odin_ii.c File Reference

#include <stdlib.h>#include <stdio.h>#include <unistd.h>#include <string.h>#include "globals.h"#include "types.h"#include "util.h"#include "netlist_utils.h"#include "arch_types.h"#include "parse_making_ast.h"#include "netlist_create_from_ast.h"#include "outputs.h"#include "netlist_optimizations.h"#include "ezxml.h"#include "read_xml_arch_file.h"#include "partial_map.h"#include "multipliers.h"#include "netlist_check.h"#include "activity_estimation.h"#include "high_level_data.h"#include "hard_blocks.h"#include "memories.h"#include "errors.h"

Include dependency graph for odin_ii.c:

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Functions | |

| void | get_options (int argc, char **argv) |

| void | do_high_level_synthesis () |

| void | do_simulation_of_netlist () |

| void | do_activation_estimation (int num_types, t_type_descriptor *type_descriptors) |

| int | main (int argc, char **argv) |

Variables | |

| global_args_t | global_args |

| int | current_parse_file |

| t_arch | Arch |

| t_type_descriptor * | type_descriptors |

| int | block_tag |

| static const char * | optString = "hHc:V:h:o:O:a:B:N:f:s:S:g:G:t:T:" |

Function Documentation

| void do_activation_estimation | ( | int | num_types, | |

| t_type_descriptor * | type_descriptors | |||

| ) |

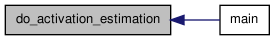

Here is the caller graph for this function:

| void do_high_level_synthesis | ( | ) |

Definition at line 230 of file odin_ii.c.

00231 { 00232 printf("--------------------------------------------------------------------\n"); 00233 printf("High-level synthesis Begin\n"); 00234 00235 /* Perform any initialization routines here */ 00236 #ifdef VPR6 00237 find_hard_multipliers(); 00238 register_hard_blocks(); 00239 #endif 00240 00241 /* parse to abstract syntax tree */ 00242 printf("Parser starting - we'll create an abstract syntax tree. Note this tree can be viewed using GraphViz (see dosumentation)\n"); 00243 parse_to_ast(); 00244 /* Note that the entry point for ast optimzations is done per module with the function void next_parsed_verilog_file(ast_node_t *file_items_list) */ 00245 00246 /* after the ast is made potentiatlly do tagging for downstream links to verilog */ 00247 if (global_args.high_level_block != NULL) 00248 { 00249 add_tag_data(); 00250 } 00251 00252 /* Now that we have a parse tree (abstract syntax tree [ast]) of the Verilog we want to make into a netlist. */ 00253 printf("Converting AST into a Netlist - Note this netlist can be viewed using GraphViz (see dosumentation)\n"); 00254 create_netlist(); 00255 00256 check_netlist(verilog_netlist); // can't levelize yet since the large muxes can look like combinational loops when they're not 00257 00258 00259 /* Report on Logical Memory usage */ 00260 report_memory_distribution(); 00261 00262 /* point for all netlist optimizations. */ 00263 printf("Performing Optimizations of the Netlist\n"); 00264 netlist_optimizations_top(verilog_netlist); 00265 00266 /* point where we convert netlist to FPGA or other hardware target compatible format */ 00267 printf("Performing Partial Map to target device\n"); 00268 partial_map_top(verilog_netlist); 00269 00270 /* check for problems in the partial mapped netlist */ 00271 printf("Check for liveness and combinational loops\n"); 00272 #ifdef VPR5 00273 levelize_and_check_for_combinational_loop_and_liveness(TRUE, verilog_netlist); 00274 #endif 00275 00276 /* point for outputs. This includes soft and hard mapping all structures to the target format. Some of these could be considred optimizations */ 00277 printf("Outputting the netlist to the specified output format\n"); 00278 output_top(verilog_netlist); 00279 00280 printf("Successful High-level synthesis by Odin\n"); 00281 printf("--------------------------------------------------------------------\n"); 00282 }

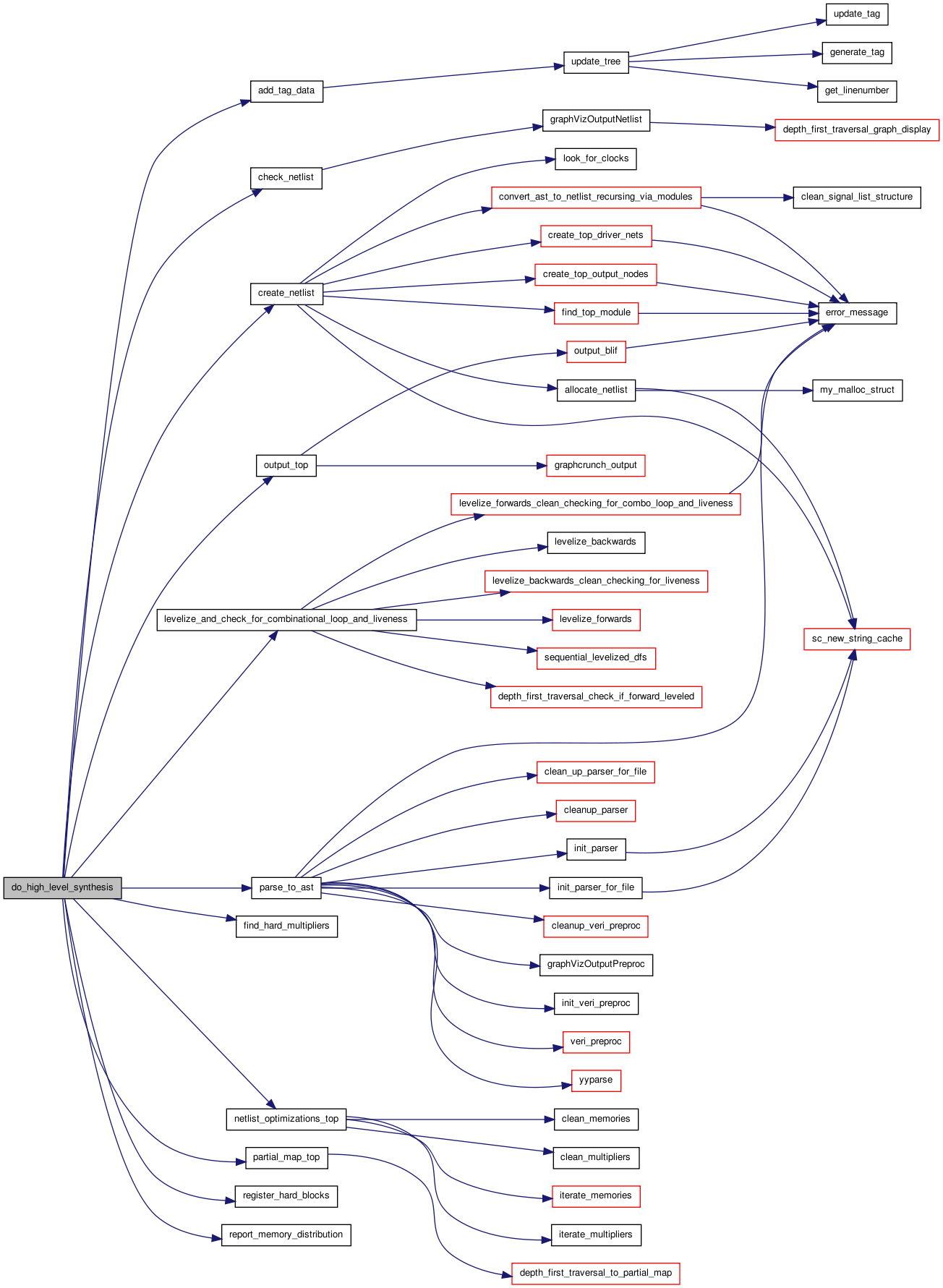

Here is the call graph for this function:

Here is the caller graph for this function:

| void do_simulation_of_netlist | ( | ) |

Definition at line 287 of file odin_ii.c.

00288 { 00289 if (global_args.sim_type == NO_SIMULATION) 00290 return; 00291 printf("Netlist Simulation Begin\n"); 00292 if (global_args.sim_type == GENERATE_VECTORS) 00293 { 00294 printf("Testing new (random) vectors.\n"); 00295 simulate_new_vectors(global_args.num_test_vectors, verilog_netlist); 00296 } 00297 else //global_args.sim_type == TEST_EXISTING_VECTORS 00298 { 00299 printf("Testing existing vectors.\n"); 00300 simulate_blif(global_args.sim_vectors_file, verilog_netlist); 00301 } 00302 printf("\n--------------------------------------------------------------------\n"); 00303 }

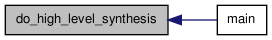

Here is the call graph for this function:

Here is the caller graph for this function:

| void get_options | ( | int | argc, | |

| char ** | argv | |||

| ) |

Definition at line 124 of file odin_ii.c.

00125 { 00126 int opt = 0; 00127 00128 /* set up the global arguments to there defualts */ 00129 global_args.config_file = NULL; 00130 global_args.verilog_file = NULL; 00131 global_args.output_file = NULL; 00132 global_args.arch_file = NULL; 00133 global_args.activation_blif_file = NULL; 00134 global_args.activation_netlist_file = NULL; 00135 global_args.high_level_block = NULL; 00136 global_args.sim_vectors_file = NULL; 00137 global_args.sim_type = NO_SIMULATION; 00138 global_args.num_test_vectors = 0; 00139 00140 /* set up the global configuration ahead of time */ 00141 configuration.list_of_file_names = NULL; 00142 configuration.num_list_of_file_names = 0; 00143 configuration.output_type = "blif"; 00144 configuration.output_ast_graphs = 0; 00145 configuration.output_netlist_graphs = 0; 00146 configuration.print_parse_tokens = 0; 00147 configuration.output_preproc_source = 0; 00148 configuration.debug_output_path = "."; 00149 configuration.arch_file = NULL; 00150 00151 /* read in the option line */ 00152 opt = getopt(argc, argv, optString); 00153 while(opt != -1) 00154 { 00155 switch(opt) 00156 { 00157 /* arch file */ 00158 case 'a': 00159 global_args.arch_file = optarg; 00160 configuration.arch_file = optarg; 00161 break; 00162 /* config file */ 00163 case 'c': 00164 global_args.config_file = optarg; 00165 break; 00166 case 'V': 00167 global_args.verilog_file = optarg; 00168 break; 00169 case 'o': 00170 case 'O': 00171 global_args.output_file = optarg; 00172 break; 00173 case 'B': 00174 global_args.activation_blif_file = optarg; 00175 break; 00176 case 'N': 00177 global_args.activation_netlist_file = optarg; 00178 break; 00179 case 'f': 00180 #ifdef VPR5 00181 global_args.high_level_block = optarg; 00182 #endif 00183 #ifdef VPR6 00184 warning_message(0, -1, 0, "VPR 6.0 doesn't have this feature yet. You'll need to deal with the output_blif.c differences wrapped by \"if (global_args.high_level_block != NULL)\"\n"); 00185 #endif 00186 break; 00187 case 'h': 00188 case 'H': 00189 printf("Usage: odin_II.exe\n\tOne of:\n\t\t-c <config_file_name.xml>\n\t\t-V <verilog_file_name.v>\n\tAlso options of:\n\t\t-o <output_path and file name>\n\t\t-a <architecture_file_in_VPR6.0_form>\n\t\t-B <blif_file_for_activation_estimation> -N <net_file_for_activation_estimation>\n\nSimulation options:\n\t\t -g <number_of_random_test_vectors\n\t\t -t test_vector_file\n"); 00190 exit(-1); 00191 break; 00192 case 'g': 00193 case 'G': 00194 global_args.num_test_vectors = atoi(optarg); 00195 global_args.sim_type = GENERATE_VECTORS; 00196 break; 00197 case 't': 00198 case 'T': 00199 global_args.sim_vectors_file = optarg; 00200 global_args.sim_type = TEST_EXISTING_VECTORS; 00201 break; 00202 case 's': 00203 case 'S': 00204 global_args.sim_vectors_file = optarg; 00205 break; 00206 default : 00207 printf("Usage: \"odin_II.exe -h\" for usage\n"); 00208 exit(-1); 00209 break; 00210 } 00211 00212 opt = getopt(argc, argv, optString); 00213 } 00214 00215 if ((global_args.config_file == NULL) && (global_args.verilog_file == NULL) && 00216 ((global_args.activation_blif_file == NULL) || (global_args.activation_netlist_file == NULL))) 00217 { 00218 printf("Error: must include either a activation blif and netlist file, a config file, or a verilog file\n"); 00219 exit(-1); 00220 } 00221 else if ((global_args.config_file != NULL) && ((global_args.verilog_file != NULL) || (global_args.activation_blif_file != NULL))) 00222 { 00223 printf("Warning: Using command line options for verilog input file!!!\n"); 00224 } 00225 }

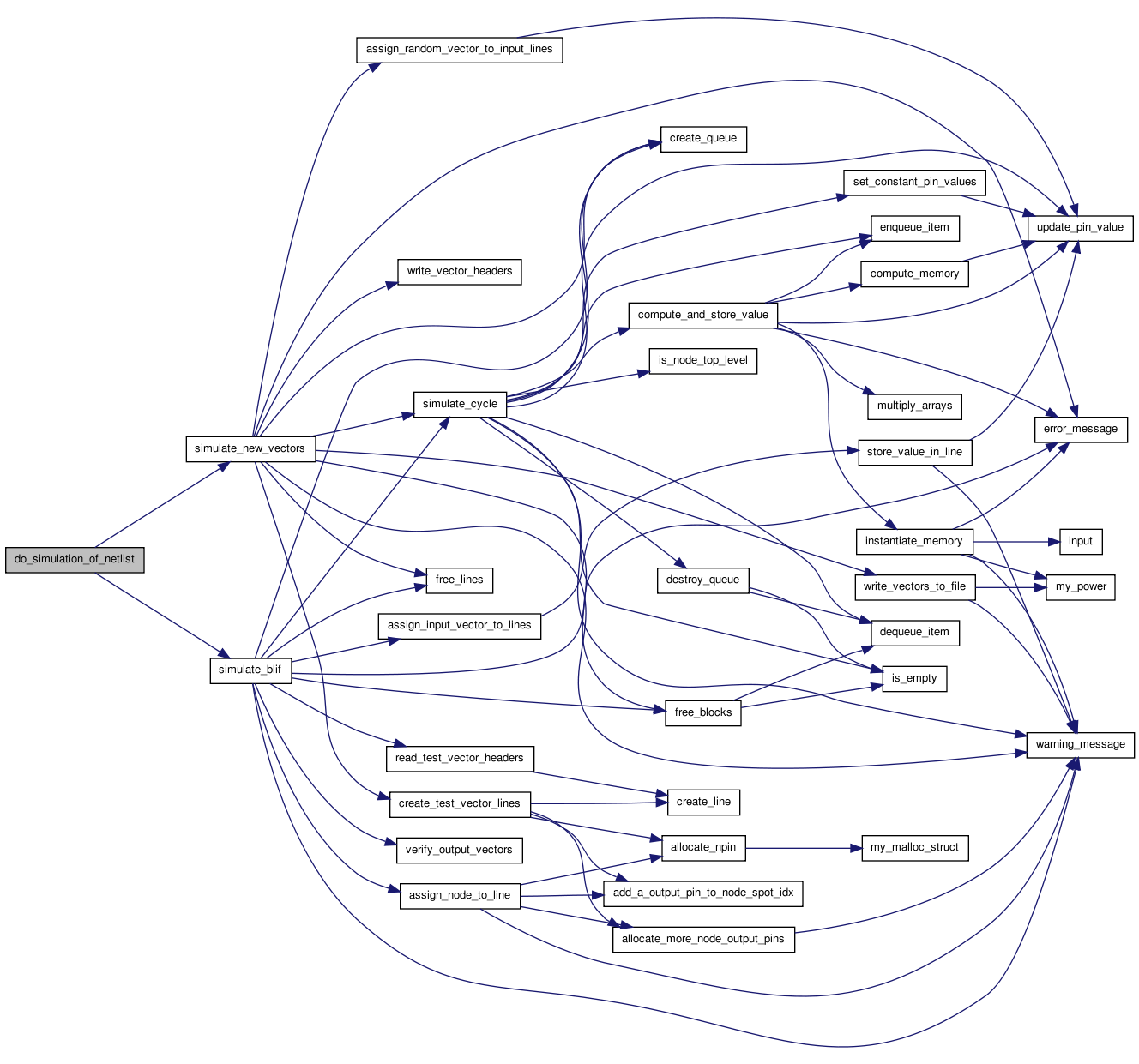

Here is the call graph for this function:

Here is the caller graph for this function:

| int main | ( | int | argc, | |

| char ** | argv | |||

| ) |

Definition at line 61 of file odin_ii.c.

00062 { 00063 int num_types; 00064 int return_val = 0; 00065 00066 printf("--------------------------------------------------------------------\n"); 00067 printf("Welcome to ODIN II version 0.1 - the better High level synthesis tools++ targetting FPGAs (mainly VPR)\n"); 00068 printf("Email: jamieson.peter@gmail.com and ken@unb.ca for support issues\n\n"); 00069 00070 /* get the command line options */ 00071 get_options(argc, argv); 00072 00073 /* read the confirguration file .. get options presets the config values just in case theyr'e not read in with config file */ 00074 if (global_args.config_file != NULL) 00075 { 00076 printf("Reading Configuration file\n"); 00077 read_config_file(global_args.config_file); 00078 } 00079 00080 /* read the FPGA architecture file */ 00081 if (global_args.arch_file != NULL) 00082 { 00083 printf("Reading FPGA Architecture file\n"); 00084 #ifdef VPR5 00085 t_clocks ClockDetails = { 0 }; 00086 t_power PowerDetails = { 0 }; 00087 XmlReadArch(global_args.arch_file, (boolean)FALSE, &Arch, &type_descriptors, &num_types, &ClockDetails, &PowerDetails); 00088 #endif 00089 #ifdef VPR6 00090 XmlReadArch(global_args.arch_file, (boolean)FALSE, &Arch, &type_descriptors, &num_types); 00091 #endif 00092 } 00093 00094 if (global_args.activation_blif_file != NULL && global_args.activation_netlist_file != NULL) 00095 { 00096 #ifdef VPR5 00097 do_activation_estimation(num_types, type_descriptors); 00098 #endif 00099 return_val = 1; 00100 } 00101 else 00102 { 00103 /* High level synthesis tool */ 00104 do_high_level_synthesis(); 00105 00106 /* Simulate blif netlist */ 00107 do_simulation_of_netlist(); 00108 } 00109 00110 /* activation estimation tool */ 00111 00112 #ifdef VPR6 00113 report_mult_distribution(); 00114 deregister_hard_blocks(); 00115 #endif 00116 00117 return 0; 00118 }

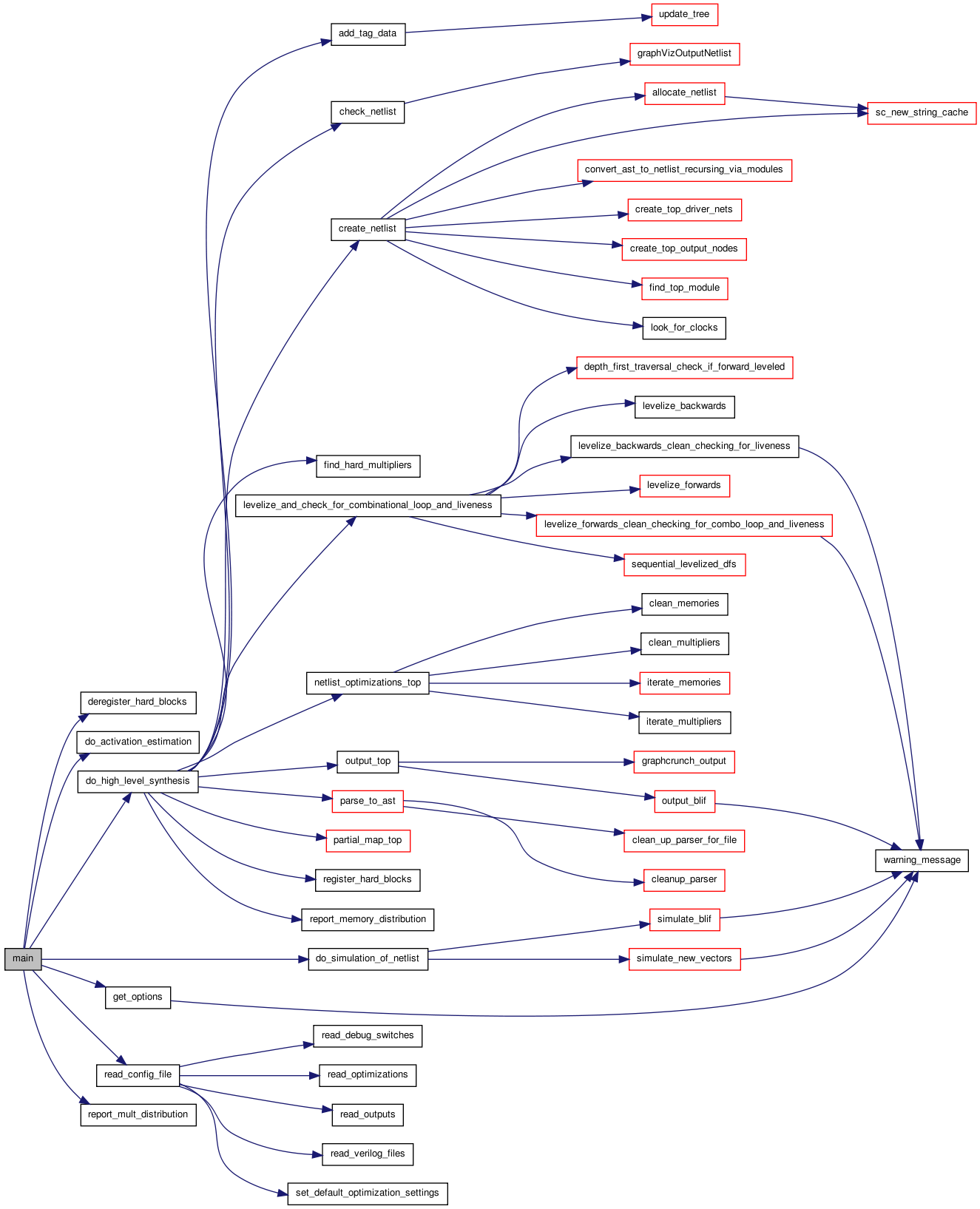

Here is the call graph for this function:

Variable Documentation

const char* optString = "hHc:V:h:o:O:a:B:N:f:s:S:g:G:t:T:" [static] |

| t_type_descriptor* type_descriptors |

1.6.3

1.6.3