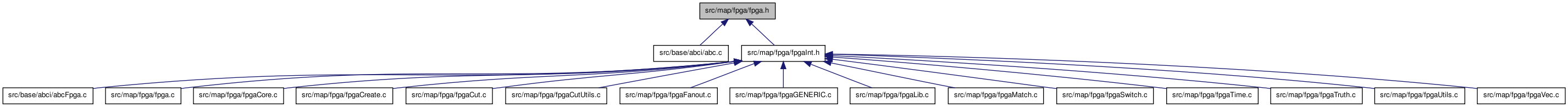

src/map/fpga/fpga.h File Reference

Go to the source code of this file.

Define Documentation

| #define Fpga_IsComplement | ( | p | ) | (((int)((unsigned long) (p) & 01))) |

| #define FPGA_MAX_LUTSIZE 32 |

CFile****************************************************************

FileName [fpga.h]

PackageName [MVSIS 2.0: Multi-valued logic synthesis system.]

Synopsis [Technology mapping for variable-size-LUT FPGAs.]

Author [MVSIS Group]

Affiliation [UC Berkeley]

Date [Ver. 2.0. Started - August 18, 2004.]

Revision [

- Id

- fpga.h,v 1.7 2004/09/30 21:18:09 satrajit Exp

] INCLUDES /// PARAMETERS ///

| #define Fpga_Not | ( | p | ) | ((Fpga_Node_t *)((unsigned long)(p) ^ 01)) |

| #define Fpga_NotCond | ( | p, | |||

| c | ) | ((Fpga_Node_t *)((unsigned long)(p) ^ (c))) |

| #define Fpga_Regular | ( | p | ) | ((Fpga_Node_t *)((unsigned long)(p) & ~01)) |

Typedef Documentation

| typedef struct Fpga_CutStruct_t_ Fpga_Cut_t |

| typedef struct Fpga_LutLibStruct_t_ Fpga_LutLib_t |

| typedef struct Fpga_ManStruct_t_ Fpga_Man_t |

| typedef struct Fpga_NodeStruct_t_ Fpga_Node_t |

| typedef struct Fpga_NodeVecStruct_t_ Fpga_NodeVec_t |

Function Documentation

| Fpga_NodeVec_t* Fpga_CollectNodeTfo | ( | Fpga_Man_t * | pMan, | |

| Fpga_Node_t * | pNode | |||

| ) |

Function*************************************************************

Synopsis [Collects the TFO of the node.]

Description []

SideEffects []

SeeAlso []

Definition at line 673 of file fpgaUtils.c.

00674 { 00675 Fpga_NodeVec_t * vVisited, * vTfo; 00676 int i; 00677 // perform the traversal 00678 vVisited = Fpga_NodeVecAlloc( 100 ); 00679 vTfo = Fpga_NodeVecAlloc( 100 ); 00680 for ( i = 0; i < pMan->nOutputs; i++ ) 00681 Fpga_CollectNodeTfo_rec( Fpga_Regular(pMan->pOutputs[i]), pNode, vVisited, vTfo ); 00682 for ( i = 0; i < vVisited->nSize; i++ ) 00683 vVisited->pArray[i]->fMark0 = vVisited->pArray[i]->fMark1 = 0; 00684 Fpga_NodeVecFree( vVisited ); 00685 return vTfo; 00686 }

| void Fpga_CutCreateFromNode | ( | Fpga_Man_t * | p, | |

| int | iRoot, | |||

| int * | pLeaves, | |||

| int | nLeaves | |||

| ) |

| Fpga_Node_t** Fpga_CutReadLeaves | ( | Fpga_Cut_t * | p | ) |

Definition at line 141 of file fpgaCreate.c.

00141 { return p->ppLeaves; }

| int Fpga_CutReadLeavesNum | ( | Fpga_Cut_t * | p | ) |

Function*************************************************************

Synopsis [Reads parameters from the cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 140 of file fpgaCreate.c.

00140 { return p->nLeaves; }

| void Fpga_CutsCleanSign | ( | Fpga_Man_t * | pMan | ) |

Function*************************************************************

Synopsis [Clean the signatures.]

Description []

SideEffects []

SeeAlso []

Definition at line 794 of file fpgaCut.c.

00795 { 00796 Fpga_Node_t * pNode; 00797 Fpga_Cut_t * pCut; 00798 int i; 00799 for ( i = 0; i < pMan->nBins; i++ ) 00800 for ( pNode = pMan->pBins[i]; pNode; pNode = pNode->pNext ) 00801 for ( pCut = pNode->pCuts; pCut; pCut = pCut->pNext ) 00802 pCut->uSign = 0; 00803 }

| int Fpga_CutVolume | ( | Fpga_Cut_t * | pCut | ) |

Function*************************************************************

Synopsis [Derives the truth table for one cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 137 of file fpgaTruth.c.

00138 { 00139 Fpga_NodeVec_t * vVisited; 00140 int Volume, i; 00141 assert( pCut->nLeaves > 1 ); 00142 // set the leaf variables 00143 for ( i = 0; i < pCut->nLeaves; i++ ) 00144 pCut->ppLeaves[i]->pCuts->fMark = 1; 00145 // recursively compute the function 00146 vVisited = Fpga_NodeVecAlloc( 10 ); 00147 Fpga_CutVolume_rec( pCut, vVisited ); 00148 // clean the marks 00149 for ( i = 0; i < pCut->nLeaves; i++ ) 00150 pCut->ppLeaves[i]->pCuts->fMark = 0; 00151 for ( i = 0; i < vVisited->nSize; i++ ) 00152 { 00153 pCut = (Fpga_Cut_t *)vVisited->pArray[i]; 00154 pCut->fMark = 0; 00155 } 00156 Volume = vVisited->nSize; 00157 printf( "%d ", Volume ); 00158 Fpga_NodeVecFree( vVisited ); 00159 return Volume; 00160 }

| int Fpga_LibReadLutMax | ( | Fpga_LutLib_t * | pLib | ) |

Function*************************************************************

Synopsis [Reads the parameters of the LUT library.]

Description []

SideEffects []

SeeAlso []

Definition at line 85 of file fpgaCreate.c.

00085 { return pLib->LutMax; }

| Fpga_LutLib_t* Fpga_LutLibDup | ( | Fpga_LutLib_t * | p | ) |

Function*************************************************************

Synopsis [Duplicates the LUT library.]

Description []

SideEffects []

SeeAlso []

Definition at line 161 of file fpgaLib.c.

00162 { 00163 Fpga_LutLib_t * pNew; 00164 pNew = ALLOC( Fpga_LutLib_t, 1 ); 00165 *pNew = *p; 00166 pNew->pName = Extra_UtilStrsav( pNew->pName ); 00167 return pNew; 00168 }

| float Fpga_LutLibReadLutArea | ( | Fpga_LutLib_t * | p, | |

| int | Size | |||

| ) |

| float* Fpga_LutLibReadLutAreas | ( | Fpga_LutLib_t * | p | ) |

| float Fpga_LutLibReadLutDelay | ( | Fpga_LutLib_t * | p, | |

| int | Size | |||

| ) |

| float* Fpga_LutLibReadLutDelays | ( | Fpga_LutLib_t * | p | ) |

| int Fpga_LutLibReadVarMax | ( | Fpga_LutLib_t * | p | ) |

CFile****************************************************************

FileName [fpgaLib.c]

PackageName [MVSIS 1.3: Multi-valued logic synthesis system.]

Synopsis [Technology mapping for variable-size-LUT FPGAs.]

Author [MVSIS Group]

Affiliation [UC Berkeley]

Date [Ver. 2.0. Started - August 18, 2004.]

Revision [

- Id

- fpgaLib.c,v 1.4 2005/01/23 06:59:41 alanmi Exp

] DECLARATIONS /// FUNCTION DEFINITIONS ///Function*************************************************************

Synopsis [APIs to access LUT library.]

Description []

SideEffects []

SeeAlso []

Definition at line 40 of file fpgaLib.c.

00040 { return p->LutMax; }

| int Fpga_ManCheckConsistency | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis [Verify one useful property.]

Description [This procedure verifies one useful property. After the FRAIG construction with choice nodes is over, each primary node should have fanins that are primary nodes. The primary nodes is the one that does not have pNode->pRepr set to point to another node.]

SideEffects []

SeeAlso []

Definition at line 498 of file fpgaUtils.c.

00499 { 00500 Fpga_Node_t * pNode; 00501 Fpga_NodeVec_t * pVec; 00502 int i; 00503 pVec = Fpga_MappingDfs( p, 0 ); 00504 for ( i = 0; i < pVec->nSize; i++ ) 00505 { 00506 pNode = pVec->pArray[i]; 00507 if ( Fpga_NodeIsVar(pNode) ) 00508 { 00509 if ( pNode->pRepr ) 00510 printf( "Primary input %d is a secondary node.\n", pNode->Num ); 00511 } 00512 else if ( Fpga_NodeIsConst(pNode) ) 00513 { 00514 if ( pNode->pRepr ) 00515 printf( "Constant 1 %d is a secondary node.\n", pNode->Num ); 00516 } 00517 else 00518 { 00519 if ( pNode->pRepr ) 00520 printf( "Internal node %d is a secondary node.\n", pNode->Num ); 00521 if ( Fpga_Regular(pNode->p1)->pRepr ) 00522 printf( "Internal node %d has first fanin that is a secondary node.\n", pNode->Num ); 00523 if ( Fpga_Regular(pNode->p2)->pRepr ) 00524 printf( "Internal node %d has second fanin that is a secondary node.\n", pNode->Num ); 00525 } 00526 } 00527 Fpga_NodeVecFree( pVec ); 00528 return 1; 00529 }

| void Fpga_ManCleanData0 | ( | Fpga_Man_t * | pMan | ) |

Function*************************************************************

Synopsis [Computes the limited DFS ordering for one node.]

Description []

SideEffects []

SeeAlso []

Definition at line 655 of file fpgaUtils.c.

| Fpga_Man_t* Fpga_ManCreate | ( | int | nInputs, | |

| int | nOutputs, | |||

| int | fVerbose | |||

| ) |

FUNCTION DEFINITIONS ///

Function*************************************************************

Synopsis [Create the mapping manager.]

Description [The number of inputs and outputs is assumed to be known is advance. It is much simpler to have them fixed upfront. When it comes to representing the object graph in the form of AIG, the resulting manager is similar to the regular AIG manager, except that it does not use reference counting (and therefore does not have garbage collections). It does have table resizing. The data structure is more flexible to represent additional information needed for mapping.]

SideEffects []

SeeAlso []

Definition at line 162 of file fpgaCreate.c.

00163 { 00164 Fpga_Man_t * p; 00165 int i; 00166 00167 // start the manager 00168 p = ALLOC( Fpga_Man_t, 1 ); 00169 memset( p, 0, sizeof(Fpga_Man_t) ); 00170 p->pLutLib = Abc_FrameReadLibLut(); 00171 p->nVarsMax = p->pLutLib->LutMax; 00172 p->fVerbose = fVerbose; 00173 p->fAreaRecovery = 1; 00174 p->fEpsilon = (float)0.001; 00175 00176 Fpga_TableCreate( p ); 00177 //if ( p->fVerbose ) 00178 // printf( "Node = %d (%d) bytes. Cut = %d bytes.\n", sizeof(Fpga_Node_t), FPGA_NUM_BYTES(sizeof(Fpga_Node_t)), sizeof(Fpga_Cut_t) ); 00179 p->mmNodes = Extra_MmFixedStart( FPGA_NUM_BYTES(sizeof(Fpga_Node_t)) ); 00180 p->mmCuts = Extra_MmFixedStart( sizeof(Fpga_Cut_t) ); 00181 00182 assert( p->nVarsMax > 0 ); 00183 // Fpga_MappingSetupTruthTables( p->uTruths ); 00184 00185 // make sure the constant node will get index -1 00186 p->nNodes = -1; 00187 // create the constant node 00188 p->pConst1 = Fpga_NodeCreate( p, NULL, NULL ); 00189 p->vNodesAll = Fpga_NodeVecAlloc( 1000 ); 00190 p->vMapping = Fpga_NodeVecAlloc( 1000 ); 00191 00192 // create the PI nodes 00193 p->nInputs = nInputs; 00194 p->pInputs = ALLOC( Fpga_Node_t *, nInputs ); 00195 for ( i = 0; i < nInputs; i++ ) 00196 p->pInputs[i] = Fpga_NodeCreate( p, NULL, NULL ); 00197 00198 // create the place for the output nodes 00199 p->nOutputs = nOutputs; 00200 p->pOutputs = ALLOC( Fpga_Node_t *, nOutputs ); 00201 memset( p->pOutputs, 0, sizeof(Fpga_Node_t *) * nOutputs ); 00202 return p; 00203 }

| void Fpga_ManFree | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis [Deallocates the mapping manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 216 of file fpgaCreate.c.

00217 { 00218 // Fpga_ManStats( p ); 00219 // int i; 00220 // for ( i = 0; i < p->vNodesAll->nSize; i++ ) 00221 // Fpga_NodeVecFree( p->vNodesAll->pArray[i]->vFanouts ); 00222 // Fpga_NodeVecFree( p->pConst1->vFanouts ); 00223 if ( p->vMapping ) 00224 Fpga_NodeVecFree( p->vMapping ); 00225 if ( p->vAnds ) 00226 Fpga_NodeVecFree( p->vAnds ); 00227 if ( p->vNodesAll ) 00228 Fpga_NodeVecFree( p->vNodesAll ); 00229 Extra_MmFixedStop( p->mmNodes ); 00230 Extra_MmFixedStop( p->mmCuts ); 00231 FREE( p->ppOutputNames ); 00232 FREE( p->pInputArrivals ); 00233 FREE( p->pInputs ); 00234 FREE( p->pOutputs ); 00235 FREE( p->pBins ); 00236 FREE( p ); 00237 }

| void Fpga_ManPrintTimeStats | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis [Prints runtime statistics of the mapping manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 251 of file fpgaCreate.c.

00252 { 00253 extern char * pNetName; 00254 extern int TotalLuts; 00255 // FILE * pTable; 00256 00257 00258 /* 00259 pTable = fopen( "stats.txt", "a+" ); 00260 fprintf( pTable, "%s ", pNetName ); 00261 fprintf( pTable, "%.0f ", p->fRequiredGlo ); 00262 // fprintf( pTable, "%.0f ", p->fAreaGlo );//+ (float)nOutputInvs ); 00263 fprintf( pTable, "%.0f ", (float)TotalLuts ); 00264 fprintf( pTable, "%4.2f\n", (float)(p->timeTotal-p->timeToMap)/(float)(CLOCKS_PER_SEC) ); 00265 fclose( pTable ); 00266 */ 00267 00268 // printf( "N-canonical = %d. Matchings = %d. ", p->nCanons, p->nMatches ); 00269 // printf( "Choice nodes = %d. Choices = %d.\n", p->nChoiceNodes, p->nChoices ); 00270 PRT( "ToMap", p->timeToMap ); 00271 PRT( "Cuts ", p->timeCuts ); 00272 PRT( "Match", p->timeMatch ); 00273 PRT( "Area ", p->timeRecover ); 00274 PRT( "ToNet", p->timeToNet ); 00275 PRT( "TOTAL", p->timeTotal ); 00276 if ( p->time1 ) { PRT( "time1", p->time1 ); } 00277 if ( p->time2 ) { PRT( "time2", p->time2 ); } 00278 }

| Fpga_Node_t* Fpga_ManReadConst1 | ( | Fpga_Man_t * | p | ) |

Definition at line 52 of file fpgaCreate.c.

00052 { return p->pConst1; }

| int Fpga_ManReadFanoutViolations | ( | Fpga_Man_t * | p | ) |

| float* Fpga_ManReadInputArrivals | ( | Fpga_Man_t * | p | ) |

Definition at line 53 of file fpgaCreate.c.

00053 { return p->pInputArrivals;}

| int Fpga_ManReadInputNum | ( | Fpga_Man_t * | p | ) |

FUNCTION DEFINITIONS ///Function*************************************************************

Synopsis [Reads parameters of the mapping manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 48 of file fpgaCreate.c.

00048 { return p->nInputs; }

| Fpga_Node_t** Fpga_ManReadInputs | ( | Fpga_Man_t * | p | ) |

Definition at line 50 of file fpgaCreate.c.

00050 { return p->pInputs; }

| float* Fpga_ManReadLutAreas | ( | Fpga_Man_t * | p | ) |

Definition at line 55 of file fpgaCreate.c.

| int Fpga_ManReadOutputNum | ( | Fpga_Man_t * | p | ) |

Definition at line 49 of file fpgaCreate.c.

00049 { return p->nOutputs; }

| Fpga_Node_t** Fpga_ManReadOutputs | ( | Fpga_Man_t * | p | ) |

Definition at line 51 of file fpgaCreate.c.

00051 { return p->pOutputs; }

| int Fpga_ManReadVerbose | ( | Fpga_Man_t * | p | ) |

Definition at line 54 of file fpgaCreate.c.

00054 { return p->fVerbose; }

| void Fpga_ManSetAreaLimit | ( | Fpga_Man_t * | p, | |

| float | AreaLimit | |||

| ) |

Definition at line 63 of file fpgaCreate.c.

00063 { p->AreaLimit = AreaLimit; }

| void Fpga_ManSetAreaRecovery | ( | Fpga_Man_t * | p, | |

| int | fAreaRecovery | |||

| ) |

Definition at line 61 of file fpgaCreate.c.

00061 { p->fAreaRecovery = fAreaRecovery;}

| void Fpga_ManSetChoiceNodeNum | ( | Fpga_Man_t * | p, | |

| int | nChoiceNodes | |||

| ) |

Definition at line 65 of file fpgaCreate.c.

00065 { p->nChoiceNodes = nChoiceNodes; }

| void Fpga_ManSetChoiceNum | ( | Fpga_Man_t * | p, | |

| int | nChoices | |||

| ) |

Definition at line 66 of file fpgaCreate.c.

00066 { p->nChoices = nChoices; }

| void Fpga_ManSetDelayLimit | ( | Fpga_Man_t * | p, | |

| float | DelayLimit | |||

| ) |

Definition at line 62 of file fpgaCreate.c.

00062 { p->DelayLimit = DelayLimit; }

| void Fpga_ManSetDelayTarget | ( | Fpga_Man_t * | p, | |

| float | DelayTarget | |||

| ) |

Definition at line 71 of file fpgaCreate.c.

00071 { p->DelayTarget = DelayTarget; }

| void Fpga_ManSetFanoutViolations | ( | Fpga_Man_t * | p, | |

| int | nVio | |||

| ) |

| void Fpga_ManSetInputArrivals | ( | Fpga_Man_t * | p, | |

| float * | pArrivals | |||

| ) |

Definition at line 60 of file fpgaCreate.c.

00060 { p->pInputArrivals = pArrivals; }

| void Fpga_ManSetLatchNum | ( | Fpga_Man_t * | p, | |

| int | nLatches | |||

| ) |

Definition at line 70 of file fpgaCreate.c.

00070 { p->nLatches = nLatches; }

| void Fpga_ManSetLatchPaths | ( | Fpga_Man_t * | p, | |

| int | fLatchPaths | |||

| ) |

Definition at line 69 of file fpgaCreate.c.

00069 { p->fLatchPaths = fLatchPaths; }

| void Fpga_ManSetName | ( | Fpga_Man_t * | p, | |

| char * | pFileName | |||

| ) |

Definition at line 72 of file fpgaCreate.c.

00072 { p->pFileName = pFileName; }

| void Fpga_ManSetNumIterations | ( | Fpga_Man_t * | p, | |

| int | nNumIterations | |||

| ) |

| void Fpga_ManSetObeyFanoutLimits | ( | Fpga_Man_t * | p, | |

| int | fObeyFanoutLimits | |||

| ) |

| void Fpga_ManSetOutputNames | ( | Fpga_Man_t * | p, | |

| char ** | ppNames | |||

| ) |

Definition at line 59 of file fpgaCreate.c.

00059 { p->ppOutputNames = ppNames; }

| void Fpga_ManSetSwitching | ( | Fpga_Man_t * | p, | |

| int | fSwitching | |||

| ) |

Definition at line 68 of file fpgaCreate.c.

00068 { p->fSwitching = fSwitching; }

| void Fpga_ManSetTimeLimit | ( | Fpga_Man_t * | p, | |

| float | TimeLimit | |||

| ) |

Definition at line 64 of file fpgaCreate.c.

00064 { p->TimeLimit = TimeLimit; }

| void Fpga_ManSetTimeToMap | ( | Fpga_Man_t * | p, | |

| int | Time | |||

| ) |

Definition at line 56 of file fpgaCreate.c.

00056 { p->timeToMap = Time; }

| void Fpga_ManSetTimeToNet | ( | Fpga_Man_t * | p, | |

| int | Time | |||

| ) |

Definition at line 57 of file fpgaCreate.c.

00057 { p->timeToNet = Time; }

| void Fpga_ManSetTimeTotal | ( | Fpga_Man_t * | p, | |

| int | Time | |||

| ) |

Definition at line 58 of file fpgaCreate.c.

00058 { p->timeTotal = Time; }

| void Fpga_ManSetVerbose | ( | Fpga_Man_t * | p, | |

| int | fVerbose | |||

| ) |

Definition at line 67 of file fpgaCreate.c.

00067 { p->fVerbose = fVerbose; }

| void Fpga_ManStats | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis [Prints some interesting stats.]

Description []

SideEffects []

SeeAlso []

Definition at line 562 of file fpgaCreate.c.

00563 { 00564 FILE * pTable; 00565 pTable = fopen( "stats.txt", "a+" ); 00566 fprintf( pTable, "%s ", p->pFileName ); 00567 fprintf( pTable, "%4d ", p->nInputs - p->nLatches ); 00568 fprintf( pTable, "%4d ", p->nOutputs - p->nLatches ); 00569 fprintf( pTable, "%4d ", p->nLatches ); 00570 fprintf( pTable, "%7d ", p->vAnds->nSize ); 00571 fprintf( pTable, "%7d ", Fpga_CutCountAll(p) ); 00572 fprintf( pTable, "%2d\n", (int)p->fRequiredGlo ); 00573 fclose( pTable ); 00574 }

| int Fpga_Mapping | ( | Fpga_Man_t * | p | ) |

FUNCTION DEFINITIONS ///Function*************************************************************

Synopsis [Performs technology mapping for the given object graph.]

Description [The object graph is stored in the mapping manager. First, all the AND-nodes, which fanout into the POs, are collected in the DFS fashion. Next, three steps are performed: the k-feasible cuts are computed for each node, the truth tables are computed for each cut, and the delay-optimal matches are assigned for each node.]

SideEffects []

SeeAlso []

Definition at line 50 of file fpgaCore.c.

00051 { 00052 int clk, clkTotal = clock(); 00053 00054 // collect the nodes reachable from POs in the DFS order (including the choices) 00055 p->vAnds = Fpga_MappingDfs( p, 1 ); 00056 Fpga_ManReportChoices( p ); // recomputes levels 00057 Fpga_MappingSetChoiceLevels( p ); 00058 00059 // compute the cuts of nodes in the DFS order 00060 clk = clock(); 00061 Fpga_MappingCuts( p ); 00062 p->timeCuts = clock() - clk; 00063 00064 // match the truth tables to the supergates 00065 clk = clock(); 00066 if ( !Fpga_MappingMatches( p, 1 ) ) 00067 return 0; 00068 p->timeMatch = clock() - clk; 00069 00070 // perform area recovery 00071 clk = clock(); 00072 if ( !Fpga_MappingPostProcess( p ) ) 00073 return 0; 00074 p->timeRecover = clock() - clk; 00075 //PRT( "Total mapping time", clock() - clkTotal ); 00076 00077 s_MappingTime = clock() - clkTotal; 00078 s_MappingMem = Fpga_CutCountAll(p) * (sizeof(Fpga_Cut_t) - sizeof(int) * (FPGA_MAX_LEAVES - p->nVarsMax)); 00079 00080 // print the AI-graph used for mapping 00081 //Fpga_ManShow( p, "test" ); 00082 // if ( p->fVerbose ) 00083 // Fpga_MappingPrintOutputArrivals( p ); 00084 if ( p->fVerbose ) 00085 { 00086 PRT( "Total time", clock() - clkTotal ); 00087 } 00088 return 1; 00089 }

| void Fpga_MappingCreatePiCuts | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis [Performs technology mapping for variable-size-LUTs.]

Description []

SideEffects []

SeeAlso []

Definition at line 178 of file fpgaCut.c.

00179 { 00180 Fpga_Cut_t * pCut; 00181 int i; 00182 00183 // set the elementary cuts for the PI variables 00184 for ( i = 0; i < p->nInputs; i++ ) 00185 { 00186 pCut = Fpga_CutAlloc( p ); 00187 pCut->nLeaves = 1; 00188 pCut->ppLeaves[0] = p->pInputs[i]; 00189 pCut->uSign = (1 << (i%31)); 00190 p->pInputs[i]->pCuts = pCut; 00191 p->pInputs[i]->pCutBest = pCut; 00192 // set the input arrival times 00193 // p->pInputs[i]->pCut[1]->tArrival = p->pInputArrivals[i]; 00194 } 00195 }

| void Fpga_MappingSetUsedCuts | ( | Fpga_Man_t * | pMan | ) |

Function*************************************************************

Synopsis [Sets the used cuts to be the currently selected ones.]

Description []

SideEffects []

SeeAlso []

Definition at line 455 of file fpgaCutUtils.c.

| Fpga_Node_t* Fpga_NodeAnd | ( | Fpga_Man_t * | p, | |

| Fpga_Node_t * | p1, | |||

| Fpga_Node_t * | p2 | |||

| ) |

Function*************************************************************

Synopsis [Elementary AND operation on the AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 468 of file fpgaCreate.c.

00469 { 00470 Fpga_Node_t * pNode; 00471 pNode = Fpga_TableLookup( p, p1, p2 ); 00472 return pNode; 00473 }

| int Fpga_NodeComparePhase | ( | Fpga_Node_t * | p1, | |

| Fpga_Node_t * | p2 | |||

| ) |

Definition at line 127 of file fpgaCreate.c.

00127 { assert( !Fpga_IsComplement(p1) ); assert( !Fpga_IsComplement(p2) ); return p1->fInv ^ p2->fInv; }

| Fpga_Node_t* Fpga_NodeCreate | ( | Fpga_Man_t * | p, | |

| Fpga_Node_t * | p1, | |||

| Fpga_Node_t * | p2 | |||

| ) |

Function*************************************************************

Synopsis [Creates a new node.]

Description [This procedure should be called to create the constant node and the PI nodes first.]

SideEffects []

SeeAlso []

Definition at line 292 of file fpgaCreate.c.

00293 { 00294 Fpga_Node_t * pNode; 00295 // create the node 00296 pNode = (Fpga_Node_t *)Extra_MmFixedEntryFetch( p->mmNodes ); 00297 memset( pNode, 0, sizeof(Fpga_Node_t) ); 00298 // set very large required time 00299 pNode->tRequired = FPGA_FLOAT_LARGE; 00300 pNode->aEstFanouts = -1; 00301 pNode->p1 = p1; 00302 pNode->p2 = p2; 00303 // set the number of this node 00304 pNode->Num = p->nNodes++; 00305 // place to store the fanouts 00306 // pNode->vFanouts = Fpga_NodeVecAlloc( 5 ); 00307 // store this node in the internal array 00308 if ( pNode->Num >= 0 ) 00309 Fpga_NodeVecPush( p->vNodesAll, pNode ); 00310 else 00311 pNode->fInv = 1; 00312 // set the level of this node 00313 if ( p1 ) 00314 { 00315 #ifdef FPGA_ALLOCATE_FANOUT 00316 // create the fanout info 00317 Fpga_NodeAddFaninFanout( Fpga_Regular(p1), pNode ); 00318 Fpga_NodeAddFaninFanout( Fpga_Regular(p2), pNode ); 00319 #endif 00320 // compute the level 00321 pNode->Level = 1 + FPGA_MAX(Fpga_Regular(p1)->Level, Fpga_Regular(p2)->Level); 00322 pNode->fInv = Fpga_NodeIsSimComplement(p1) & Fpga_NodeIsSimComplement(p2); 00323 } 00324 // reference the inputs 00325 if ( p1 ) Fpga_NodeRef(p1); 00326 if ( p2 ) Fpga_NodeRef(p2); 00327 return pNode; 00328 }

| Fpga_Node_t* Fpga_NodeExor | ( | Fpga_Man_t * | p, | |

| Fpga_Node_t * | p1, | |||

| Fpga_Node_t * | p2 | |||

| ) |

Function*************************************************************

Synopsis [Elementary EXOR operation on the AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 504 of file fpgaCreate.c.

00505 { 00506 return Fpga_NodeMux( p, p1, Fpga_Not(p2), p2 ); 00507 }

| int Fpga_NodeIsAnd | ( | Fpga_Node_t * | p | ) |

Definition at line 126 of file fpgaCreate.c.

00126 { return (Fpga_Regular(p))->p1 != NULL; }

| int Fpga_NodeIsConst | ( | Fpga_Node_t * | p | ) |

Function*************************************************************

Synopsis [Checks the type of the node.]

Description []

SideEffects []

SeeAlso []

Definition at line 124 of file fpgaCreate.c.

00124 { return (Fpga_Regular(p))->Num == -1; }

| int Fpga_NodeIsVar | ( | Fpga_Node_t * | p | ) |

Definition at line 125 of file fpgaCreate.c.

00125 { return (Fpga_Regular(p))->p1 == NULL && (Fpga_Regular(p))->Num >= 0; }

| Fpga_Node_t* Fpga_NodeMux | ( | Fpga_Man_t * | p, | |

| Fpga_Node_t * | pC, | |||

| Fpga_Node_t * | pT, | |||

| Fpga_Node_t * | pE | |||

| ) |

Function*************************************************************

Synopsis [Elementary MUX operation on the AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 520 of file fpgaCreate.c.

00521 { 00522 Fpga_Node_t * pAnd1, * pAnd2, * pRes; 00523 pAnd1 = Fpga_TableLookup( p, pC, pT ); 00524 pAnd2 = Fpga_TableLookup( p, Fpga_Not(pC), pE ); 00525 pRes = Fpga_NodeOr( p, pAnd1, pAnd2 ); 00526 return pRes; 00527 }

| Fpga_Node_t* Fpga_NodeOr | ( | Fpga_Man_t * | p, | |

| Fpga_Node_t * | p1, | |||

| Fpga_Node_t * | p2 | |||

| ) |

Function*************************************************************

Synopsis [Elementary OR operation on the AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 486 of file fpgaCreate.c.

00487 { 00488 Fpga_Node_t * pNode; 00489 pNode = Fpga_Not( Fpga_TableLookup( p, Fpga_Not(p1), Fpga_Not(p2) ) ); 00490 return pNode; 00491 }

| Fpga_Cut_t* Fpga_NodeReadCutBest | ( | Fpga_Node_t * | p | ) |

Definition at line 104 of file fpgaCreate.c.

00104 { return p->pCutBest; }

| Fpga_Cut_t* Fpga_NodeReadCuts | ( | Fpga_Node_t * | p | ) |

Definition at line 103 of file fpgaCreate.c.

00103 { return p->pCuts; }

| char* Fpga_NodeReadData0 | ( | Fpga_Node_t * | p | ) |

Function*************************************************************

Synopsis [Reads parameters of the mapping node.]

Description []

SideEffects []

SeeAlso []

Definition at line 98 of file fpgaCreate.c.

00098 { return p->pData0; }

| Fpga_Node_t* Fpga_NodeReadData1 | ( | Fpga_Node_t * | p | ) |

Definition at line 99 of file fpgaCreate.c.

00099 { return p->pLevel; }

| int Fpga_NodeReadLevel | ( | Fpga_Node_t * | p | ) |

Definition at line 102 of file fpgaCreate.c.

00102 { return Fpga_Regular(p)->Level; }

| int Fpga_NodeReadNum | ( | Fpga_Node_t * | p | ) |

Definition at line 101 of file fpgaCreate.c.

00101 { return p->Num; }

| Fpga_Node_t* Fpga_NodeReadOne | ( | Fpga_Node_t * | p | ) |

Definition at line 105 of file fpgaCreate.c.

00105 { return p->p1; }

| int Fpga_NodeReadRefs | ( | Fpga_Node_t * | p | ) |

Definition at line 100 of file fpgaCreate.c.

00100 { return p->nRefs; }

| Fpga_Node_t* Fpga_NodeReadTwo | ( | Fpga_Node_t * | p | ) |

Definition at line 106 of file fpgaCreate.c.

00106 { return p->p2; }

| void Fpga_NodeSetArrival | ( | Fpga_Node_t * | p, | |

| float | Time | |||

| ) |

| void Fpga_NodeSetChoice | ( | Fpga_Man_t * | pMan, | |

| Fpga_Node_t * | pNodeOld, | |||

| Fpga_Node_t * | pNodeNew | |||

| ) |

Function*************************************************************

Synopsis [Sets the node to be equivalent to the given one.]

Description [This procedure is a work-around for the equivalence check. Does not verify the equivalence. Use at the user's risk.]

SideEffects []

SeeAlso []

Definition at line 542 of file fpgaCreate.c.

| void Fpga_NodeSetData0 | ( | Fpga_Node_t * | p, | |

| char * | pData | |||

| ) |

Definition at line 107 of file fpgaCreate.c.

00107 { p->pData0 = pData; }

| void Fpga_NodeSetData1 | ( | Fpga_Node_t * | p, | |

| Fpga_Node_t * | pNode | |||

| ) |

Definition at line 108 of file fpgaCreate.c.

00108 { p->pLevel = pNode; }

| void Fpga_NodeSetLevel | ( | Fpga_Node_t * | p, | |

| Fpga_Node_t * | pNode | |||

| ) |

| void Fpga_NodeSetNextE | ( | Fpga_Node_t * | p, | |

| Fpga_Node_t * | pNextE | |||

| ) |

Definition at line 109 of file fpgaCreate.c.

00109 { p->pNextE = pNextE; }

| void Fpga_NodeSetRepr | ( | Fpga_Node_t * | p, | |

| Fpga_Node_t * | pRepr | |||

| ) |

Definition at line 110 of file fpgaCreate.c.

00110 { p->pRepr = pRepr; }

| void Fpga_NodeSetSwitching | ( | Fpga_Node_t * | p, | |

| float | Switching | |||

| ) |

Definition at line 111 of file fpgaCreate.c.

00111 { p->Switching = Switching; }

| void Fpga_SetSimpleLutLib | ( | int | nLutSize | ) |

Function*************************************************************

Synopsis [Sets simple LUT library.]

Description []

SideEffects []

SeeAlso []

Definition at line 249 of file fpga.c.

00250 { 00251 Fpga_LutLib_t s_LutLib10= { "lutlib",10, 0, {0,1,1,1,1,1,1,1,1,1,1}, {{0},{1},{1},{1},{1},{1},{1},{1},{1},{1},{1}} }; 00252 Fpga_LutLib_t s_LutLib9 = { "lutlib", 9, 0, {0,1,1,1,1,1,1,1,1,1}, {{0},{1},{1},{1},{1},{1},{1},{1},{1},{1}} }; 00253 Fpga_LutLib_t s_LutLib8 = { "lutlib", 8, 0, {0,1,1,1,1,1,1,1,1}, {{0},{1},{1},{1},{1},{1},{1},{1},{1}} }; 00254 Fpga_LutLib_t s_LutLib7 = { "lutlib", 7, 0, {0,1,1,1,1,1,1,1}, {{0},{1},{1},{1},{1},{1},{1},{1}} }; 00255 Fpga_LutLib_t s_LutLib6 = { "lutlib", 6, 0, {0,1,1,1,1,1,1}, {{0},{1},{1},{1},{1},{1},{1}} }; 00256 Fpga_LutLib_t s_LutLib5 = { "lutlib", 5, 0, {0,1,1,1,1,1}, {{0},{1},{1},{1},{1},{1}} }; 00257 Fpga_LutLib_t s_LutLib4 = { "lutlib", 4, 0, {0,1,1,1,1}, {{0},{1},{1},{1},{1}} }; 00258 Fpga_LutLib_t s_LutLib3 = { "lutlib", 3, 0, {0,1,1,1}, {{0},{1},{1},{1}} }; 00259 Fpga_LutLib_t * pLutLib; 00260 assert( nLutSize >= 3 && nLutSize <= 10 ); 00261 switch ( nLutSize ) 00262 { 00263 case 3: pLutLib = &s_LutLib3; break; 00264 case 4: pLutLib = &s_LutLib4; break; 00265 case 5: pLutLib = &s_LutLib5; break; 00266 case 6: pLutLib = &s_LutLib6; break; 00267 case 7: pLutLib = &s_LutLib7; break; 00268 case 8: pLutLib = &s_LutLib8; break; 00269 case 9: pLutLib = &s_LutLib9; break; 00270 case 10: pLutLib = &s_LutLib10; break; 00271 default: pLutLib = NULL; break; 00272 } 00273 if ( pLutLib == NULL ) 00274 return; 00275 Fpga_LutLibFree( Abc_FrameReadLibLut() ); 00276 Abc_FrameSetLibLut( Fpga_LutLibDup(pLutLib) ); 00277 }

| void* Fpga_TruthsCutBdd | ( | void * | dd, | |

| Fpga_Cut_t * | pCut | |||

| ) |

Function*************************************************************

Synopsis [Derives the truth table for one cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 76 of file fpgaTruth.c.

00077 { 00078 Fpga_NodeVec_t * vVisited; 00079 DdNode * bFunc; 00080 int i; 00081 assert( pCut->nLeaves > 1 ); 00082 // set the leaf variables 00083 for ( i = 0; i < pCut->nLeaves; i++ ) 00084 pCut->ppLeaves[i]->pCuts->uSign = (unsigned)Cudd_bddIthVar( dd, i ); 00085 // recursively compute the function 00086 vVisited = Fpga_NodeVecAlloc( 10 ); 00087 bFunc = Fpga_TruthsCutBdd_rec( dd, pCut, vVisited ); Cudd_Ref( bFunc ); 00088 // clean the intermediate BDDs 00089 for ( i = 0; i < pCut->nLeaves; i++ ) 00090 pCut->ppLeaves[i]->pCuts->uSign = 0; 00091 for ( i = 0; i < vVisited->nSize; i++ ) 00092 { 00093 pCut = (Fpga_Cut_t *)vVisited->pArray[i]; 00094 Cudd_RecursiveDeref( dd, (DdNode*)pCut->uSign ); 00095 pCut->uSign = 0; 00096 } 00097 // printf( "%d ", vVisited->nSize ); 00098 Fpga_NodeVecFree( vVisited ); 00099 Cudd_Deref( bFunc ); 00100 return bFunc; 00101 }

1.6.1

1.6.1