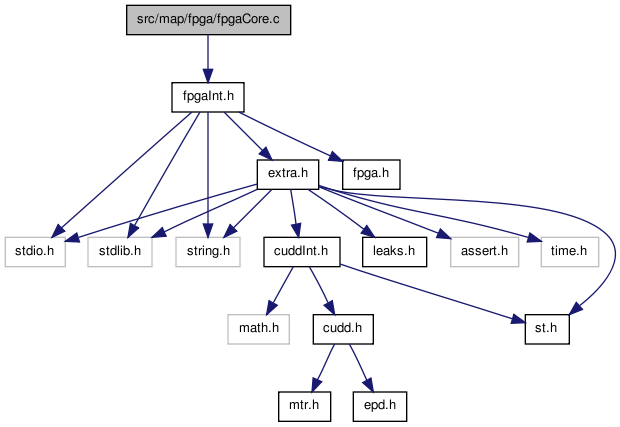

src/map/fpga/fpgaCore.c File Reference

#include "fpgaInt.h"

Go to the source code of this file.

Functions | |

| static int | Fpga_MappingPostProcess (Fpga_Man_t *p) |

| int | Fpga_Mapping (Fpga_Man_t *p) |

Variables | |

| int | s_MappingTime |

| int | s_MappingMem |

Function Documentation

| int Fpga_Mapping | ( | Fpga_Man_t * | p | ) |

FUNCTION DEFINITIONS ///Function*************************************************************

Synopsis [Performs technology mapping for the given object graph.]

Description [The object graph is stored in the mapping manager. First, all the AND-nodes, which fanout into the POs, are collected in the DFS fashion. Next, three steps are performed: the k-feasible cuts are computed for each node, the truth tables are computed for each cut, and the delay-optimal matches are assigned for each node.]

SideEffects []

SeeAlso []

Definition at line 50 of file fpgaCore.c.

00051 { 00052 int clk, clkTotal = clock(); 00053 00054 // collect the nodes reachable from POs in the DFS order (including the choices) 00055 p->vAnds = Fpga_MappingDfs( p, 1 ); 00056 Fpga_ManReportChoices( p ); // recomputes levels 00057 Fpga_MappingSetChoiceLevels( p ); 00058 00059 // compute the cuts of nodes in the DFS order 00060 clk = clock(); 00061 Fpga_MappingCuts( p ); 00062 p->timeCuts = clock() - clk; 00063 00064 // match the truth tables to the supergates 00065 clk = clock(); 00066 if ( !Fpga_MappingMatches( p, 1 ) ) 00067 return 0; 00068 p->timeMatch = clock() - clk; 00069 00070 // perform area recovery 00071 clk = clock(); 00072 if ( !Fpga_MappingPostProcess( p ) ) 00073 return 0; 00074 p->timeRecover = clock() - clk; 00075 //PRT( "Total mapping time", clock() - clkTotal ); 00076 00077 s_MappingTime = clock() - clkTotal; 00078 s_MappingMem = Fpga_CutCountAll(p) * (sizeof(Fpga_Cut_t) - sizeof(int) * (FPGA_MAX_LEAVES - p->nVarsMax)); 00079 00080 // print the AI-graph used for mapping 00081 //Fpga_ManShow( p, "test" ); 00082 // if ( p->fVerbose ) 00083 // Fpga_MappingPrintOutputArrivals( p ); 00084 if ( p->fVerbose ) 00085 { 00086 PRT( "Total time", clock() - clkTotal ); 00087 } 00088 return 1; 00089 }

| int Fpga_MappingPostProcess | ( | Fpga_Man_t * | p | ) | [static] |

CFile****************************************************************

FileName [fpgaCore.c]

PackageName [MVSIS 1.3: Multi-valued logic synthesis system.]

Synopsis [Technology mapping for variable-size-LUT FPGAs.]

Author [MVSIS Group]

Affiliation [UC Berkeley]

Date [Ver. 2.0. Started - August 18, 2004.]

Revision [

- Id

- fpgaCore.c,v 1.7 2004/10/01 23:41:04 satrajit Exp

] DECLARATIONS ///

Function*************************************************************

Synopsis [Postprocesses the mapped network for area recovery.]

Description [This procedure assumes that the mapping is assigned. It iterates the loop, in which the required times are computed and the mapping is updated. It is conceptually similar to the paper: V. Manohararajah, S. D. Brown, Z. G. Vranesic, Heuristics for area minimization in LUT-based FPGA technology mapping. Proc. IWLS '04.]

SideEffects []

SeeAlso []

Definition at line 106 of file fpgaCore.c.

00107 { 00108 int fShowSwitching = 0; 00109 int fRecoverAreaFlow = 1; 00110 int fRecoverArea = 1; 00111 float aAreaTotalCur, aAreaTotalCur2; 00112 int Iter, clk; 00113 00114 //if ( p->fVerbose ) 00115 // printf( "Best clock period = %5.2f\n", Fpga_TimeComputeArrivalMax(p) ); 00116 00117 // compute area, set references, and collect nodes used in the mapping 00118 Iter = 1; 00119 aAreaTotalCur = Fpga_MappingSetRefsAndArea( p ); 00120 if ( p->fVerbose ) 00121 { 00122 printf( "Iteration %dD : Area = %8.1f ", Iter++, aAreaTotalCur ); 00123 if ( fShowSwitching ) 00124 printf( "Switch = %8.1f ", Fpga_MappingGetSwitching(p,p->vMapping) ); 00125 else 00126 printf( "Delay = %5.2f ", Fpga_TimeComputeArrivalMax(p) ); 00127 00128 PRT( "Time", p->timeMatch ); 00129 } 00130 00131 if ( !p->fAreaRecovery ) 00132 return 1; 00133 00134 if ( fRecoverAreaFlow ) 00135 { 00136 clk = clock(); 00137 // compute the required times and the fanouts 00138 Fpga_TimeComputeRequiredGlobal( p, 1 ); 00139 // remap topologically 00140 Fpga_MappingMatches( p, 0 ); 00141 // get the resulting area 00142 // aAreaTotalCur = Fpga_MappingSetRefsAndArea( p ); 00143 aAreaTotalCur = Fpga_MappingAreaTrav( p ); 00144 // note that here we do not update the reference counter 00145 // for some reason, this works better on benchmarks 00146 if ( p->fVerbose ) 00147 { 00148 printf( "Iteration %dF : Area = %8.1f ", Iter++, aAreaTotalCur ); 00149 if ( fShowSwitching ) 00150 printf( "Switch = %8.1f ", Fpga_MappingGetSwitching(p,p->vMapping) ); 00151 else 00152 printf( "Delay = %5.2f ", Fpga_TimeComputeArrivalMax(p) ); 00153 PRT( "Time", clock() - clk ); 00154 } 00155 } 00156 00157 // update reference counters 00158 aAreaTotalCur2 = Fpga_MappingSetRefsAndArea( p ); 00159 assert( aAreaTotalCur == aAreaTotalCur2 ); 00160 00161 if ( fRecoverArea ) 00162 { 00163 clk = clock(); 00164 // compute the required times and the fanouts 00165 Fpga_TimeComputeRequiredGlobal( p, 0 ); 00166 // remap topologically 00167 if ( p->fSwitching ) 00168 Fpga_MappingMatchesSwitch( p ); 00169 else 00170 Fpga_MappingMatchesArea( p ); 00171 // get the resulting area 00172 aAreaTotalCur = Fpga_MappingSetRefsAndArea( p ); 00173 if ( p->fVerbose ) 00174 { 00175 printf( "Iteration %d%s : Area = %8.1f ", Iter++, (p->fSwitching?"S":"A"), aAreaTotalCur ); 00176 if ( fShowSwitching ) 00177 printf( "Switch = %8.1f ", Fpga_MappingGetSwitching(p,p->vMapping) ); 00178 else 00179 printf( "Delay = %5.2f ", Fpga_TimeComputeArrivalMax(p) ); 00180 PRT( "Time", clock() - clk ); 00181 } 00182 } 00183 00184 p->fAreaGlo = aAreaTotalCur; 00185 return 1; 00186 }

Variable Documentation

| int s_MappingMem |

Definition at line 35 of file abcPrint.c.

| int s_MappingTime |

CFile****************************************************************

FileName [abcPrint.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Network and node package.]

Synopsis [Printing statistics.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 20, 2005.]

Revision [

- Id

- abcPrint.c,v 1.00 2005/06/20 00:00:00 alanmi Exp

] DECLARATIONS ///

Definition at line 34 of file abcPrint.c.

1.6.1

1.6.1