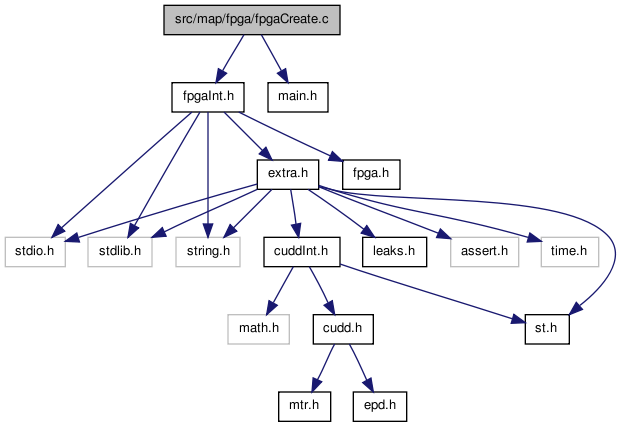

src/map/fpga/fpgaCreate.c File Reference

#include "fpgaInt.h"#include "main.h"

Go to the source code of this file.

Function Documentation

| Fpga_Node_t** Fpga_CutReadLeaves | ( | Fpga_Cut_t * | p | ) |

Definition at line 141 of file fpgaCreate.c.

00141 { return p->ppLeaves; }

| int Fpga_CutReadLeavesNum | ( | Fpga_Cut_t * | p | ) |

Function*************************************************************

Synopsis [Reads parameters from the cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 140 of file fpgaCreate.c.

00140 { return p->nLeaves; }

| static unsigned Fpga_HashKey2 | ( | Fpga_Node_t * | p0, | |

| Fpga_Node_t * | p1, | |||

| int | TableSize | |||

| ) | [inline, static] |

Definition at line 31 of file fpgaCreate.c.

| int Fpga_LibReadLutMax | ( | Fpga_LutLib_t * | pLib | ) |

Function*************************************************************

Synopsis [Reads the parameters of the LUT library.]

Description []

SideEffects []

SeeAlso []

Definition at line 85 of file fpgaCreate.c.

00085 { return pLib->LutMax; }

| Fpga_Man_t* Fpga_ManCreate | ( | int | nInputs, | |

| int | nOutputs, | |||

| int | fVerbose | |||

| ) |

Function*************************************************************

Synopsis [Create the mapping manager.]

Description [The number of inputs and outputs is assumed to be known is advance. It is much simpler to have them fixed upfront. When it comes to representing the object graph in the form of AIG, the resulting manager is similar to the regular AIG manager, except that it does not use reference counting (and therefore does not have garbage collections). It does have table resizing. The data structure is more flexible to represent additional information needed for mapping.]

SideEffects []

SeeAlso []

Definition at line 162 of file fpgaCreate.c.

00163 { 00164 Fpga_Man_t * p; 00165 int i; 00166 00167 // start the manager 00168 p = ALLOC( Fpga_Man_t, 1 ); 00169 memset( p, 0, sizeof(Fpga_Man_t) ); 00170 p->pLutLib = Abc_FrameReadLibLut(); 00171 p->nVarsMax = p->pLutLib->LutMax; 00172 p->fVerbose = fVerbose; 00173 p->fAreaRecovery = 1; 00174 p->fEpsilon = (float)0.001; 00175 00176 Fpga_TableCreate( p ); 00177 //if ( p->fVerbose ) 00178 // printf( "Node = %d (%d) bytes. Cut = %d bytes.\n", sizeof(Fpga_Node_t), FPGA_NUM_BYTES(sizeof(Fpga_Node_t)), sizeof(Fpga_Cut_t) ); 00179 p->mmNodes = Extra_MmFixedStart( FPGA_NUM_BYTES(sizeof(Fpga_Node_t)) ); 00180 p->mmCuts = Extra_MmFixedStart( sizeof(Fpga_Cut_t) ); 00181 00182 assert( p->nVarsMax > 0 ); 00183 // Fpga_MappingSetupTruthTables( p->uTruths ); 00184 00185 // make sure the constant node will get index -1 00186 p->nNodes = -1; 00187 // create the constant node 00188 p->pConst1 = Fpga_NodeCreate( p, NULL, NULL ); 00189 p->vNodesAll = Fpga_NodeVecAlloc( 1000 ); 00190 p->vMapping = Fpga_NodeVecAlloc( 1000 ); 00191 00192 // create the PI nodes 00193 p->nInputs = nInputs; 00194 p->pInputs = ALLOC( Fpga_Node_t *, nInputs ); 00195 for ( i = 0; i < nInputs; i++ ) 00196 p->pInputs[i] = Fpga_NodeCreate( p, NULL, NULL ); 00197 00198 // create the place for the output nodes 00199 p->nOutputs = nOutputs; 00200 p->pOutputs = ALLOC( Fpga_Node_t *, nOutputs ); 00201 memset( p->pOutputs, 0, sizeof(Fpga_Node_t *) * nOutputs ); 00202 return p; 00203 }

| void Fpga_ManFree | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis [Deallocates the mapping manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 216 of file fpgaCreate.c.

00217 { 00218 // Fpga_ManStats( p ); 00219 // int i; 00220 // for ( i = 0; i < p->vNodesAll->nSize; i++ ) 00221 // Fpga_NodeVecFree( p->vNodesAll->pArray[i]->vFanouts ); 00222 // Fpga_NodeVecFree( p->pConst1->vFanouts ); 00223 if ( p->vMapping ) 00224 Fpga_NodeVecFree( p->vMapping ); 00225 if ( p->vAnds ) 00226 Fpga_NodeVecFree( p->vAnds ); 00227 if ( p->vNodesAll ) 00228 Fpga_NodeVecFree( p->vNodesAll ); 00229 Extra_MmFixedStop( p->mmNodes ); 00230 Extra_MmFixedStop( p->mmCuts ); 00231 FREE( p->ppOutputNames ); 00232 FREE( p->pInputArrivals ); 00233 FREE( p->pInputs ); 00234 FREE( p->pOutputs ); 00235 FREE( p->pBins ); 00236 FREE( p ); 00237 }

| void Fpga_ManPrintTimeStats | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis [Prints runtime statistics of the mapping manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 251 of file fpgaCreate.c.

00252 { 00253 extern char * pNetName; 00254 extern int TotalLuts; 00255 // FILE * pTable; 00256 00257 00258 /* 00259 pTable = fopen( "stats.txt", "a+" ); 00260 fprintf( pTable, "%s ", pNetName ); 00261 fprintf( pTable, "%.0f ", p->fRequiredGlo ); 00262 // fprintf( pTable, "%.0f ", p->fAreaGlo );//+ (float)nOutputInvs ); 00263 fprintf( pTable, "%.0f ", (float)TotalLuts ); 00264 fprintf( pTable, "%4.2f\n", (float)(p->timeTotal-p->timeToMap)/(float)(CLOCKS_PER_SEC) ); 00265 fclose( pTable ); 00266 */ 00267 00268 // printf( "N-canonical = %d. Matchings = %d. ", p->nCanons, p->nMatches ); 00269 // printf( "Choice nodes = %d. Choices = %d.\n", p->nChoiceNodes, p->nChoices ); 00270 PRT( "ToMap", p->timeToMap ); 00271 PRT( "Cuts ", p->timeCuts ); 00272 PRT( "Match", p->timeMatch ); 00273 PRT( "Area ", p->timeRecover ); 00274 PRT( "ToNet", p->timeToNet ); 00275 PRT( "TOTAL", p->timeTotal ); 00276 if ( p->time1 ) { PRT( "time1", p->time1 ); } 00277 if ( p->time2 ) { PRT( "time2", p->time2 ); } 00278 }

| Fpga_Node_t* Fpga_ManReadConst1 | ( | Fpga_Man_t * | p | ) |

Definition at line 52 of file fpgaCreate.c.

00052 { return p->pConst1; }

| float* Fpga_ManReadInputArrivals | ( | Fpga_Man_t * | p | ) |

Definition at line 53 of file fpgaCreate.c.

00053 { return p->pInputArrivals;}

| int Fpga_ManReadInputNum | ( | Fpga_Man_t * | p | ) |

FUNCTION DEFINITIONS ///Function*************************************************************

Synopsis [Reads parameters of the mapping manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 48 of file fpgaCreate.c.

00048 { return p->nInputs; }

| Fpga_Node_t** Fpga_ManReadInputs | ( | Fpga_Man_t * | p | ) |

Definition at line 50 of file fpgaCreate.c.

00050 { return p->pInputs; }

| float* Fpga_ManReadLutAreas | ( | Fpga_Man_t * | p | ) |

Definition at line 55 of file fpgaCreate.c.

| int Fpga_ManReadOutputNum | ( | Fpga_Man_t * | p | ) |

Definition at line 49 of file fpgaCreate.c.

00049 { return p->nOutputs; }

| Fpga_Node_t** Fpga_ManReadOutputs | ( | Fpga_Man_t * | p | ) |

Definition at line 51 of file fpgaCreate.c.

00051 { return p->pOutputs; }

| int Fpga_ManReadVerbose | ( | Fpga_Man_t * | p | ) |

Definition at line 54 of file fpgaCreate.c.

00054 { return p->fVerbose; }

| void Fpga_ManSetAreaLimit | ( | Fpga_Man_t * | p, | |

| float | AreaLimit | |||

| ) |

Definition at line 63 of file fpgaCreate.c.

00063 { p->AreaLimit = AreaLimit; }

| void Fpga_ManSetAreaRecovery | ( | Fpga_Man_t * | p, | |

| int | fAreaRecovery | |||

| ) |

Definition at line 61 of file fpgaCreate.c.

00061 { p->fAreaRecovery = fAreaRecovery;}

| void Fpga_ManSetChoiceNodeNum | ( | Fpga_Man_t * | p, | |

| int | nChoiceNodes | |||

| ) |

Definition at line 65 of file fpgaCreate.c.

00065 { p->nChoiceNodes = nChoiceNodes; }

| void Fpga_ManSetChoiceNum | ( | Fpga_Man_t * | p, | |

| int | nChoices | |||

| ) |

Definition at line 66 of file fpgaCreate.c.

00066 { p->nChoices = nChoices; }

| void Fpga_ManSetDelayLimit | ( | Fpga_Man_t * | p, | |

| float | DelayLimit | |||

| ) |

Definition at line 62 of file fpgaCreate.c.

00062 { p->DelayLimit = DelayLimit; }

| void Fpga_ManSetDelayTarget | ( | Fpga_Man_t * | p, | |

| float | DelayTarget | |||

| ) |

Definition at line 71 of file fpgaCreate.c.

00071 { p->DelayTarget = DelayTarget; }

| void Fpga_ManSetInputArrivals | ( | Fpga_Man_t * | p, | |

| float * | pArrivals | |||

| ) |

Definition at line 60 of file fpgaCreate.c.

00060 { p->pInputArrivals = pArrivals; }

| void Fpga_ManSetLatchNum | ( | Fpga_Man_t * | p, | |

| int | nLatches | |||

| ) |

Definition at line 70 of file fpgaCreate.c.

00070 { p->nLatches = nLatches; }

| void Fpga_ManSetLatchPaths | ( | Fpga_Man_t * | p, | |

| int | fLatchPaths | |||

| ) |

Definition at line 69 of file fpgaCreate.c.

00069 { p->fLatchPaths = fLatchPaths; }

| void Fpga_ManSetName | ( | Fpga_Man_t * | p, | |

| char * | pFileName | |||

| ) |

Definition at line 72 of file fpgaCreate.c.

00072 { p->pFileName = pFileName; }

| void Fpga_ManSetOutputNames | ( | Fpga_Man_t * | p, | |

| char ** | ppNames | |||

| ) |

Definition at line 59 of file fpgaCreate.c.

00059 { p->ppOutputNames = ppNames; }

| void Fpga_ManSetSwitching | ( | Fpga_Man_t * | p, | |

| int | fSwitching | |||

| ) |

Definition at line 68 of file fpgaCreate.c.

00068 { p->fSwitching = fSwitching; }

| void Fpga_ManSetTimeLimit | ( | Fpga_Man_t * | p, | |

| float | TimeLimit | |||

| ) |

Definition at line 64 of file fpgaCreate.c.

00064 { p->TimeLimit = TimeLimit; }

| void Fpga_ManSetTimeToMap | ( | Fpga_Man_t * | p, | |

| int | Time | |||

| ) |

Definition at line 56 of file fpgaCreate.c.

00056 { p->timeToMap = Time; }

| void Fpga_ManSetTimeToNet | ( | Fpga_Man_t * | p, | |

| int | Time | |||

| ) |

Definition at line 57 of file fpgaCreate.c.

00057 { p->timeToNet = Time; }

| void Fpga_ManSetTimeTotal | ( | Fpga_Man_t * | p, | |

| int | Time | |||

| ) |

Definition at line 58 of file fpgaCreate.c.

00058 { p->timeTotal = Time; }

| void Fpga_ManSetVerbose | ( | Fpga_Man_t * | p, | |

| int | fVerbose | |||

| ) |

Definition at line 67 of file fpgaCreate.c.

00067 { p->fVerbose = fVerbose; }

| void Fpga_ManStats | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis [Prints some interesting stats.]

Description []

SideEffects []

SeeAlso []

Definition at line 562 of file fpgaCreate.c.

00563 { 00564 FILE * pTable; 00565 pTable = fopen( "stats.txt", "a+" ); 00566 fprintf( pTable, "%s ", p->pFileName ); 00567 fprintf( pTable, "%4d ", p->nInputs - p->nLatches ); 00568 fprintf( pTable, "%4d ", p->nOutputs - p->nLatches ); 00569 fprintf( pTable, "%4d ", p->nLatches ); 00570 fprintf( pTable, "%7d ", p->vAnds->nSize ); 00571 fprintf( pTable, "%7d ", Fpga_CutCountAll(p) ); 00572 fprintf( pTable, "%2d\n", (int)p->fRequiredGlo ); 00573 fclose( pTable ); 00574 }

| Fpga_Node_t* Fpga_NodeAnd | ( | Fpga_Man_t * | p, | |

| Fpga_Node_t * | p1, | |||

| Fpga_Node_t * | p2 | |||

| ) |

Function*************************************************************

Synopsis [Elementary AND operation on the AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 468 of file fpgaCreate.c.

00469 { 00470 Fpga_Node_t * pNode; 00471 pNode = Fpga_TableLookup( p, p1, p2 ); 00472 return pNode; 00473 }

| int Fpga_NodeComparePhase | ( | Fpga_Node_t * | p1, | |

| Fpga_Node_t * | p2 | |||

| ) |

Definition at line 127 of file fpgaCreate.c.

00127 { assert( !Fpga_IsComplement(p1) ); assert( !Fpga_IsComplement(p2) ); return p1->fInv ^ p2->fInv; }

| Fpga_Node_t* Fpga_NodeCreate | ( | Fpga_Man_t * | p, | |

| Fpga_Node_t * | p1, | |||

| Fpga_Node_t * | p2 | |||

| ) |

Function*************************************************************

Synopsis [Creates a new node.]

Description [This procedure should be called to create the constant node and the PI nodes first.]

SideEffects []

SeeAlso []

Definition at line 292 of file fpgaCreate.c.

00293 { 00294 Fpga_Node_t * pNode; 00295 // create the node 00296 pNode = (Fpga_Node_t *)Extra_MmFixedEntryFetch( p->mmNodes ); 00297 memset( pNode, 0, sizeof(Fpga_Node_t) ); 00298 // set very large required time 00299 pNode->tRequired = FPGA_FLOAT_LARGE; 00300 pNode->aEstFanouts = -1; 00301 pNode->p1 = p1; 00302 pNode->p2 = p2; 00303 // set the number of this node 00304 pNode->Num = p->nNodes++; 00305 // place to store the fanouts 00306 // pNode->vFanouts = Fpga_NodeVecAlloc( 5 ); 00307 // store this node in the internal array 00308 if ( pNode->Num >= 0 ) 00309 Fpga_NodeVecPush( p->vNodesAll, pNode ); 00310 else 00311 pNode->fInv = 1; 00312 // set the level of this node 00313 if ( p1 ) 00314 { 00315 #ifdef FPGA_ALLOCATE_FANOUT 00316 // create the fanout info 00317 Fpga_NodeAddFaninFanout( Fpga_Regular(p1), pNode ); 00318 Fpga_NodeAddFaninFanout( Fpga_Regular(p2), pNode ); 00319 #endif 00320 // compute the level 00321 pNode->Level = 1 + FPGA_MAX(Fpga_Regular(p1)->Level, Fpga_Regular(p2)->Level); 00322 pNode->fInv = Fpga_NodeIsSimComplement(p1) & Fpga_NodeIsSimComplement(p2); 00323 } 00324 // reference the inputs 00325 if ( p1 ) Fpga_NodeRef(p1); 00326 if ( p2 ) Fpga_NodeRef(p2); 00327 return pNode; 00328 }

| Fpga_Node_t* Fpga_NodeExor | ( | Fpga_Man_t * | p, | |

| Fpga_Node_t * | p1, | |||

| Fpga_Node_t * | p2 | |||

| ) |

Function*************************************************************

Synopsis [Elementary EXOR operation on the AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 504 of file fpgaCreate.c.

00505 { 00506 return Fpga_NodeMux( p, p1, Fpga_Not(p2), p2 ); 00507 }

| int Fpga_NodeIsAnd | ( | Fpga_Node_t * | p | ) |

Definition at line 126 of file fpgaCreate.c.

00126 { return (Fpga_Regular(p))->p1 != NULL; }

| int Fpga_NodeIsConst | ( | Fpga_Node_t * | p | ) |

Function*************************************************************

Synopsis [Checks the type of the node.]

Description []

SideEffects []

SeeAlso []

Definition at line 124 of file fpgaCreate.c.

00124 { return (Fpga_Regular(p))->Num == -1; }

| int Fpga_NodeIsVar | ( | Fpga_Node_t * | p | ) |

Definition at line 125 of file fpgaCreate.c.

00125 { return (Fpga_Regular(p))->p1 == NULL && (Fpga_Regular(p))->Num >= 0; }

| Fpga_Node_t* Fpga_NodeMux | ( | Fpga_Man_t * | p, | |

| Fpga_Node_t * | pC, | |||

| Fpga_Node_t * | pT, | |||

| Fpga_Node_t * | pE | |||

| ) |

Function*************************************************************

Synopsis [Elementary MUX operation on the AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 520 of file fpgaCreate.c.

00521 { 00522 Fpga_Node_t * pAnd1, * pAnd2, * pRes; 00523 pAnd1 = Fpga_TableLookup( p, pC, pT ); 00524 pAnd2 = Fpga_TableLookup( p, Fpga_Not(pC), pE ); 00525 pRes = Fpga_NodeOr( p, pAnd1, pAnd2 ); 00526 return pRes; 00527 }

| Fpga_Node_t* Fpga_NodeOr | ( | Fpga_Man_t * | p, | |

| Fpga_Node_t * | p1, | |||

| Fpga_Node_t * | p2 | |||

| ) |

Function*************************************************************

Synopsis [Elementary OR operation on the AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 486 of file fpgaCreate.c.

00487 { 00488 Fpga_Node_t * pNode; 00489 pNode = Fpga_Not( Fpga_TableLookup( p, Fpga_Not(p1), Fpga_Not(p2) ) ); 00490 return pNode; 00491 }

| Fpga_Cut_t* Fpga_NodeReadCutBest | ( | Fpga_Node_t * | p | ) |

Definition at line 104 of file fpgaCreate.c.

00104 { return p->pCutBest; }

| Fpga_Cut_t* Fpga_NodeReadCuts | ( | Fpga_Node_t * | p | ) |

Definition at line 103 of file fpgaCreate.c.

00103 { return p->pCuts; }

| char* Fpga_NodeReadData0 | ( | Fpga_Node_t * | p | ) |

Function*************************************************************

Synopsis [Reads parameters of the mapping node.]

Description []

SideEffects []

SeeAlso []

Definition at line 98 of file fpgaCreate.c.

00098 { return p->pData0; }

| Fpga_Node_t* Fpga_NodeReadData1 | ( | Fpga_Node_t * | p | ) |

Definition at line 99 of file fpgaCreate.c.

00099 { return p->pLevel; }

| int Fpga_NodeReadLevel | ( | Fpga_Node_t * | p | ) |

Definition at line 102 of file fpgaCreate.c.

00102 { return Fpga_Regular(p)->Level; }

| int Fpga_NodeReadNum | ( | Fpga_Node_t * | p | ) |

Definition at line 101 of file fpgaCreate.c.

00101 { return p->Num; }

| Fpga_Node_t* Fpga_NodeReadOne | ( | Fpga_Node_t * | p | ) |

Definition at line 105 of file fpgaCreate.c.

00105 { return p->p1; }

| int Fpga_NodeReadRefs | ( | Fpga_Node_t * | p | ) |

Definition at line 100 of file fpgaCreate.c.

00100 { return p->nRefs; }

| Fpga_Node_t* Fpga_NodeReadTwo | ( | Fpga_Node_t * | p | ) |

Definition at line 106 of file fpgaCreate.c.

00106 { return p->p2; }

| void Fpga_NodeSetChoice | ( | Fpga_Man_t * | pMan, | |

| Fpga_Node_t * | pNodeOld, | |||

| Fpga_Node_t * | pNodeNew | |||

| ) |

Function*************************************************************

Synopsis [Sets the node to be equivalent to the given one.]

Description [This procedure is a work-around for the equivalence check. Does not verify the equivalence. Use at the user's risk.]

SideEffects []

SeeAlso []

Definition at line 542 of file fpgaCreate.c.

| void Fpga_NodeSetData0 | ( | Fpga_Node_t * | p, | |

| char * | pData | |||

| ) |

Definition at line 107 of file fpgaCreate.c.

00107 { p->pData0 = pData; }

| void Fpga_NodeSetData1 | ( | Fpga_Node_t * | p, | |

| Fpga_Node_t * | pNode | |||

| ) |

Definition at line 108 of file fpgaCreate.c.

00108 { p->pLevel = pNode; }

| void Fpga_NodeSetNextE | ( | Fpga_Node_t * | p, | |

| Fpga_Node_t * | pNextE | |||

| ) |

Definition at line 109 of file fpgaCreate.c.

00109 { p->pNextE = pNextE; }

| void Fpga_NodeSetRepr | ( | Fpga_Node_t * | p, | |

| Fpga_Node_t * | pRepr | |||

| ) |

Definition at line 110 of file fpgaCreate.c.

00110 { p->pRepr = pRepr; }

| void Fpga_NodeSetSwitching | ( | Fpga_Node_t * | p, | |

| float | Switching | |||

| ) |

Definition at line 111 of file fpgaCreate.c.

00111 { p->Switching = Switching; }

| void Fpga_TableCreate | ( | Fpga_Man_t * | pMan | ) | [static] |

CFile****************************************************************

FileName [fpgaCreate.c]

PackageName [MVSIS 1.3: Multi-valued logic synthesis system.]

Synopsis [Technology mapping for variable-size-LUT FPGAs.]

Author [MVSIS Group]

Affiliation [UC Berkeley]

Date [Ver. 2.0. Started - August 18, 2004.]

Revision [

- Id

- fpgaCreate.c,v 1.8 2004/09/30 21:18:09 satrajit Exp

] DECLARATIONS ///

Function*************************************************************

Synopsis [Create the unique table of AND gates.]

Description []

SideEffects []

SeeAlso []

Definition at line 341 of file fpgaCreate.c.

00342 { 00343 assert( pMan->pBins == NULL ); 00344 pMan->nBins = Cudd_Prime(50000); 00345 pMan->pBins = ALLOC( Fpga_Node_t *, pMan->nBins ); 00346 memset( pMan->pBins, 0, sizeof(Fpga_Node_t *) * pMan->nBins ); 00347 pMan->nNodes = 0; 00348 }

| Fpga_Node_t * Fpga_TableLookup | ( | Fpga_Man_t * | pMan, | |

| Fpga_Node_t * | p1, | |||

| Fpga_Node_t * | p2 | |||

| ) | [static] |

Function*************************************************************

Synopsis [Looks up the AND2 node in the unique table.]

Description [This procedure implements one-level hashing. All the nodes are hashed by their children. If the node with the same children was already created, it is returned by the call to this procedure. If it does not exist, this procedure creates a new node with these children. ]

SideEffects []

SeeAlso []

Definition at line 364 of file fpgaCreate.c.

00365 { 00366 Fpga_Node_t * pEnt; 00367 unsigned Key; 00368 00369 if ( p1 == p2 ) 00370 return p1; 00371 if ( p1 == Fpga_Not(p2) ) 00372 return Fpga_Not(pMan->pConst1); 00373 if ( Fpga_NodeIsConst(p1) ) 00374 { 00375 if ( p1 == pMan->pConst1 ) 00376 return p2; 00377 return Fpga_Not(pMan->pConst1); 00378 } 00379 if ( Fpga_NodeIsConst(p2) ) 00380 { 00381 if ( p2 == pMan->pConst1 ) 00382 return p1; 00383 return Fpga_Not(pMan->pConst1); 00384 } 00385 00386 if ( Fpga_Regular(p1)->Num > Fpga_Regular(p2)->Num ) 00387 pEnt = p1, p1 = p2, p2 = pEnt; 00388 00389 Key = Fpga_HashKey2( p1, p2, pMan->nBins ); 00390 for ( pEnt = pMan->pBins[Key]; pEnt; pEnt = pEnt->pNext ) 00391 if ( pEnt->p1 == p1 && pEnt->p2 == p2 ) 00392 return pEnt; 00393 // resize the table 00394 if ( pMan->nNodes >= 2 * pMan->nBins ) 00395 { 00396 Fpga_TableResize( pMan ); 00397 Key = Fpga_HashKey2( p1, p2, pMan->nBins ); 00398 } 00399 // create the new node 00400 pEnt = Fpga_NodeCreate( pMan, p1, p2 ); 00401 // add the node to the corresponding linked list in the table 00402 pEnt->pNext = pMan->pBins[Key]; 00403 pMan->pBins[Key] = pEnt; 00404 return pEnt; 00405 }

| void Fpga_TableResize | ( | Fpga_Man_t * | pMan | ) | [static] |

Function*************************************************************

Synopsis [Resizes the table.]

Description []

SideEffects []

SeeAlso []

Definition at line 419 of file fpgaCreate.c.

00420 { 00421 Fpga_Node_t ** pBinsNew; 00422 Fpga_Node_t * pEnt, * pEnt2; 00423 int nBinsNew, Counter, i, clk; 00424 unsigned Key; 00425 00426 clk = clock(); 00427 // get the new table size 00428 nBinsNew = Cudd_Prime(2 * pMan->nBins); 00429 // allocate a new array 00430 pBinsNew = ALLOC( Fpga_Node_t *, nBinsNew ); 00431 memset( pBinsNew, 0, sizeof(Fpga_Node_t *) * nBinsNew ); 00432 // rehash the entries from the old table 00433 Counter = 0; 00434 for ( i = 0; i < pMan->nBins; i++ ) 00435 for ( pEnt = pMan->pBins[i], pEnt2 = pEnt? pEnt->pNext: NULL; pEnt; 00436 pEnt = pEnt2, pEnt2 = pEnt? pEnt->pNext: NULL ) 00437 { 00438 Key = Fpga_HashKey2( pEnt->p1, pEnt->p2, nBinsNew ); 00439 pEnt->pNext = pBinsNew[Key]; 00440 pBinsNew[Key] = pEnt; 00441 Counter++; 00442 } 00443 assert( Counter == pMan->nNodes - pMan->nInputs ); 00444 if ( pMan->fVerbose ) 00445 { 00446 // printf( "Increasing the unique table size from %6d to %6d. ", pMan->nBins, nBinsNew ); 00447 // PRT( "Time", clock() - clk ); 00448 } 00449 // replace the table and the parameters 00450 free( pMan->pBins ); 00451 pMan->pBins = pBinsNew; 00452 pMan->nBins = nBinsNew; 00453 }

1.6.1

1.6.1