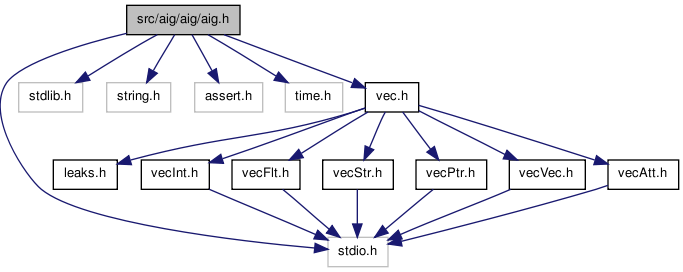

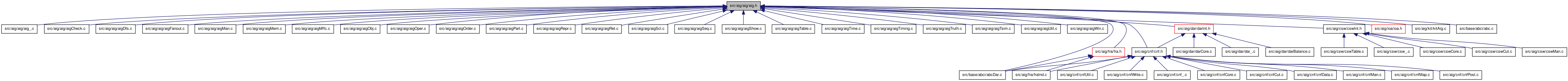

src/aig/aig/aig.h File Reference

#include <stdio.h>#include <stdlib.h>#include <string.h>#include <assert.h>#include <time.h>#include "vec.h"

Go to the source code of this file.

Define Documentation

| #define Aig_ManForEachAssert | ( | p, | |||

| pObj, | |||||

| i | ) | Vec_PtrForEachEntryStart( p->vPos, pObj, i, Aig_ManPoNum(p)-p->nAsserts ) |

| #define Aig_ManForEachLiLoSeq | ( | p, | |||

| pObjLi, | |||||

| pObjLo, | |||||

| k | ) |

for ( k = 0; (k < Aig_ManRegNum(p)) && (((pObjLi) = Aig_ManLi(p, k)), 1) \ && (((pObjLo)=Aig_ManLo(p, k)), 1); k++ )

| #define Aig_ManForEachLiSeq | ( | p, | |||

| pObj, | |||||

| i | ) | Vec_PtrForEachEntryStart( p->vPos, pObj, i, Aig_ManPoNum(p)-Aig_ManRegNum(p) ) |

| #define Aig_ManForEachLoSeq | ( | p, | |||

| pObj, | |||||

| i | ) | Vec_PtrForEachEntryStart( p->vPis, pObj, i, Aig_ManPiNum(p)-Aig_ManRegNum(p) ) |

| #define Aig_ManForEachNode | ( | p, | |||

| pObj, | |||||

| i | ) | Vec_PtrForEachEntry( p->vObjs, pObj, i ) if ( (pObj) == NULL || !Aig_ObjIsNode(pObj) ) {} else |

| #define Aig_ManForEachNodeInOrder | ( | p, | |||

| pObj | ) |

for ( assert(p->pOrderData), p->iPrev = 0, p->iNext = p->pOrderData[1]; \ p->iNext && (((pObj) = Aig_ManObj(p, p->iNext)), 1); \ p->iNext = p->pOrderData[2*p->iPrev+1] )

| #define Aig_ManForEachNodeVec | ( | p, | |||

| vIds, | |||||

| pObj, | |||||

| i | ) | for ( i = 0; i < Vec_IntSize(vIds) && ((pObj) = Aig_ManObj(p, Vec_IntEntry(vIds,i))); i++ ) |

| #define Aig_ManForEachObj | ( | p, | |||

| pObj, | |||||

| i | ) | Vec_PtrForEachEntry( p->vObjs, pObj, i ) if ( (pObj) == NULL ) {} else |

| #define Aig_ManForEachPi | ( | p, | |||

| pObj, | |||||

| i | ) | Vec_PtrForEachEntry( p->vPis, pObj, i ) |

| #define Aig_ManForEachPiSeq | ( | p, | |||

| pObj, | |||||

| i | ) | Vec_PtrForEachEntryStop( p->vPis, pObj, i, Aig_ManPiNum(p)-Aig_ManRegNum(p) ) |

| #define Aig_ManForEachPo | ( | p, | |||

| pObj, | |||||

| i | ) | Vec_PtrForEachEntry( p->vPos, pObj, i ) |

| #define Aig_ManForEachPoSeq | ( | p, | |||

| pObj, | |||||

| i | ) | Vec_PtrForEachEntryStop( p->vPos, pObj, i, Aig_ManPoNum(p)-Aig_ManRegNum(p) ) |

| #define AIG_MIN | ( | a, | |||

| b | ) | (((a) < (b))? (a) : (b)) |

| #define Aig_ObjForEachFanout | ( | p, | |||

| pObj, | |||||

| pFanout, | |||||

| iFan, | |||||

| i | ) |

for ( assert(p->pFanData), i = 0; (i < (int)(pObj)->nRefs) && \ (((iFan) = i? Aig_ObjFanoutNext(p, iFan) : Aig_ObjFanout0Int(p, pObj->Id)), 1) && \ (((pFanout) = Aig_ManObj(p, iFan>>1)), 1); i++ )

| #define PRT | ( | a, | |||

| t | ) | printf("%s = ", (a)); printf("%6.2f sec\n", (float)(t)/(float)(CLOCKS_PER_SEC)) |

Typedef Documentation

| typedef struct Aig_Man_t_ Aig_Man_t |

CFile****************************************************************

FileName [aig.h]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [AIG package.]

Synopsis [External declarations.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - April 28, 2007.]

Revision [

- Id

- aig.h,v 1.00 2007/04/28 00:00:00 alanmi Exp

] INCLUDES /// PARAMETERS /// BASIC TYPES ///

| typedef struct Aig_MmFixed_t_ Aig_MmFixed_t |

| typedef struct Aig_MmFlex_t_ Aig_MmFlex_t |

| typedef struct Aig_MmStep_t_ Aig_MmStep_t |

| typedef struct Aig_Obj_t_ Aig_Obj_t |

| typedef struct Aig_TMan_t_ Aig_TMan_t |

Enumeration Type Documentation

| enum Aig_Type_t |

- Enumerator:

AIG_OBJ_NONE AIG_OBJ_CONST1 AIG_OBJ_PI AIG_OBJ_PO AIG_OBJ_BUF AIG_OBJ_AND AIG_OBJ_EXOR AIG_OBJ_LATCH AIG_OBJ_VOID

Definition at line 56 of file aig.h.

00056 { 00057 AIG_OBJ_NONE, // 0: non-existent object 00058 AIG_OBJ_CONST1, // 1: constant 1 00059 AIG_OBJ_PI, // 2: primary input 00060 AIG_OBJ_PO, // 3: primary output 00061 AIG_OBJ_BUF, // 4: buffer node 00062 AIG_OBJ_AND, // 5: AND node 00063 AIG_OBJ_EXOR, // 6: EXOR node 00064 AIG_OBJ_LATCH, // 7: latch 00065 AIG_OBJ_VOID // 8: unused object 00066 } Aig_Type_t;

Function Documentation

Function*************************************************************

Synopsis [Performs canonicization step.]

Description [The argument nodes can be complemented.]

SideEffects []

SeeAlso []

Definition at line 138 of file aigOper.c.

00139 { 00140 Aig_Obj_t * pGhost, * pResult; 00141 // Aig_Obj_t * pFan0, * pFan1; 00142 // check trivial cases 00143 if ( p0 == p1 ) 00144 return p0; 00145 if ( p0 == Aig_Not(p1) ) 00146 return Aig_Not(p->pConst1); 00147 if ( Aig_Regular(p0) == p->pConst1 ) 00148 return p0 == p->pConst1 ? p1 : Aig_Not(p->pConst1); 00149 if ( Aig_Regular(p1) == p->pConst1 ) 00150 return p1 == p->pConst1 ? p0 : Aig_Not(p->pConst1); 00151 // check not so trivial cases 00152 if ( p->fAddStrash && (Aig_ObjIsNode(Aig_Regular(p0)) || Aig_ObjIsNode(Aig_Regular(p1))) ) 00153 { // http://fmv.jku.at/papers/BrummayerBiere-MEMICS06.pdf 00154 Aig_Obj_t * pFanA, * pFanB, * pFanC, * pFanD; 00155 pFanA = Aig_ObjChild0(Aig_Regular(p0)); 00156 pFanB = Aig_ObjChild1(Aig_Regular(p0)); 00157 pFanC = Aig_ObjChild0(Aig_Regular(p1)); 00158 pFanD = Aig_ObjChild1(Aig_Regular(p1)); 00159 if ( Aig_IsComplement(p0) ) 00160 { 00161 if ( pFanA == Aig_Not(p1) || pFanB == Aig_Not(p1) ) 00162 return p1; 00163 if ( pFanB == p1 ) 00164 return Aig_And( p, Aig_Not(pFanA), pFanB ); 00165 if ( pFanA == p1 ) 00166 return Aig_And( p, Aig_Not(pFanB), pFanA ); 00167 } 00168 else 00169 { 00170 if ( pFanA == Aig_Not(p1) || pFanB == Aig_Not(p1) ) 00171 return Aig_Not(p->pConst1); 00172 if ( pFanA == p1 || pFanB == p1 ) 00173 return p0; 00174 } 00175 if ( Aig_IsComplement(p1) ) 00176 { 00177 if ( pFanC == Aig_Not(p0) || pFanD == Aig_Not(p0) ) 00178 return p0; 00179 if ( pFanD == p0 ) 00180 return Aig_And( p, Aig_Not(pFanC), pFanD ); 00181 if ( pFanC == p0 ) 00182 return Aig_And( p, Aig_Not(pFanD), pFanC ); 00183 } 00184 else 00185 { 00186 if ( pFanC == Aig_Not(p0) || pFanD == Aig_Not(p0) ) 00187 return Aig_Not(p->pConst1); 00188 if ( pFanC == p0 || pFanD == p0 ) 00189 return p1; 00190 } 00191 if ( !Aig_IsComplement(p0) && !Aig_IsComplement(p1) ) 00192 { 00193 if ( pFanA == Aig_Not(pFanC) || pFanA == Aig_Not(pFanD) || pFanB == Aig_Not(pFanC) || pFanB == Aig_Not(pFanD) ) 00194 return Aig_Not(p->pConst1); 00195 if ( pFanA == pFanC || pFanB == pFanC ) 00196 return Aig_And( p, p0, pFanD ); 00197 if ( pFanB == pFanC || pFanB == pFanD ) 00198 return Aig_And( p, pFanA, p1 ); 00199 if ( pFanA == pFanD || pFanB == pFanD ) 00200 return Aig_And( p, p0, pFanC ); 00201 if ( pFanA == pFanC || pFanA == pFanD ) 00202 return Aig_And( p, pFanB, p1 ); 00203 } 00204 else if ( Aig_IsComplement(p0) && !Aig_IsComplement(p1) ) 00205 { 00206 if ( pFanA == Aig_Not(pFanC) || pFanA == Aig_Not(pFanD) || pFanB == Aig_Not(pFanC) || pFanB == Aig_Not(pFanD) ) 00207 return p1; 00208 if ( pFanB == pFanC || pFanB == pFanD ) 00209 return Aig_And( p, Aig_Not(pFanA), p1 ); 00210 if ( pFanA == pFanC || pFanA == pFanD ) 00211 return Aig_And( p, Aig_Not(pFanB), p1 ); 00212 } 00213 else if ( !Aig_IsComplement(p0) && Aig_IsComplement(p1) ) 00214 { 00215 if ( pFanC == Aig_Not(pFanA) || pFanC == Aig_Not(pFanB) || pFanD == Aig_Not(pFanA) || pFanD == Aig_Not(pFanB) ) 00216 return p0; 00217 if ( pFanD == pFanA || pFanD == pFanB ) 00218 return Aig_And( p, Aig_Not(pFanC), p0 ); 00219 if ( pFanC == pFanA || pFanC == pFanB ) 00220 return Aig_And( p, Aig_Not(pFanD), p0 ); 00221 } 00222 else // if ( Aig_IsComplement(p0) && Aig_IsComplement(p1) ) 00223 { 00224 if ( pFanA == pFanD && pFanB == Aig_Not(pFanC) ) 00225 return Aig_Not(pFanA); 00226 if ( pFanB == pFanC && pFanA == Aig_Not(pFanD) ) 00227 return Aig_Not(pFanB); 00228 if ( pFanA == pFanC && pFanB == Aig_Not(pFanD) ) 00229 return Aig_Not(pFanA); 00230 if ( pFanB == pFanD && pFanA == Aig_Not(pFanC) ) 00231 return Aig_Not(pFanB); 00232 } 00233 } 00234 // check if it can be an EXOR gate 00235 // if ( Aig_ObjIsExorType( p0, p1, &pFan0, &pFan1 ) ) 00236 // return Aig_Exor( p, pFan0, pFan1 ); 00237 pGhost = Aig_ObjCreateGhost( p, p0, p1, AIG_OBJ_AND ); 00238 pResult = Aig_CanonPair_rec( p, pGhost ); 00239 return pResult; 00240 }

| static int Aig_Base10Log | ( | unsigned | n | ) | [inline, static] |

| static int Aig_Base2Log | ( | unsigned | n | ) | [inline, static] |

| static int Aig_BitWordNum | ( | int | nBits | ) | [inline, static] |

Function*************************************************************

Synopsis [Composes the AIG (pRoot) with the function (pFunc) using PI var (iVar).]

Description []

SideEffects []

SeeAlso []

Definition at line 546 of file aigDfs.c.

00547 { 00548 // quit if the PI variable is not defined 00549 if ( iVar >= Aig_ManPiNum(p) ) 00550 { 00551 printf( "Aig_Compose(): The PI variable %d is not defined.\n", iVar ); 00552 return NULL; 00553 } 00554 // recursively perform composition 00555 Aig_Compose_rec( p, Aig_Regular(pRoot), pFunc, Aig_ManPi(p, iVar) ); 00556 // clear the markings 00557 Aig_ConeUnmark_rec( Aig_Regular(pRoot) ); 00558 return Aig_NotCond( Aig_Regular(pRoot)->pData, Aig_IsComplement(pRoot) ); 00559 }

| void Aig_ConeUnmark_rec | ( | Aig_Obj_t * | pObj | ) |

Function*************************************************************

Synopsis [Counts the number of AIG nodes rooted at this cone.]

Description []

SideEffects []

SeeAlso []

Definition at line 372 of file aigDfs.c.

00373 { 00374 assert( !Aig_IsComplement(pObj) ); 00375 if ( !Aig_ObjIsNode(pObj) || !Aig_ObjIsMarkA(pObj) ) 00376 return; 00377 Aig_ConeUnmark_rec( Aig_ObjFanin0(pObj) ); 00378 Aig_ConeUnmark_rec( Aig_ObjFanin1(pObj) ); 00379 assert( Aig_ObjIsMarkA(pObj) ); // loop detection 00380 Aig_ObjClearMarkA( pObj ); 00381 }

Function*************************************************************

Synopsis [Creates AND function with nVars inputs.]

Description []

SideEffects []

SeeAlso []

Definition at line 476 of file aigOper.c.

00477 { 00478 Aig_Obj_t * pFunc; 00479 int i; 00480 pFunc = Aig_ManConst1( p ); 00481 for ( i = 0; i < nVars; i++ ) 00482 pFunc = Aig_And( p, pFunc, Aig_IthVar(p, i) ); 00483 return pFunc; 00484 }

Function*************************************************************

Synopsis [Creates AND function with nVars inputs.]

Description []

SideEffects []

SeeAlso []

Definition at line 518 of file aigOper.c.

00519 { 00520 Aig_Obj_t * pFunc; 00521 int i; 00522 pFunc = Aig_ManConst0( p ); 00523 for ( i = 0; i < nVars; i++ ) 00524 pFunc = Aig_Exor( p, pFunc, Aig_IthVar(p, i) ); 00525 return pFunc; 00526 }

Function*************************************************************

Synopsis [Creates AND function with nVars inputs.]

Description []

SideEffects []

SeeAlso []

Definition at line 497 of file aigOper.c.

00498 { 00499 Aig_Obj_t * pFunc; 00500 int i; 00501 pFunc = Aig_ManConst0( p ); 00502 for ( i = 0; i < nVars; i++ ) 00503 pFunc = Aig_Or( p, pFunc, Aig_IthVar(p, i) ); 00504 return pFunc; 00505 }

| int Aig_DagSize | ( | Aig_Obj_t * | pObj | ) |

Function*************************************************************

Synopsis [Counts the number of AIG nodes rooted at this cone.]

Description []

SideEffects []

SeeAlso []

Definition at line 394 of file aigDfs.c.

00395 { 00396 int Counter; 00397 Counter = Aig_ConeCountAndMark_rec( Aig_Regular(pObj) ); 00398 Aig_ConeUnmark_rec( Aig_Regular(pObj) ); 00399 return Counter; 00400 }

Function*************************************************************

Synopsis [Performs canonicization step.]

Description [The argument nodes can be complemented.]

SideEffects []

SeeAlso []

Definition at line 274 of file aigOper.c.

00275 { 00276 /* 00277 Aig_Obj_t * pGhost, * pResult; 00278 // check trivial cases 00279 if ( p0 == p1 ) 00280 return Aig_Not(p->pConst1); 00281 if ( p0 == Aig_Not(p1) ) 00282 return p->pConst1; 00283 if ( Aig_Regular(p0) == p->pConst1 ) 00284 return Aig_NotCond( p1, p0 == p->pConst1 ); 00285 if ( Aig_Regular(p1) == p->pConst1 ) 00286 return Aig_NotCond( p0, p1 == p->pConst1 ); 00287 // check the table 00288 pGhost = Aig_ObjCreateGhost( p, p0, p1, AIG_OBJ_EXOR ); 00289 if ( pResult = Aig_TableLookup( p, pGhost ) ) 00290 return pResult; 00291 return Aig_ObjCreate( p, pGhost ); 00292 */ 00293 return Aig_Or( p, Aig_And(p, p0, Aig_Not(p1)), Aig_And(p, Aig_Not(p0), p1) ); 00294 }

| static int Aig_InfoHasBit | ( | unsigned * | p, | |

| int | i | |||

| ) | [inline, static] |

| static unsigned Aig_InfoMask | ( | int | nVar | ) | [inline, static] |

| static void Aig_InfoSetBit | ( | unsigned * | p, | |

| int | i | |||

| ) | [inline, static] |

| static void Aig_InfoXorBit | ( | unsigned * | p, | |

| int | i | |||

| ) | [inline, static] |

| static int Aig_IsComplement | ( | Aig_Obj_t * | p | ) | [inline, static] |

FUNCTION DEFINITIONS ///Function*************************************************************

Synopsis [Returns i-th elementary variable.]

Description []

SideEffects []

SeeAlso []

Definition at line 60 of file aigOper.c.

00061 { 00062 int v; 00063 for ( v = Aig_ManPiNum(p); v <= i; v++ ) 00064 Aig_ObjCreatePi( p ); 00065 assert( i < Vec_PtrSize(p->vPis) ); 00066 return Aig_ManPi( p, i ); 00067 }

Function*************************************************************

Synopsis [Creates the canonical form of the node.]

Description []

SideEffects []

SeeAlso []

Definition at line 253 of file aigOper.c.

00254 { 00255 Aig_Obj_t * pGhost, * pResult; 00256 pGhost = Aig_ObjCreateGhost( p, Aig_NotCond(pObj, fInitOne), NULL, AIG_OBJ_LATCH ); 00257 pResult = Aig_TableLookup( p, pGhost ); 00258 if ( pResult == NULL ) 00259 pResult = Aig_ObjCreate( p, pGhost ); 00260 return Aig_NotCond( pResult, fInitOne ); 00261 }

Function*************************************************************

Synopsis [Implements ITE operation.]

Description []

SideEffects []

SeeAlso []

| static int Aig_ManAndNum | ( | Aig_Man_t * | p | ) | [inline, static] |

Definition at line 187 of file aig.h.

00187 { return p->nObjs[AIG_OBJ_AND]; }

| static int Aig_ManBufNum | ( | Aig_Man_t * | p | ) | [inline, static] |

Definition at line 186 of file aig.h.

00186 { return p->nObjs[AIG_OBJ_BUF]; }

| int Aig_ManCheck | ( | Aig_Man_t * | p | ) |

FUNCTION DECLARATIONS ///

CFile****************************************************************

FileName [aigCheck.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [AIG package.]

Synopsis [AIG checking procedures.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - April 28, 2007.]

Revision [

- Id

- aigCheck.c,v 1.00 2007/04/28 00:00:00 alanmi Exp

] DECLARATIONS /// FUNCTION DEFINITIONS ///Function*************************************************************

Synopsis [Checks the consistency of the AIG manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 42 of file aigCheck.c.

00043 { 00044 Aig_Obj_t * pObj, * pObj2; 00045 int i; 00046 // check primary inputs 00047 Aig_ManForEachPi( p, pObj, i ) 00048 { 00049 if ( Aig_ObjFanin0(pObj) || Aig_ObjFanin1(pObj) ) 00050 { 00051 printf( "Aig_ManCheck: The PI node \"%p\" has fanins.\n", pObj ); 00052 return 0; 00053 } 00054 } 00055 // check primary outputs 00056 Aig_ManForEachPo( p, pObj, i ) 00057 { 00058 if ( !Aig_ObjFanin0(pObj) ) 00059 { 00060 printf( "Aig_ManCheck: The PO node \"%p\" has NULL fanin.\n", pObj ); 00061 return 0; 00062 } 00063 if ( Aig_ObjFanin1(pObj) ) 00064 { 00065 printf( "Aig_ManCheck: The PO node \"%p\" has second fanin.\n", pObj ); 00066 return 0; 00067 } 00068 } 00069 // check internal nodes 00070 Aig_ManForEachObj( p, pObj, i ) 00071 { 00072 if ( !Aig_ObjIsNode(pObj) ) 00073 continue; 00074 if ( !Aig_ObjFanin0(pObj) || !Aig_ObjFanin1(pObj) ) 00075 { 00076 printf( "Aig_ManCheck: The AIG has internal node \"%p\" with a NULL fanin.\n", pObj ); 00077 return 0; 00078 } 00079 if ( Aig_ObjFanin0(pObj)->Id >= Aig_ObjFanin1(pObj)->Id ) 00080 { 00081 printf( "Aig_ManCheck: The AIG has node \"%p\" with a wrong ordering of fanins.\n", pObj ); 00082 return 0; 00083 } 00084 pObj2 = Aig_TableLookup( p, pObj ); 00085 if ( pObj2 != pObj ) 00086 { 00087 printf( "Aig_ManCheck: Node \"%p\" is not in the structural hashing table.\n", pObj ); 00088 return 0; 00089 } 00090 } 00091 // count the total number of nodes 00092 if ( Aig_ManObjNum(p) != 1 + Aig_ManPiNum(p) + Aig_ManPoNum(p) + 00093 Aig_ManBufNum(p) + Aig_ManAndNum(p) + Aig_ManExorNum(p) + Aig_ManLatchNum(p) ) 00094 { 00095 printf( "Aig_ManCheck: The number of created nodes is wrong.\n" ); 00096 printf( "C1 = %d. Pi = %d. Po = %d. Buf = %d. And = %d. Xor = %d. Lat = %d. Total = %d.\n", 00097 1, Aig_ManPiNum(p), Aig_ManPoNum(p), Aig_ManBufNum(p), Aig_ManAndNum(p), Aig_ManExorNum(p), Aig_ManLatchNum(p), 00098 1 + Aig_ManPiNum(p) + Aig_ManPoNum(p) + Aig_ManBufNum(p) + Aig_ManAndNum(p) + Aig_ManExorNum(p) + Aig_ManLatchNum(p) ); 00099 printf( "Created = %d. Deleted = %d. Existing = %d.\n", 00100 p->nCreated, p->nDeleted, p->nCreated - p->nDeleted ); 00101 return 0; 00102 } 00103 // count the number of nodes in the table 00104 if ( Aig_TableCountEntries(p) != Aig_ManAndNum(p) + Aig_ManExorNum(p) + Aig_ManLatchNum(p) ) 00105 { 00106 printf( "Aig_ManCheck: The number of nodes in the structural hashing table is wrong.\n" ); 00107 printf( "Entries = %d. And = %d. Xor = %d. Lat = %d. Total = %d.\n", 00108 Aig_TableCountEntries(p), Aig_ManAndNum(p), Aig_ManExorNum(p), Aig_ManLatchNum(p), 00109 Aig_ManAndNum(p) + Aig_ManExorNum(p) + Aig_ManLatchNum(p) ); 00110 00111 return 0; 00112 } 00113 // if ( !Aig_ManIsAcyclic(p) ) 00114 // return 0; 00115 return 1; 00116 }

| void Aig_ManCheckMarkA | ( | Aig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Checks if the markA is reset.]

Description []

SideEffects []

SeeAlso []

Definition at line 129 of file aigCheck.c.

00130 { 00131 Aig_Obj_t * pObj; 00132 int i; 00133 Aig_ManForEachObj( p, pObj, i ) 00134 assert( pObj->fMarkA == 0 ); 00135 }

| void Aig_ManCheckPhase | ( | Aig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Checks the consistency of phase assignment.]

Description []

SideEffects []

SeeAlso []

Definition at line 148 of file aigCheck.c.

00149 { 00150 Aig_Obj_t * pObj; 00151 int i; 00152 Aig_ManForEachObj( p, pObj, i ) 00153 if ( Aig_ObjIsPi(pObj) ) 00154 assert( (int)pObj->fPhase == 0 ); 00155 else 00156 assert( (int)pObj->fPhase == (Aig_ObjPhaseReal(Aig_ObjChild0(pObj)) & Aig_ObjPhaseReal(Aig_ObjChild1(pObj))) ); 00157 }

Function*************************************************************

Synopsis [Performs partitioned choice computation.]

Description [Assumes that each output in the second AIG cannot have more supp vars than the same output in the first AIG.]

SideEffects []

SeeAlso []

Definition at line 872 of file aigPart.c.

00873 { 00874 extern int Cmd_CommandExecute( void * pAbc, char * sCommand ); 00875 extern void * Abc_FrameGetGlobalFrame(); 00876 extern Aig_Man_t * Fra_FraigChoice( Aig_Man_t * pManAig, int nConfMax ); 00877 00878 Vec_Ptr_t * vOutsTotal, * vOuts; 00879 Aig_Man_t * pAigTotal, * pAigPart, * pAig; 00880 Vec_Int_t * vPart, * vPartSupp; 00881 Vec_Ptr_t * vParts; 00882 Aig_Obj_t * pObj; 00883 void ** ppData; 00884 int i, k, m; 00885 00886 // partition the first AIG in the array 00887 assert( Vec_PtrSize(vAigs) > 1 ); 00888 pAig = Vec_PtrEntry( vAigs, 0 ); 00889 vParts = Aig_ManPartitionSmart( pAig, nPartSize, 0, NULL ); 00890 00891 // start the total fraiged AIG 00892 pAigTotal = Aig_ManStartFrom( pAig ); 00893 Aig_ManReprStart( pAigTotal, Vec_PtrSize(vAigs) * Aig_ManObjNumMax(pAig) + 10000 ); 00894 vOutsTotal = Vec_PtrStart( Aig_ManPoNum(pAig) ); 00895 00896 // set the PI numbers 00897 Vec_PtrForEachEntry( vAigs, pAig, i ) 00898 Aig_ManForEachPi( pAig, pObj, k ) 00899 pObj->pNext = (Aig_Obj_t *)(long)k; 00900 00901 Cmd_CommandExecute( Abc_FrameGetGlobalFrame(), "unset progressbar" ); 00902 00903 // create the total fraiged AIG 00904 vPartSupp = Vec_IntAlloc( 100 ); // maps part PI num into total PI num 00905 Vec_PtrForEachEntry( vParts, vPart, i ) 00906 { 00907 // derive the partition AIG 00908 pAigPart = Aig_ManStart( 5000 ); 00909 // pAigPart->pName = Extra_UtilStrsav( pAigPart->pName ); 00910 Vec_IntClear( vPartSupp ); 00911 Vec_PtrForEachEntry( vAigs, pAig, k ) 00912 { 00913 vOuts = Aig_ManDupPart( pAigPart, pAig, vPart, vPartSupp, 0 ); 00914 if ( k == 0 ) 00915 { 00916 Vec_PtrForEachEntry( vOuts, pObj, m ) 00917 Aig_ObjCreatePo( pAigPart, pObj ); 00918 } 00919 Vec_PtrFree( vOuts ); 00920 } 00921 // derive the total AIG from the partitioned AIG 00922 vOuts = Aig_ManDupPart( pAigTotal, pAigPart, vPart, vPartSupp, 1 ); 00923 // add to the outputs 00924 Vec_PtrForEachEntry( vOuts, pObj, k ) 00925 { 00926 assert( Vec_PtrEntry( vOutsTotal, Vec_IntEntry(vPart,k) ) == NULL ); 00927 Vec_PtrWriteEntry( vOutsTotal, Vec_IntEntry(vPart,k), pObj ); 00928 } 00929 Vec_PtrFree( vOuts ); 00930 // store contents of pData pointers 00931 ppData = ALLOC( void *, Aig_ManObjNumMax(pAigPart) ); 00932 Aig_ManForEachObj( pAigPart, pObj, k ) 00933 ppData[k] = pObj->pData; 00934 // report the process 00935 printf( "Part %4d (out of %4d) PI = %5d. PO = %5d. And = %6d. Lev = %4d.\r", 00936 i+1, Vec_PtrSize(vParts), Aig_ManPiNum(pAigPart), Aig_ManPoNum(pAigPart), 00937 Aig_ManNodeNum(pAigPart), Aig_ManLevelNum(pAigPart) ); 00938 // compute equivalence classes (to be stored in pNew->pReprs) 00939 pAig = Fra_FraigChoice( pAigPart, 1000 ); 00940 Aig_ManStop( pAig ); 00941 // reset the pData pointers 00942 Aig_ManForEachObj( pAigPart, pObj, k ) 00943 pObj->pData = ppData[k]; 00944 free( ppData ); 00945 // transfer representatives to the total AIG 00946 if ( pAigPart->pReprs ) 00947 Aig_ManTransferRepr( pAigTotal, pAigPart ); 00948 Aig_ManStop( pAigPart ); 00949 } 00950 printf( " \r" ); 00951 Vec_VecFree( (Vec_Vec_t *)vParts ); 00952 Vec_IntFree( vPartSupp ); 00953 00954 Cmd_CommandExecute( Abc_FrameGetGlobalFrame(), "set progressbar" ); 00955 00956 // clear the PI numbers 00957 Vec_PtrForEachEntry( vAigs, pAig, i ) 00958 Aig_ManForEachPi( pAig, pObj, k ) 00959 pObj->pNext = NULL; 00960 /* 00961 // collect the missing outputs (outputs whose driver is not a node) 00962 pAig = Vec_PtrEntry( vAigs, 0 ); 00963 Aig_ManConst1(pAig)->pData = Aig_ManConst1(pAigTotal); 00964 Aig_ManForEachPi( pAig, pObj, i ) 00965 pAig->pData = Aig_ManPi( pAigTotal, i ); 00966 Aig_ManForEachPo( pAig, pObj, i ) 00967 if ( !Aig_ObjIsNode(Aig_ObjFanin0(pObj)) ) 00968 { 00969 assert( Vec_PtrEntry( vOutsTotal, i ) == NULL ); 00970 Vec_PtrWriteEntry( vOutsTotal, i, Aig_ObjChild0Copy(pObj) ); 00971 } 00972 */ 00973 // add the outputs in the same order 00974 Vec_PtrForEachEntry( vOutsTotal, pObj, i ) 00975 Aig_ObjCreatePo( pAigTotal, pObj ); 00976 Vec_PtrFree( vOutsTotal ); 00977 00978 // derive the result of choicing 00979 pAig = Aig_ManRehash( pAigTotal ); 00980 // create the equivalent nodes lists 00981 Aig_ManMarkValidChoices( pAig ); 00982 return pAig; 00983 }

| void Aig_ManCleanData | ( | Aig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Cleans the data pointers for the nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 180 of file aigUtil.c.

00181 { 00182 Aig_Obj_t * pObj; 00183 int i; 00184 Aig_ManForEachObj( p, pObj, i ) 00185 pObj->pData = NULL; 00186 }

| void Aig_ManCleanMarkA | ( | Aig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Cleans MarkB.]

Description []

SideEffects []

SeeAlso []

Definition at line 142 of file aigUtil.c.

00143 { 00144 Aig_Obj_t * pObj; 00145 int i; 00146 Aig_ManForEachObj( p, pObj, i ) 00147 pObj->fMarkA = 0; 00148 }

| void Aig_ManCleanMarkB | ( | Aig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Cleans MarkB.]

Description []

SideEffects []

SeeAlso []

Definition at line 161 of file aigUtil.c.

00162 { 00163 Aig_Obj_t * pObj; 00164 int i; 00165 Aig_ManForEachObj( p, pObj, i ) 00166 pObj->fMarkB = 0; 00167 }

| int Aig_ManCleanup | ( | Aig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Returns the number of dangling nodes removed.]

Description []

SideEffects []

SeeAlso []

Definition at line 273 of file aigMan.c.

00274 { 00275 Vec_Ptr_t * vObjs; 00276 Aig_Obj_t * pNode; 00277 int i, nNodesOld; 00278 nNodesOld = Aig_ManNodeNum(p); 00279 // collect roots of dangling nodes 00280 vObjs = Vec_PtrAlloc( 100 ); 00281 Aig_ManForEachObj( p, pNode, i ) 00282 if ( Aig_ObjIsNode(pNode) && Aig_ObjRefs(pNode) == 0 ) 00283 Vec_PtrPush( vObjs, pNode ); 00284 // recursively remove dangling nodes 00285 Vec_PtrForEachEntry( vObjs, pNode, i ) 00286 Aig_ObjDelete_rec( p, pNode, 1 ); 00287 Vec_PtrFree( vObjs ); 00288 return nNodesOld - Aig_ManNodeNum(p); 00289 }

Function*************************************************************

Synopsis [Reduces the circuit using ternary simulation.]

Description []

SideEffects []

SeeAlso []

Definition at line 414 of file aigTsim.c.

00415 { 00416 Aig_Man_t * pTemp; 00417 Vec_Ptr_t * vMap; 00418 while ( (vMap = Aig_ManTernarySimulate( p, fVerbose )) ) 00419 { 00420 if ( fVerbose ) 00421 printf( "RBeg = %5d. NBeg = %6d. ", Aig_ManRegNum(p), Aig_ManNodeNum(p) ); 00422 p = Aig_ManRemap( pTemp = p, vMap ); 00423 Aig_ManStop( pTemp ); 00424 Vec_PtrFree( vMap ); 00425 Aig_ManSeqCleanup( p ); 00426 if ( fVerbose ) 00427 printf( "REnd = %5d. NEnd = %6d. \n", Aig_ManRegNum(p), Aig_ManNodeNum(p) ); 00428 } 00429 return p; 00430 }

| int Aig_ManCountLevels | ( | Aig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Computes the max number of levels in the manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 267 of file aigDfs.c.

00268 { 00269 Vec_Ptr_t * vNodes; 00270 Aig_Obj_t * pObj; 00271 int i, LevelsMax, Level0, Level1; 00272 // initialize the levels 00273 Aig_ManConst1(p)->iData = 0; 00274 Aig_ManForEachPi( p, pObj, i ) 00275 pObj->iData = 0; 00276 // compute levels in a DFS order 00277 vNodes = Aig_ManDfs( p ); 00278 Vec_PtrForEachEntry( vNodes, pObj, i ) 00279 { 00280 Level0 = Aig_ObjFanin0(pObj)->iData; 00281 Level1 = Aig_ObjFanin1(pObj)->iData; 00282 pObj->iData = 1 + Aig_ObjIsExor(pObj) + AIG_MAX(Level0, Level1); 00283 } 00284 Vec_PtrFree( vNodes ); 00285 // get levels of the POs 00286 LevelsMax = 0; 00287 Aig_ManForEachPo( p, pObj, i ) 00288 LevelsMax = AIG_MAX( LevelsMax, Aig_ObjFanin0(pObj)->iData ); 00289 return LevelsMax; 00290 }

| int Aig_ManCountMergeRegs | ( | Aig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Returns the number of dangling nodes removed.]

Description []

SideEffects []

SeeAlso []

Definition at line 221 of file aigScl.c.

00222 { 00223 Aig_Obj_t * pObj, * pFanin; 00224 int i, Counter = 0, Const0 = 0, Const1 = 0; 00225 Aig_ManIncrementTravId( p ); 00226 Aig_ManForEachLiSeq( p, pObj, i ) 00227 { 00228 pFanin = Aig_ObjFanin0(pObj); 00229 if ( Aig_ObjIsConst1(pFanin) ) 00230 { 00231 if ( Aig_ObjFaninC0(pObj) ) 00232 Const0++; 00233 else 00234 Const1++; 00235 } 00236 if ( Aig_ObjIsTravIdCurrent(p, pFanin) ) 00237 continue; 00238 Aig_ObjSetTravIdCurrent(p, pFanin); 00239 Counter++; 00240 } 00241 printf( "Regs = %d. Fanins = %d. Const0 = %d. Const1 = %d.\n", 00242 Aig_ManRegNum(p), Counter, Const0, Const1 ); 00243 return 0; 00244 }

| unsigned* Aig_ManCutTruth | ( | Aig_Obj_t * | pRoot, | |

| Vec_Ptr_t * | vLeaves, | |||

| Vec_Ptr_t * | vNodes, | |||

| Vec_Ptr_t * | vTruthElem, | |||

| Vec_Ptr_t * | vTruthStore | |||

| ) |

Function*************************************************************

Synopsis [Computes truth table of the cut.]

Description [The returned pointer should be used immediately.]

SideEffects []

SeeAlso []

Definition at line 77 of file aigTruth.c.

00078 { 00079 Aig_Obj_t * pObj; 00080 int i, nWords; 00081 assert( Vec_PtrSize(vLeaves) <= Vec_PtrSize(vTruthElem) ); 00082 assert( Vec_PtrSize(vNodes) <= Vec_PtrSize(vTruthStore) ); 00083 assert( Vec_PtrSize(vNodes) == 0 || pRoot == Vec_PtrEntryLast(vNodes) ); 00084 // assign elementary truth tables 00085 Vec_PtrForEachEntry( vLeaves, pObj, i ) 00086 pObj->pData = Vec_PtrEntry( vTruthElem, i ); 00087 // compute truths for other nodes 00088 nWords = Aig_TruthWordNum( Vec_PtrSize(vLeaves) ); 00089 Vec_PtrForEachEntry( vNodes, pObj, i ) 00090 pObj->pData = Aig_ManCutTruthOne( pObj, Vec_PtrEntry(vTruthStore, i), nWords ); 00091 return pRoot->pData; 00092 }

Function*************************************************************

Synopsis [Collects internal nodes in the DFS order.]

Description []

SideEffects []

SeeAlso []

Definition at line 68 of file aigDfs.c.

00069 { 00070 Vec_Ptr_t * vNodes; 00071 Aig_Obj_t * pObj; 00072 int i; 00073 Aig_ManIncrementTravId( p ); 00074 // mark constant and PIs 00075 Aig_ObjSetTravIdCurrent( p, Aig_ManConst1(p) ); 00076 Aig_ManForEachPi( p, pObj, i ) 00077 Aig_ObjSetTravIdCurrent( p, pObj ); 00078 // if there are latches, mark them 00079 if ( Aig_ManLatchNum(p) > 0 ) 00080 Aig_ManForEachObj( p, pObj, i ) 00081 if ( Aig_ObjIsLatch(pObj) ) 00082 Aig_ObjSetTravIdCurrent( p, pObj ); 00083 // go through the nodes 00084 vNodes = Vec_PtrAlloc( Aig_ManNodeNum(p) ); 00085 Aig_ManForEachObj( p, pObj, i ) 00086 if ( Aig_ObjIsNode(pObj) || Aig_ObjIsBuf(pObj) ) 00087 Aig_ManDfs_rec( p, pObj, vNodes ); 00088 return vNodes; 00089 }

Function*************************************************************

Synopsis [Collects internal nodes in the DFS order.]

Description []

SideEffects []

SeeAlso []

Definition at line 158 of file aigDfs.c.

00159 { 00160 Vec_Ptr_t * vNodes; 00161 Aig_Obj_t * pObj; 00162 int i; 00163 assert( p->pEquivs != NULL ); 00164 Aig_ManIncrementTravId( p ); 00165 // mark constant and PIs 00166 Aig_ObjSetTravIdCurrent( p, Aig_ManConst1(p) ); 00167 Aig_ManForEachPi( p, pObj, i ) 00168 Aig_ObjSetTravIdCurrent( p, pObj ); 00169 // go through the nodes 00170 vNodes = Vec_PtrAlloc( Aig_ManNodeNum(p) ); 00171 Aig_ManForEachPo( p, pObj, i ) 00172 Aig_ManDfsChoices_rec( p, Aig_ObjFanin0(pObj), vNodes ); 00173 return vNodes; 00174 }

Function*************************************************************

Synopsis [Collects internal nodes in the DFS order.]

Description []

SideEffects []

SeeAlso []

Definition at line 102 of file aigDfs.c.

00103 { 00104 Vec_Ptr_t * vNodes; 00105 Aig_Obj_t * pObj; 00106 int i; 00107 assert( Aig_ManLatchNum(p) == 0 ); 00108 Aig_ManIncrementTravId( p ); 00109 // mark constant and PIs 00110 Aig_ObjSetTravIdCurrent( p, Aig_ManConst1(p) ); 00111 Aig_ManForEachPi( p, pObj, i ) 00112 Aig_ObjSetTravIdCurrent( p, pObj ); 00113 // go through the nodes 00114 vNodes = Vec_PtrAlloc( Aig_ManNodeNum(p) ); 00115 for ( i = 0; i < nNodes; i++ ) 00116 Aig_ManDfs_rec( p, ppNodes[i], vNodes ); 00117 return vNodes; 00118 }

Function*************************************************************

Synopsis [Collects internal nodes in the reverse DFS order.]

Description []

SideEffects []

SeeAlso []

Definition at line 213 of file aigDfs.c.

00214 { 00215 Vec_Ptr_t * vNodes; 00216 Aig_Obj_t * pObj; 00217 int i; 00218 Aig_ManIncrementTravId( p ); 00219 // mark POs 00220 Aig_ManForEachPo( p, pObj, i ) 00221 Aig_ObjSetTravIdCurrent( p, pObj ); 00222 // if there are latches, mark them 00223 if ( Aig_ManLatchNum(p) > 0 ) 00224 Aig_ManForEachObj( p, pObj, i ) 00225 if ( Aig_ObjIsLatch(pObj) ) 00226 Aig_ObjSetTravIdCurrent( p, pObj ); 00227 // go through the nodes 00228 vNodes = Vec_PtrAlloc( Aig_ManNodeNum(p) ); 00229 Aig_ManForEachObj( p, pObj, i ) 00230 if ( Aig_ObjIsNode(pObj) || Aig_ObjIsBuf(pObj) ) 00231 Aig_ManDfsReverse_rec( p, pObj, vNodes ); 00232 return vNodes; 00233 }

| void Aig_ManDump | ( | Aig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Write speculative miter for one node.]

Description []

SideEffects []

SeeAlso []

Definition at line 640 of file aigUtil.c.

00641 { 00642 static int Counter = 0; 00643 char FileName[20]; 00644 // dump the logic into a file 00645 sprintf( FileName, "aigbug\\%03d.blif", ++Counter ); 00646 Aig_ManDumpBlif( p, FileName ); 00647 printf( "Intermediate AIG with %d nodes was written into file \"%s\".\n", Aig_ManNodeNum(p), FileName ); 00648 }

| void Aig_ManDumpBlif | ( | Aig_Man_t * | p, | |

| char * | pFileName | |||

| ) |

Function*************************************************************

Synopsis [Writes the AIG into the BLIF file.]

Description []

SideEffects []

SeeAlso []

Definition at line 661 of file aigUtil.c.

00662 { 00663 FILE * pFile; 00664 Vec_Ptr_t * vNodes; 00665 Aig_Obj_t * pObj, * pObjLi, * pObjLo, * pConst1 = NULL; 00666 int i, nDigits, Counter = 0; 00667 if ( Aig_ManPoNum(p) == 0 ) 00668 { 00669 printf( "Aig_ManDumpBlif(): AIG manager does not have POs.\n" ); 00670 return; 00671 } 00672 // collect nodes in the DFS order 00673 vNodes = Aig_ManDfs( p ); 00674 // assign IDs to objects 00675 Aig_ManConst1(p)->iData = Counter++; 00676 Aig_ManForEachPi( p, pObj, i ) 00677 pObj->iData = Counter++; 00678 Aig_ManForEachPo( p, pObj, i ) 00679 pObj->iData = Counter++; 00680 Vec_PtrForEachEntry( vNodes, pObj, i ) 00681 pObj->iData = Counter++; 00682 nDigits = Aig_Base10Log( Counter ); 00683 // write the file 00684 pFile = fopen( pFileName, "w" ); 00685 fprintf( pFile, "# BLIF file written by procedure Aig_ManDumpBlif()\n" ); 00686 // fprintf( pFile, "# http://www.eecs.berkeley.edu/~alanmi/abc/\n" ); 00687 fprintf( pFile, ".model test\n" ); 00688 // write PIs 00689 fprintf( pFile, ".inputs" ); 00690 Aig_ManForEachPiSeq( p, pObj, i ) 00691 fprintf( pFile, " n%0*d", nDigits, pObj->iData ); 00692 fprintf( pFile, "\n" ); 00693 // write POs 00694 fprintf( pFile, ".outputs" ); 00695 Aig_ManForEachPoSeq( p, pObj, i ) 00696 fprintf( pFile, " n%0*d", nDigits, pObj->iData ); 00697 fprintf( pFile, "\n" ); 00698 // write latches 00699 if ( Aig_ManRegNum(p) ) 00700 { 00701 fprintf( pFile, "\n" ); 00702 Aig_ManForEachLiLoSeq( p, pObjLi, pObjLo, i ) 00703 fprintf( pFile, ".latch n%0*d n%0*d 0\n", nDigits, pObjLi->iData, nDigits, pObjLo->iData ); 00704 fprintf( pFile, "\n" ); 00705 } 00706 // write nodes 00707 Vec_PtrForEachEntry( vNodes, pObj, i ) 00708 { 00709 fprintf( pFile, ".names n%0*d n%0*d n%0*d\n", 00710 nDigits, Aig_ObjFanin0(pObj)->iData, 00711 nDigits, Aig_ObjFanin1(pObj)->iData, 00712 nDigits, pObj->iData ); 00713 fprintf( pFile, "%d%d 1\n", !Aig_ObjFaninC0(pObj), !Aig_ObjFaninC1(pObj) ); 00714 } 00715 // write POs 00716 Aig_ManForEachPo( p, pObj, i ) 00717 { 00718 fprintf( pFile, ".names n%0*d n%0*d\n", 00719 nDigits, Aig_ObjFanin0(pObj)->iData, 00720 nDigits, pObj->iData ); 00721 fprintf( pFile, "%d 1\n", !Aig_ObjFaninC0(pObj) ); 00722 if ( Aig_ObjIsConst1(Aig_ObjFanin0(pObj)) ) 00723 pConst1 = Aig_ManConst1(p); 00724 } 00725 if ( pConst1 ) 00726 fprintf( pFile, ".names n%0*d\n 1\n", nDigits, pConst1->iData ); 00727 fprintf( pFile, ".end\n\n" ); 00728 fclose( pFile ); 00729 Vec_PtrFree( vNodes ); 00730 }

| void Aig_ManDumpVerilog | ( | Aig_Man_t * | p, | |

| char * | pFileName | |||

| ) |

Function*************************************************************

Synopsis [Writes the AIG into the BLIF file.]

Description []

SideEffects []

SeeAlso []

Definition at line 743 of file aigUtil.c.

00744 { 00745 FILE * pFile; 00746 Vec_Ptr_t * vNodes; 00747 Aig_Obj_t * pObj, * pObjLi, * pObjLo, * pConst1 = NULL; 00748 int i, nDigits, Counter = 0; 00749 if ( Aig_ManPoNum(p) == 0 ) 00750 { 00751 printf( "Aig_ManDumpBlif(): AIG manager does not have POs.\n" ); 00752 return; 00753 } 00754 // collect nodes in the DFS order 00755 vNodes = Aig_ManDfs( p ); 00756 // assign IDs to objects 00757 Aig_ManConst1(p)->iData = Counter++; 00758 Aig_ManForEachPi( p, pObj, i ) 00759 pObj->iData = Counter++; 00760 Aig_ManForEachPo( p, pObj, i ) 00761 pObj->iData = Counter++; 00762 Vec_PtrForEachEntry( vNodes, pObj, i ) 00763 pObj->iData = Counter++; 00764 nDigits = Aig_Base10Log( Counter ); 00765 // write the file 00766 pFile = fopen( pFileName, "w" ); 00767 fprintf( pFile, "// Verilog file written by procedure Aig_ManDumpVerilog()\n" ); 00768 // fprintf( pFile, "// http://www.eecs.berkeley.edu/~alanmi/abc/\n" ); 00769 if ( Aig_ManRegNum(p) ) 00770 fprintf( pFile, "module %s ( clock", p->pName? p->pName: "test" ); 00771 else 00772 fprintf( pFile, "module %s (", p->pName? p->pName: "test" ); 00773 Aig_ManForEachPiSeq( p, pObj, i ) 00774 fprintf( pFile, "%s n%0*d", ((Aig_ManRegNum(p) || i)? ",":""), nDigits, pObj->iData ); 00775 Aig_ManForEachPoSeq( p, pObj, i ) 00776 fprintf( pFile, ", n%0*d", nDigits, pObj->iData ); 00777 fprintf( pFile, " );\n" ); 00778 00779 // write PIs 00780 if ( Aig_ManRegNum(p) ) 00781 fprintf( pFile, "input clock;\n" ); 00782 Aig_ManForEachPiSeq( p, pObj, i ) 00783 fprintf( pFile, "input n%0*d;\n", nDigits, pObj->iData ); 00784 // write POs 00785 Aig_ManForEachPoSeq( p, pObj, i ) 00786 fprintf( pFile, "output n%0*d;\n", nDigits, pObj->iData ); 00787 // write latches 00788 if ( Aig_ManRegNum(p) ) 00789 { 00790 Aig_ManForEachLiLoSeq( p, pObjLi, pObjLo, i ) 00791 fprintf( pFile, "reg n%0*d;\n", nDigits, pObjLo->iData ); 00792 Aig_ManForEachLiLoSeq( p, pObjLi, pObjLo, i ) 00793 fprintf( pFile, "wire n%0*d;\n", nDigits, pObjLi->iData ); 00794 } 00795 // write nodes 00796 Vec_PtrForEachEntry( vNodes, pObj, i ) 00797 fprintf( pFile, "wire n%0*d;\n", nDigits, pObj->iData ); 00798 // write nodes 00799 Vec_PtrForEachEntry( vNodes, pObj, i ) 00800 { 00801 fprintf( pFile, "assign n%0*d = %sn%0*d & %sn%0*d;\n", 00802 nDigits, pObj->iData, 00803 !Aig_ObjFaninC0(pObj) ? " " : "~", nDigits, Aig_ObjFanin0(pObj)->iData, 00804 !Aig_ObjFaninC1(pObj) ? " " : "~", nDigits, Aig_ObjFanin1(pObj)->iData 00805 ); 00806 } 00807 // write POs 00808 Aig_ManForEachPoSeq( p, pObj, i ) 00809 { 00810 fprintf( pFile, "assign n%0*d = %sn%0*d;\n", 00811 nDigits, pObj->iData, 00812 !Aig_ObjFaninC0(pObj) ? " " : "~", nDigits, Aig_ObjFanin0(pObj)->iData ); 00813 if ( Aig_ObjIsConst1(Aig_ObjFanin0(pObj)) ) 00814 pConst1 = Aig_ManConst1(p); 00815 } 00816 if ( Aig_ManRegNum(p) ) 00817 { 00818 Aig_ManForEachLiLoSeq( p, pObjLi, pObjLo, i ) 00819 { 00820 fprintf( pFile, "assign n%0*d = %sn%0*d;\n", 00821 nDigits, pObjLi->iData, 00822 !Aig_ObjFaninC0(pObjLi) ? " " : "~", nDigits, Aig_ObjFanin0(pObjLi)->iData ); 00823 if ( Aig_ObjIsConst1(Aig_ObjFanin0(pObjLi)) ) 00824 pConst1 = Aig_ManConst1(p); 00825 } 00826 } 00827 if ( pConst1 ) 00828 fprintf( pFile, "assign n%0*d = 1\'b1;\n", nDigits, pConst1->iData ); 00829 00830 // write initial state 00831 if ( Aig_ManRegNum(p) ) 00832 { 00833 Aig_ManForEachLiLoSeq( p, pObjLi, pObjLo, i ) 00834 fprintf( pFile, "always @ (posedge clock) begin n%0*d <= n%0*d; end\n", 00835 nDigits, pObjLo->iData, 00836 nDigits, pObjLi->iData ); 00837 Aig_ManForEachLiLoSeq( p, pObjLi, pObjLo, i ) 00838 fprintf( pFile, "initial begin n%0*d <= 1\'b0; end\n", 00839 nDigits, pObjLo->iData ); 00840 } 00841 00842 fprintf( pFile, "endmodule\n\n" ); 00843 fclose( pFile ); 00844 Vec_PtrFree( vNodes ); 00845 }

Function*************************************************************

Synopsis [Duplicates the AIG manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 132 of file aigMan.c.

00133 { 00134 Aig_Man_t * pNew; 00135 Aig_Obj_t * pObj; 00136 int i; 00137 // create the new manager 00138 pNew = Aig_ManStart( Aig_ManObjNumMax(p) ); 00139 pNew->pName = Aig_UtilStrsav( p->pName ); 00140 pNew->nRegs = p->nRegs; 00141 pNew->nAsserts = p->nAsserts; 00142 if ( p->vFlopNums ) 00143 pNew->vFlopNums = Vec_IntDup( p->vFlopNums ); 00144 // create the PIs 00145 Aig_ManCleanData( p ); 00146 Aig_ManConst1(p)->pData = Aig_ManConst1(pNew); 00147 Aig_ManForEachPi( p, pObj, i ) 00148 pObj->pData = Aig_ObjCreatePi(pNew); 00149 // duplicate internal nodes 00150 if ( fOrdered ) 00151 { 00152 Aig_ManForEachObj( p, pObj, i ) 00153 if ( Aig_ObjIsBuf(pObj) ) 00154 pObj->pData = Aig_ObjChild0Copy(pObj); 00155 else if ( Aig_ObjIsNode(pObj) ) 00156 pObj->pData = Aig_And( pNew, Aig_ObjChild0Copy(pObj), Aig_ObjChild1Copy(pObj) ); 00157 } 00158 else 00159 { 00160 Aig_ManForEachObj( p, pObj, i ) 00161 if ( !Aig_ObjIsPo(pObj) ) 00162 { 00163 Aig_ManDup_rec( pNew, p, pObj ); 00164 assert( pObj->Level == ((Aig_Obj_t*)pObj->pData)->Level ); 00165 } 00166 } 00167 // add the POs 00168 Aig_ManForEachPo( p, pObj, i ) 00169 Aig_ObjCreatePo( pNew, Aig_ObjChild0Copy(pObj) ); 00170 assert( Aig_ManBufNum(p) != 0 || Aig_ManNodeNum(p) == Aig_ManNodeNum(pNew) ); 00171 // check the resulting network 00172 if ( !Aig_ManCheck(pNew) ) 00173 printf( "Aig_ManDup(): The check has failed.\n" ); 00174 return pNew; 00175 }

Function*************************************************************

Synopsis [Duplicates the AIG manager recursively.]

Description []

SideEffects []

SeeAlso []

Definition at line 110 of file aigMan.c.

00111 { 00112 if ( pObj->pData ) 00113 return pObj->pData; 00114 Aig_ManDup_rec( pNew, p, Aig_ObjFanin0(pObj) ); 00115 if ( Aig_ObjIsBuf(pObj) ) 00116 return pObj->pData = Aig_ObjChild0Copy(pObj); 00117 Aig_ManDup_rec( pNew, p, Aig_ObjFanin1(pObj) ); 00118 return pObj->pData = Aig_And( pNew, Aig_ObjChild0Copy(pObj), Aig_ObjChild1Copy(pObj) ); 00119 }

Function*************************************************************

Synopsis [Duplicates AIG while substituting representatives.]

Description []

SideEffects []

SeeAlso []

Definition at line 264 of file aigRepr.c.

00265 { 00266 Aig_Man_t * pNew; 00267 Aig_Obj_t * pObj; 00268 int i; 00269 // start the HOP package 00270 pNew = Aig_ManStart( Aig_ManObjNumMax(p) ); 00271 pNew->pName = Aig_UtilStrsav( p->pName ); 00272 pNew->nRegs = p->nRegs; 00273 if ( p->vFlopNums ) 00274 pNew->vFlopNums = Vec_IntDup( p->vFlopNums ); 00275 // map the const and primary inputs 00276 Aig_ManCleanData( p ); 00277 Aig_ManConst1(p)->pData = Aig_ManConst1(pNew); 00278 Aig_ManForEachPi( p, pObj, i ) 00279 pObj->pData = Aig_ObjCreatePi(pNew); 00280 // map the internal nodes 00281 if ( fOrdered ) 00282 { 00283 Aig_ManForEachNode( p, pObj, i ) 00284 pObj->pData = Aig_And( pNew, Aig_ObjChild0Repr(p, pObj), Aig_ObjChild1Repr(p, pObj) ); 00285 } 00286 else 00287 { 00288 Aig_ManForEachPo( p, pObj, i ) 00289 Aig_ManDupRepr_rec( pNew, p, Aig_ObjFanin0(pObj) ); 00290 } 00291 // transfer the POs 00292 Aig_ManForEachPo( p, pObj, i ) 00293 Aig_ObjCreatePo( pNew, Aig_ObjChild0Repr(p, pObj) ); 00294 // check the new manager 00295 if ( !Aig_ManCheck(pNew) ) 00296 printf( "Aig_ManDupRepr: Check has failed.\n" ); 00297 return pNew; 00298 }

| static int Aig_ManExorNum | ( | Aig_Man_t * | p | ) | [inline, static] |

Definition at line 188 of file aig.h.

00188 { return p->nObjs[AIG_OBJ_EXOR]; }

Function*************************************************************

Synopsis [Extracts the miter composed of XOR of the two nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 188 of file aigMan.c.

00189 { 00190 Aig_Man_t * pNew; 00191 Aig_Obj_t * pObj; 00192 int i; 00193 // create the new manager 00194 pNew = Aig_ManStart( Aig_ManObjNumMax(p) ); 00195 pNew->pName = Aig_UtilStrsav( p->pName ); 00196 // create the PIs 00197 Aig_ManCleanData( p ); 00198 Aig_ManConst1(p)->pData = Aig_ManConst1(pNew); 00199 Aig_ManForEachPi( p, pObj, i ) 00200 pObj->pData = Aig_ObjCreatePi(pNew); 00201 // dump the nodes 00202 Aig_ManDup_rec( pNew, p, pNode1 ); 00203 Aig_ManDup_rec( pNew, p, pNode2 ); 00204 // construct the EXOR 00205 pObj = Aig_Exor( pNew, pNode1->pData, pNode2->pData ); 00206 pObj = Aig_NotCond( pObj, Aig_Regular(pObj)->fPhase ^ Aig_IsComplement(pObj) ); 00207 // add the PO 00208 Aig_ObjCreatePo( pNew, pObj ); 00209 // check the resulting network 00210 if ( !Aig_ManCheck(pNew) ) 00211 printf( "Aig_ManDup(): The check has failed.\n" ); 00212 return pNew; 00213 }

| void Aig_ManFanoutStart | ( | Aig_Man_t * | p | ) |

FUNCTION DEFINITIONS ///Function*************************************************************

Synopsis [Create fanout for all objects in the manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 53 of file aigFanout.c.

00054 { 00055 Aig_Obj_t * pObj; 00056 int i; 00057 assert( Aig_ManBufNum(p) == 0 ); 00058 // allocate fanout datastructure 00059 assert( p->pFanData == NULL ); 00060 p->nFansAlloc = 2 * Aig_ManObjNumMax(p); 00061 if ( p->nFansAlloc < (1<<12) ) 00062 p->nFansAlloc = (1<<12); 00063 p->pFanData = ALLOC( int, 5 * p->nFansAlloc ); 00064 memset( p->pFanData, 0, sizeof(int) * 5 * p->nFansAlloc ); 00065 // add fanouts for all objects 00066 Aig_ManForEachObj( p, pObj, i ) 00067 { 00068 if ( Aig_ObjChild0(pObj) ) 00069 Aig_ObjAddFanout( p, Aig_ObjFanin0(pObj), pObj ); 00070 if ( Aig_ObjChild1(pObj) ) 00071 Aig_ObjAddFanout( p, Aig_ObjFanin1(pObj), pObj ); 00072 } 00073 }

| void Aig_ManFanoutStop | ( | Aig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Deletes fanout for all objects in the manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 86 of file aigFanout.c.

Definition at line 286 of file aig.h.

00287 { 00288 extern char * Aig_MmFixedEntryFetch( Aig_MmFixed_t * p ); 00289 Aig_Obj_t * pTemp; 00290 pTemp = (Aig_Obj_t *)Aig_MmFixedEntryFetch( p->pMemObjs ); 00291 memset( pTemp, 0, sizeof(Aig_Obj_t) ); 00292 Vec_PtrPush( p->vObjs, pTemp ); 00293 pTemp->Id = p->nCreated++; 00294 return pTemp; 00295 }

| void Aig_ManFindCut | ( | Aig_Obj_t * | pRoot, | |

| Vec_Ptr_t * | vFront, | |||

| Vec_Ptr_t * | vVisited, | |||

| int | nSizeLimit, | |||

| int | nFanoutLimit | |||

| ) |

Function*************************************************************

Synopsis [Computes one sequential cut of the given size.]

Description []

SideEffects []

SeeAlso []

Definition at line 142 of file aigWin.c.

00143 { 00144 Aig_Obj_t * pNode; 00145 int i; 00146 00147 assert( !Aig_IsComplement(pRoot) ); 00148 assert( Aig_ObjIsNode(pRoot) ); 00149 assert( Aig_ObjChild0(pRoot) ); 00150 assert( Aig_ObjChild1(pRoot) ); 00151 00152 // start the cut 00153 Vec_PtrClear( vFront ); 00154 Vec_PtrPush( vFront, Aig_ObjFanin0(pRoot) ); 00155 Vec_PtrPush( vFront, Aig_ObjFanin1(pRoot) ); 00156 00157 // start the visited nodes 00158 Vec_PtrClear( vVisited ); 00159 Vec_PtrPush( vVisited, pRoot ); 00160 Vec_PtrPush( vVisited, Aig_ObjFanin0(pRoot) ); 00161 Vec_PtrPush( vVisited, Aig_ObjFanin1(pRoot) ); 00162 00163 // mark these nodes 00164 assert( !pRoot->fMarkA ); 00165 assert( !Aig_ObjFanin0(pRoot)->fMarkA ); 00166 assert( !Aig_ObjFanin1(pRoot)->fMarkA ); 00167 pRoot->fMarkA = 1; 00168 Aig_ObjFanin0(pRoot)->fMarkA = 1; 00169 Aig_ObjFanin1(pRoot)->fMarkA = 1; 00170 00171 // compute the cut 00172 while ( Aig_ManFindCut_int( vFront, vVisited, nSizeLimit, nFanoutLimit ) ); 00173 assert( Vec_PtrSize(vFront) <= nSizeLimit ); 00174 00175 // clean the visit markings 00176 Vec_PtrForEachEntry( vVisited, pNode, i ) 00177 pNode->fMarkA = 0; 00178 }

| static int Aig_ManGetCost | ( | Aig_Man_t * | p | ) | [inline, static] |

Definition at line 191 of file aig.h.

00191 { return p->nObjs[AIG_OBJ_AND]+3*p->nObjs[AIG_OBJ_EXOR]; }

| void Aig_ManIncrementTravId | ( | Aig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Increments the current traversal ID of the network.]

Description []

SideEffects []

SeeAlso []

Definition at line 78 of file aigUtil.c.

00079 { 00080 if ( p->nTravIds >= (1<<30)-1 ) 00081 Aig_ManCleanData( p ); 00082 p->nTravIds++; 00083 }

| static int Aig_ManLatchNum | ( | Aig_Man_t * | p | ) | [inline, static] |

Definition at line 189 of file aig.h.

00189 { return p->nObjs[AIG_OBJ_LATCH]; }

| int Aig_ManLevelNum | ( | Aig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Computes the max number of levels in the manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 246 of file aigDfs.c.

00247 { 00248 Aig_Obj_t * pObj; 00249 int i, LevelsMax; 00250 LevelsMax = 0; 00251 Aig_ManForEachPo( p, pObj, i ) 00252 LevelsMax = AIG_MAX( LevelsMax, (int)Aig_ObjFanin0(pObj)->Level ); 00253 return LevelsMax; 00254 }

| int Aig_ManLevels | ( | Aig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Collect the latches.]

Description []

SideEffects []

SeeAlso []

Definition at line 96 of file aigUtil.c.

00097 { 00098 Aig_Obj_t * pObj; 00099 int i, LevelMax = 0; 00100 Aig_ManForEachPo( p, pObj, i ) 00101 LevelMax = AIG_MAX( LevelMax, (int)Aig_ObjFanin0(pObj)->Level ); 00102 return LevelMax; 00103 }

Definition at line 202 of file aig.h.

00202 { return (Aig_Obj_t *)Vec_PtrEntry(p->vPos, Aig_ManPoNum(p)-Aig_ManRegNum(p)+i); }

Definition at line 201 of file aig.h.

00201 { return (Aig_Obj_t *)Vec_PtrEntry(p->vPis, Aig_ManPiNum(p)-Aig_ManRegNum(p)+i); }

| void Aig_ManMarkValidChoices | ( | Aig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Marks the nodes that are Creates choices.]

Description [The input AIG is assumed to have representatives assigned.]

SideEffects []

SeeAlso []

Definition at line 417 of file aigRepr.c.

00418 { 00419 Aig_Obj_t * pObj, * pRepr; 00420 int i; 00421 assert( p->pReprs != NULL ); 00422 // create equivalent nodes in the manager 00423 assert( p->pEquivs == NULL ); 00424 p->pEquivs = ALLOC( Aig_Obj_t *, Aig_ManObjNumMax(p) ); 00425 memset( p->pEquivs, 0, sizeof(Aig_Obj_t *) * Aig_ManObjNumMax(p) ); 00426 // make the choice nodes 00427 Aig_ManForEachNode( p, pObj, i ) 00428 { 00429 pRepr = Aig_ObjFindRepr( p, pObj ); 00430 if ( pRepr == NULL ) 00431 continue; 00432 assert( pObj->nRefs == 0 ); 00433 // skip constant and PI classes 00434 if ( !Aig_ObjIsNode(pRepr) ) 00435 { 00436 Aig_ObjClearRepr( p, pObj ); 00437 continue; 00438 } 00439 // skip choices with combinatinal loops 00440 if ( Aig_ObjCheckTfi( p, pObj, pRepr ) ) 00441 { 00442 Aig_ObjClearRepr( p, pObj ); 00443 continue; 00444 } 00445 //printf( "Node %d is represented by node %d.\n", pObj->Id, pRepr->Id ); 00446 // add choice to the choice node 00447 p->pEquivs[pObj->Id] = p->pEquivs[pRepr->Id]; 00448 p->pEquivs[pRepr->Id] = pObj; 00449 } 00450 }

| static int Aig_ManNodeNum | ( | Aig_Man_t * | p | ) | [inline, static] |

Definition at line 190 of file aig.h.

00190 { return p->nObjs[AIG_OBJ_AND]+p->nObjs[AIG_OBJ_EXOR]; }

| static int Aig_ManObjNum | ( | Aig_Man_t * | p | ) | [inline, static] |

| static int Aig_ManObjNumMax | ( | Aig_Man_t * | p | ) | [inline, static] |

Definition at line 193 of file aig.h.

00193 { return Vec_PtrSize(p->vObjs); }

| void Aig_ManOrderStart | ( | Aig_Man_t * | p | ) |

CFile****************************************************************

FileName [aigOrder.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [AIG package.]

Synopsis [Dynamically updated topological order.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - April 28, 2007.]

Revision [

- Id

- aigOrder.c,v 1.00 2007/04/28 00:00:00 alanmi Exp

] DECLARATIONS /// FUNCTION DEFINITIONS ///Function*************************************************************

Synopsis [Initializes the order datastructure.]

Description []

SideEffects []

SeeAlso []

Definition at line 42 of file aigOrder.c.

00043 { 00044 Aig_Obj_t * pObj; 00045 int i; 00046 assert( Aig_ManBufNum(p) == 0 ); 00047 // allocate order datastructure 00048 assert( p->pOrderData == NULL ); 00049 p->nOrderAlloc = 2 * Aig_ManObjNumMax(p); 00050 if ( p->nOrderAlloc < (1<<12) ) 00051 p->nOrderAlloc = (1<<12); 00052 p->pOrderData = ALLOC( unsigned, 2 * p->nOrderAlloc ); 00053 memset( p->pOrderData, 0xFF, sizeof(unsigned) * 2 * p->nOrderAlloc ); 00054 // add the constant node 00055 p->pOrderData[0] = p->pOrderData[1] = 0; 00056 p->iPrev = p->iNext = 0; 00057 // add the internal nodes 00058 Aig_ManForEachNode( p, pObj, i ) 00059 Aig_ObjOrderInsert( p, pObj->Id ); 00060 }

| void Aig_ManOrderStop | ( | Aig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Deletes the order datastructure.]

Description []

SideEffects []

SeeAlso []

Definition at line 73 of file aigOrder.c.

00074 { 00075 assert( p->pOrderData ); 00076 FREE( p->pOrderData ); 00077 p->nOrderAlloc = 0; 00078 p->iPrev = p->iNext = 0; 00079 }

Function*************************************************************

Synopsis [Perform the naive partitioning.]

Description []

SideEffects []

SeeAlso []

Definition at line 697 of file aigPart.c.

00698 { 00699 Vec_Ptr_t * vParts; 00700 Aig_Obj_t * pObj; 00701 int nParts, i; 00702 nParts = (Aig_ManPoNum(p) / nPartSize) + ((Aig_ManPoNum(p) % nPartSize) > 0); 00703 vParts = (Vec_Ptr_t *)Vec_VecStart( nParts ); 00704 Aig_ManForEachPo( p, pObj, i ) 00705 Vec_IntPush( Vec_PtrEntry(vParts, i / nPartSize), i ); 00706 return vParts; 00707 }

| Vec_Ptr_t* Aig_ManPartitionSmart | ( | Aig_Man_t * | p, | |

| int | nSuppSizeLimit, | |||

| int | fVerbose, | |||

| Vec_Ptr_t ** | pvPartSupps | |||

| ) |

Function*************************************************************

Synopsis [Perform the smart partitioning.]

Description []

SideEffects []

SeeAlso []

Definition at line 573 of file aigPart.c.

00574 { 00575 Vec_Ptr_t * vPartSuppsBit; 00576 Vec_Ptr_t * vSupports, * vPartsAll, * vPartsAll2, * vPartSuppsAll;//, * vPartPtr; 00577 Vec_Int_t * vOne, * vPart, * vPartSupp, * vTemp; 00578 int i, iPart, iOut, clk; 00579 00580 // compute the supports for all outputs 00581 clk = clock(); 00582 vSupports = Aig_ManSupports( p ); 00583 if ( fVerbose ) 00584 { 00585 PRT( "Supps", clock() - clk ); 00586 } 00587 // start char-based support representation 00588 vPartSuppsBit = Vec_PtrAlloc( 1000 ); 00589 00590 // create partitions 00591 clk = clock(); 00592 vPartsAll = Vec_PtrAlloc( 256 ); 00593 vPartSuppsAll = Vec_PtrAlloc( 256 ); 00594 Vec_PtrForEachEntry( vSupports, vOne, i ) 00595 { 00596 // get the output number 00597 iOut = Vec_IntPop(vOne); 00598 // find closely matching part 00599 iPart = Aig_ManPartitionSmartFindPart( vPartSuppsAll, vPartsAll, vPartSuppsBit, nSuppSizeLimit, vOne ); 00600 if ( iPart == -1 ) 00601 { 00602 // create new partition 00603 vPart = Vec_IntAlloc( 32 ); 00604 Vec_IntPush( vPart, iOut ); 00605 // create new partition support 00606 vPartSupp = Vec_IntDup( vOne ); 00607 // add this partition and its support 00608 Vec_PtrPush( vPartsAll, vPart ); 00609 Vec_PtrPush( vPartSuppsAll, vPartSupp ); 00610 00611 Vec_PtrPush( vPartSuppsBit, Aig_ManSuppCharStart(vOne, Aig_ManPiNum(p)) ); 00612 } 00613 else 00614 { 00615 // add output to this partition 00616 vPart = Vec_PtrEntry( vPartsAll, iPart ); 00617 Vec_IntPush( vPart, iOut ); 00618 // merge supports 00619 vPartSupp = Vec_PtrEntry( vPartSuppsAll, iPart ); 00620 vPartSupp = Vec_IntTwoMerge( vTemp = vPartSupp, vOne ); 00621 Vec_IntFree( vTemp ); 00622 // reinsert new support 00623 Vec_PtrWriteEntry( vPartSuppsAll, iPart, vPartSupp ); 00624 00625 Aig_ManSuppCharAdd( Vec_PtrEntry(vPartSuppsBit, iPart), vOne, Aig_ManPiNum(p) ); 00626 } 00627 } 00628 00629 // stop char-based support representation 00630 Vec_PtrForEachEntry( vPartSuppsBit, vTemp, i ) 00631 free( vTemp ); 00632 Vec_PtrFree( vPartSuppsBit ); 00633 00634 //printf( "\n" ); 00635 if ( fVerbose ) 00636 { 00637 PRT( "Parts", clock() - clk ); 00638 } 00639 00640 clk = clock(); 00641 // reorder partitions in the decreasing order of support sizes 00642 // remember partition number in each partition support 00643 Vec_PtrForEachEntry( vPartSuppsAll, vOne, i ) 00644 Vec_IntPush( vOne, i ); 00645 // sort the supports in the decreasing order 00646 Vec_VecSort( (Vec_Vec_t *)vPartSuppsAll, 1 ); 00647 // reproduce partitions 00648 vPartsAll2 = Vec_PtrAlloc( 256 ); 00649 Vec_PtrForEachEntry( vPartSuppsAll, vOne, i ) 00650 Vec_PtrPush( vPartsAll2, Vec_PtrEntry(vPartsAll, Vec_IntPop(vOne)) ); 00651 Vec_PtrFree( vPartsAll ); 00652 vPartsAll = vPartsAll2; 00653 00654 // compact small partitions 00655 // Aig_ManPartitionPrint( p, vPartsAll, vPartSuppsAll ); 00656 Aig_ManPartitionCompact( vPartsAll, vPartSuppsAll, nSuppSizeLimit ); 00657 if ( fVerbose ) 00658 // Aig_ManPartitionPrint( p, vPartsAll, vPartSuppsAll ); 00659 printf( "Created %d partitions.\n", Vec_PtrSize(vPartsAll) ); 00660 00661 if ( fVerbose ) 00662 { 00663 //PRT( "Comps", clock() - clk ); 00664 } 00665 00666 // cleanup 00667 Vec_VecFree( (Vec_Vec_t *)vSupports ); 00668 if ( pvPartSupps == NULL ) 00669 Vec_VecFree( (Vec_Vec_t *)vPartSuppsAll ); 00670 else 00671 *pvPartSupps = vPartSuppsAll; 00672 /* 00673 // converts from intergers to nodes 00674 Vec_PtrForEachEntry( vPartsAll, vPart, iPart ) 00675 { 00676 vPartPtr = Vec_PtrAlloc( Vec_IntSize(vPart) ); 00677 Vec_IntForEachEntry( vPart, iOut, i ) 00678 Vec_PtrPush( vPartPtr, Aig_ManPo(p, iOut) ); 00679 Vec_IntFree( vPart ); 00680 Vec_PtrWriteEntry( vPartsAll, iPart, vPartPtr ); 00681 } 00682 */ 00683 return vPartsAll; 00684 }

Definition at line 199 of file aig.h.

00199 { return (Aig_Obj_t *)Vec_PtrEntry(p->vPis, i); }

| static int Aig_ManPiNum | ( | Aig_Man_t * | p | ) | [inline, static] |

Definition at line 184 of file aig.h.

00184 { return p->nObjs[AIG_OBJ_PI]; }

Definition at line 200 of file aig.h.

00200 { return (Aig_Obj_t *)Vec_PtrEntry(p->vPos, i); }

| static int Aig_ManPoNum | ( | Aig_Man_t * | p | ) | [inline, static] |

Definition at line 185 of file aig.h.

00185 { return p->nObjs[AIG_OBJ_PO]; }

| void Aig_ManPrintStats | ( | Aig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Stops the AIG manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 302 of file aigMan.c.

00303 { 00304 printf( "PI/PO/Lat = %5d/%5d/%5d ", Aig_ManPiNum(p), Aig_ManPoNum(p), Aig_ManLatchNum(p) ); 00305 printf( "A = %7d. ", Aig_ManAndNum(p) ); 00306 if ( Aig_ManExorNum(p) ) 00307 printf( "X = %5d. ", Aig_ManExorNum(p) ); 00308 // if ( Aig_ManBufNum(p) ) 00309 printf( "B = %5d. ", Aig_ManBufNum(p) ); 00310 // printf( "Cre = %6d. ", p->nCreated ); 00311 // printf( "Del = %6d. ", p->nDeleted ); 00312 // printf( "Lev = %3d. ", Aig_ManCountLevels(p) ); 00313 printf( "Max = %7d. ", Aig_ManObjNumMax(p) ); 00314 printf( "Lev = %3d. ", Aig_ManLevels(p) ); 00315 if ( Aig_ManRegNum(p) ) 00316 printf( "Lat = %5d. ", Aig_ManRegNum(p) ); 00317 printf( "\n" ); 00318 fflush( stdout ); 00319 }

| void Aig_ManPrintVerbose | ( | Aig_Man_t * | p, | |

| int | fHaig | |||

| ) |

Function*************************************************************

Synopsis [Prints node in HAIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 614 of file aigUtil.c.

00615 { 00616 Vec_Ptr_t * vNodes; 00617 Aig_Obj_t * pObj; 00618 int i; 00619 printf( "PIs: " ); 00620 Aig_ManForEachPi( p, pObj, i ) 00621 printf( " %p", pObj ); 00622 printf( "\n" ); 00623 vNodes = Aig_ManDfs( p ); 00624 Vec_PtrForEachEntry( vNodes, pObj, i ) 00625 Aig_ObjPrintVerbose( pObj, fHaig ), printf( "\n" ); 00626 printf( "\n" ); 00627 }

Definition at line 296 of file aig.h.

00297 { 00298 extern void Aig_MmFixedEntryRecycle( Aig_MmFixed_t * p, char * pEntry ); 00299 assert( pEntry->nRefs == 0 ); 00300 pEntry->Type = AIG_OBJ_NONE; // distinquishes a dead node from a live node 00301 Aig_MmFixedEntryRecycle( p->pMemObjs, (char *)pEntry ); 00302 p->nDeleted++; 00303 }

Function*************************************************************

Synopsis [Reduces the latches.]

Description []

SideEffects []

SeeAlso []

Definition at line 366 of file aigScl.c.

00367 { 00368 Aig_Man_t * pTemp; 00369 Vec_Ptr_t * vMap; 00370 int nSaved, nCur; 00371 for ( nSaved = 0; (nCur = Aig_ManReduceLachesCount(p)); nSaved += nCur ) 00372 { 00373 if ( fVerbose ) 00374 { 00375 printf( "Saved = %5d. ", nCur ); 00376 printf( "RBeg = %5d. NBeg = %6d. ", Aig_ManRegNum(p), Aig_ManNodeNum(p) ); 00377 } 00378 vMap = Aig_ManReduceLachesOnce( p ); 00379 p = Aig_ManRemap( pTemp = p, vMap ); 00380 Aig_ManStop( pTemp ); 00381 Vec_PtrFree( vMap ); 00382 Aig_ManSeqCleanup( p ); 00383 if ( fVerbose ) 00384 { 00385 printf( "REnd = %5d. NEnd = %6d. ", Aig_ManRegNum(p), Aig_ManNodeNum(p) ); 00386 printf( "\n" ); 00387 } 00388 if ( p->nRegs == 0 ) 00389 break; 00390 } 00391 return p; 00392 }

| static int Aig_ManRegNum | ( | Aig_Man_t * | p | ) | [inline, static] |

Function*************************************************************

Synopsis [Iteratively rehashes the AIG.]

Description [The input AIG is assumed to have representatives assigned.]

SideEffects []

SeeAlso []

Definition at line 390 of file aigRepr.c.

00391 { 00392 Aig_Man_t * pTemp; 00393 int i, nFanouts; 00394 assert( p->pReprs != NULL ); 00395 for ( i = 0; (nFanouts = Aig_ManRemapRepr( p )); i++ ) 00396 { 00397 // printf( "Iter = %3d. Fanouts = %6d. Nodes = %7d.\n", i+1, nFanouts, Aig_ManNodeNum(p) ); 00398 p = Aig_ManDupRepr( pTemp = p, 1 ); 00399 Aig_ManReprStart( p, Aig_ManObjNumMax(p) ); 00400 Aig_ManTransferRepr( p, pTemp ); 00401 Aig_ManStop( pTemp ); 00402 } 00403 return p; 00404 }

CFile****************************************************************

FileName [aigScl.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [AIG package.]

Synopsis [Sequential cleanup.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - April 28, 2007.]

Revision [

- Id

- aigScl.c,v 1.00 2007/04/28 00:00:00 alanmi Exp

] DECLARATIONS /// FUNCTION DEFINITIONS ///Function*************************************************************

Synopsis [Remaps the manager.]

Description [Map in the array specifies for each CI nodes the node that should be used after remapping.]

SideEffects []

SeeAlso []

Definition at line 43 of file aigScl.c.

00044 { 00045 Aig_Man_t * pNew; 00046 Aig_Obj_t * pObj, * pObjMapped; 00047 int i; 00048 // create the new manager 00049 pNew = Aig_ManStart( Aig_ManObjNumMax(p) ); 00050 pNew->pName = Aig_UtilStrsav( p->pName ); 00051 pNew->nRegs = p->nRegs; 00052 pNew->nAsserts = p->nAsserts; 00053 if ( p->vFlopNums ) 00054 pNew->vFlopNums = Vec_IntDup( p->vFlopNums ); 00055 // create the PIs 00056 Aig_ManCleanData( p ); 00057 Aig_ManConst1(p)->pData = Aig_ManConst1(pNew); 00058 Aig_ManForEachPi( p, pObj, i ) 00059 pObj->pData = Aig_ObjCreatePi(pNew); 00060 // implement the mapping 00061 Aig_ManForEachPi( p, pObj, i ) 00062 { 00063 pObjMapped = Vec_PtrEntry( vMap, i ); 00064 pObj->pData = Aig_NotCond( Aig_Regular(pObjMapped)->pData, Aig_IsComplement(pObjMapped) ); 00065 } 00066 // duplicate internal nodes 00067 Aig_ManForEachObj( p, pObj, i ) 00068 if ( Aig_ObjIsBuf(pObj) ) 00069 pObj->pData = Aig_ObjChild0Copy(pObj); 00070 else if ( Aig_ObjIsNode(pObj) ) 00071 pObj->pData = Aig_And( pNew, Aig_ObjChild0Copy(pObj), Aig_ObjChild1Copy(pObj) ); 00072 // add the POs 00073 Aig_ManForEachPo( p, pObj, i ) 00074 Aig_ObjCreatePo( pNew, Aig_ObjChild0Copy(pObj) ); 00075 assert( Aig_ManNodeNum(p) >= Aig_ManNodeNum(pNew) ); 00076 // check the resulting network 00077 if ( !Aig_ManCheck(pNew) ) 00078 printf( "Aig_ManDup(): The check has failed.\n" ); 00079 return pNew; 00080 }

| void Aig_ManReprStart | ( | Aig_Man_t * | p, | |

| int | nIdMax | |||

| ) |

CFile****************************************************************

FileName [aigRepr.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [AIG package.]

Synopsis [Handing node representatives.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - April 28, 2007.]

Revision [

- Id

- aigRepr.c,v 1.00 2007/04/28 00:00:00 alanmi Exp

] DECLARATIONS /// FUNCTION DEFINITIONS ///Function*************************************************************

Synopsis [Starts the array of representatives.]

Description []

SideEffects []

SeeAlso []

Definition at line 42 of file aigRepr.c.

00043 { 00044 assert( Aig_ManBufNum(p) == 0 ); 00045 assert( p->pReprs == NULL ); 00046 p->nReprsAlloc = nIdMax; 00047 p->pReprs = ALLOC( Aig_Obj_t *, p->nReprsAlloc ); 00048 memset( p->pReprs, 0, sizeof(Aig_Obj_t *) * p->nReprsAlloc ); 00049 }

| void Aig_ManReprStop | ( | Aig_Man_t * | p | ) |

| void Aig_ManResetRefs | ( | Aig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Reset reference counters.]

Description []

SideEffects []

SeeAlso []

Definition at line 116 of file aigUtil.c.

00117 { 00118 Aig_Obj_t * pObj; 00119 int i; 00120 Aig_ManForEachObj( p, pObj, i ) 00121 pObj->nRefs = 0; 00122 Aig_ManForEachObj( p, pObj, i ) 00123 { 00124 if ( Aig_ObjFanin0(pObj) ) 00125 Aig_ObjFanin0(pObj)->nRefs++; 00126 if ( Aig_ObjFanin1(pObj) ) 00127 Aig_ObjFanin1(pObj)->nRefs++; 00128 } 00129 }

| int Aig_ManSeqCleanup | ( | Aig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Returns the number of dangling nodes removed.]

Description []

SideEffects []

SeeAlso []

Definition at line 125 of file aigScl.c.

00126 { 00127 Vec_Ptr_t * vNodes, * vCis, * vCos; 00128 Aig_Obj_t * pObj, * pObjLi, * pObjLo; 00129 int i, nTruePis, nTruePos; 00130 assert( Aig_ManBufNum(p) == 0 ); 00131 00132 // mark the PIs 00133 Aig_ManIncrementTravId( p ); 00134 Aig_ObjSetTravIdCurrent( p, Aig_ManConst1(p) ); 00135 Aig_ManForEachPiSeq( p, pObj, i ) 00136 Aig_ObjSetTravIdCurrent( p, pObj ); 00137 00138 // prepare to collect nodes reachable from POs 00139 vNodes = Vec_PtrAlloc( 100 ); 00140 Aig_ManForEachPoSeq( p, pObj, i ) 00141 Vec_PtrPush( vNodes, pObj ); 00142 00143 // remember latch inputs in latch outputs 00144 Aig_ManForEachLiLoSeq( p, pObjLi, pObjLo, i ) 00145 pObjLo->pNext = pObjLi; 00146 // mark the nodes reachable from these nodes 00147 Vec_PtrForEachEntry( vNodes, pObj, i ) 00148 Aig_ManSeqCleanup_rec( p, pObj, vNodes ); 00149 assert( Vec_PtrSize(vNodes) <= Aig_ManPoNum(p) ); 00150 // clean latch output pointers 00151 Aig_ManForEachLiLoSeq( p, pObjLi, pObjLo, i ) 00152 pObjLo->pNext = NULL; 00153 00154 // if some latches are removed, update PIs/POs 00155 if ( Vec_PtrSize(vNodes) < Aig_ManPoNum(p) ) 00156 { 00157 if ( p->vFlopNums ) 00158 { 00159 int nTruePos = Aig_ManPoNum(p)-Aig_ManRegNum(p); 00160 // remember numbers of flops in the flops 00161 Aig_ManForEachLiSeq( p, pObj, i ) 00162 pObj->pNext = (Aig_Obj_t *)(long)Vec_IntEntry( p->vFlopNums, i - nTruePos ); 00163 // reset the flop numbers 00164 Vec_PtrForEachEntryStart( vNodes, pObj, i, nTruePos ) 00165 Vec_IntWriteEntry( p->vFlopNums, i - nTruePos, (int)(long)pObj->pNext ); 00166 Vec_IntShrink( p->vFlopNums, Vec_PtrSize(vNodes) - nTruePos ); 00167 // clean the next pointer 00168 Aig_ManForEachLiSeq( p, pObj, i ) 00169 pObj->pNext = NULL; 00170 } 00171 // collect new CIs/COs 00172 vCis = Vec_PtrAlloc( Aig_ManPiNum(p) ); 00173 Aig_ManForEachPi( p, pObj, i ) 00174 if ( Aig_ObjIsTravIdCurrent(p, pObj) ) 00175 Vec_PtrPush( vCis, pObj ); 00176 else 00177 { 00178 Vec_PtrWriteEntry( p->vObjs, pObj->Id, NULL ); 00179 // Aig_ManRecycleMemory( p, pObj ); 00180 } 00181 vCos = Vec_PtrAlloc( Aig_ManPoNum(p) ); 00182 Aig_ManForEachPo( p, pObj, i ) 00183 if ( Aig_ObjIsTravIdCurrent(p, pObj) ) 00184 Vec_PtrPush( vCos, pObj ); 00185 else 00186 { 00187 Aig_ObjDisconnect( p, pObj ); 00188 Vec_PtrWriteEntry( p->vObjs, pObj->Id, NULL ); 00189 // Aig_ManRecycleMemory( p, pObj ); 00190 } 00191 // remember the number of true PIs/POs 00192 nTruePis = Aig_ManPiNum(p) - Aig_ManRegNum(p); 00193 nTruePos = Aig_ManPoNum(p) - Aig_ManRegNum(p); 00194 // set the new number of registers 00195 p->nRegs -= Aig_ManPoNum(p) - Vec_PtrSize(vNodes); 00196 // create new PIs/POs 00197 assert( Vec_PtrSize(vCis) == nTruePis + p->nRegs ); 00198 assert( Vec_PtrSize(vCos) == nTruePos + p->nRegs ); 00199 Vec_PtrFree( p->vPis ); p->vPis = vCis; 00200 Vec_PtrFree( p->vPos ); p->vPos = vCos; 00201 p->nObjs[AIG_OBJ_PI] = Vec_PtrSize( p->vPis ); 00202 p->nObjs[AIG_OBJ_PO] = Vec_PtrSize( p->vPos ); 00203 00204 } 00205 Vec_PtrFree( vNodes ); 00206 // remove dangling nodes 00207 return Aig_ManCleanup( p ); 00208 }

| int Aig_ManSeqStrash | ( | Aig_Man_t * | p, | |

| int | nLatches, | |||

| int * | pInits | |||

| ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 439 of file aigSeq.c.

00440 { 00441 Vec_Ptr_t * vNodes, * vUnreach; 00442 // Aig_Obj_t * pObj, * pFanin; 00443 // int i; 00444 int Iter, RetValue = 1; 00445 00446 // create latches out of the additional PI/PO pairs 00447 Aig_ManSeqStrashConvert( p, nLatches, pInits ); 00448 00449 // iteratively rehash the network 00450 for ( Iter = 0; RetValue; Iter++ ) 00451 { 00452 // Aig_ManPrintStats( p ); 00453 /* 00454 Aig_ManForEachObj( p, pObj, i ) 00455 { 00456 assert( pObj->Type > 0 ); 00457 pFanin = Aig_ObjFanin0(pObj); 00458 assert( pFanin == NULL || pFanin->Type > 0 ); 00459 pFanin = Aig_ObjFanin1(pObj); 00460 assert( pFanin == NULL || pFanin->Type > 0 ); 00461 } 00462 */ 00463 // mark nodes unreachable from the PIs 00464 vUnreach = Aig_ManDfsUnreach( p ); 00465 if ( Iter == 0 && Vec_PtrSize(vUnreach) > 0 ) 00466 printf( "Unreachable objects = %d.\n", Vec_PtrSize(vUnreach) ); 00467 // collect nodes reachable from the POs 00468 vNodes = Aig_ManDfsSeq( p ); 00469 // remove nodes unreachable from the POs 00470 if ( Iter == 0 ) 00471 Aig_ManRemoveUnmarked( p ); 00472 // continue rehashing as long as there are changes 00473 RetValue = Aig_ManSeqRehashOne( p, vNodes, vUnreach ); 00474 Vec_PtrFree( vNodes ); 00475 Vec_PtrFree( vUnreach ); 00476 } 00477 00478 // perform the final cleanup 00479 Aig_ManIncrementTravId( p ); 00480 vNodes = Aig_ManDfsSeq( p ); 00481 Aig_ManRemoveUnmarked( p ); 00482 Vec_PtrFree( vNodes ); 00483 // remove buffers if they are left 00484 // Aig_ManRemoveBuffers( p ); 00485 00486 // clean up 00487 if ( !Aig_ManCheck( p ) ) 00488 { 00489 printf( "Aig_ManSeqStrash: The network check has failed.\n" ); 00490 return 0; 00491 } 00492 return 1; 00493 00494 }

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 329 of file aigShow.c.

00330 { 00331 extern void Abc_ShowFile( char * FileNameDot ); 00332 static Counter = 0; 00333 char FileNameDot[200]; 00334 FILE * pFile; 00335 // create the file name 00336 // Aig_ShowGetFileName( pMan->pName, FileNameDot ); 00337 sprintf( FileNameDot, "temp%02d.dot", Counter++ ); 00338 // check that the file can be opened 00339 if ( (pFile = fopen( FileNameDot, "w" )) == NULL ) 00340 { 00341 fprintf( stdout, "Cannot open the intermediate file \"%s\".\n", FileNameDot ); 00342 return; 00343 } 00344 fclose( pFile ); 00345 // generate the file 00346 Aig_WriteDotAig( pMan, FileNameDot, fHaig, vBold ); 00347 // visualize the file 00348 Abc_ShowFile( FileNameDot ); 00349 }

| Aig_Man_t* Aig_ManStart | ( | int | nNodesMax | ) |

CFile****************************************************************

FileName [aigMan.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [AIG package.]

Synopsis [AIG manager.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - April 28, 2007.]

Revision [

- Id

- aigMan.c,v 1.00 2007/04/28 00:00:00 alanmi Exp

] DECLARATIONS /// FUNCTION DEFINITIONS ///Function*************************************************************

Synopsis [Starts the AIG manager.]

Description [The argument of this procedure is a soft limit on the the number of nodes, or 0 if the limit is unknown.]

SideEffects []

SeeAlso []

Definition at line 43 of file aigMan.c.

00044 { 00045 Aig_Man_t * p; 00046 if ( nNodesMax <= 0 ) 00047 nNodesMax = 10007; 00048 // start the manager 00049 p = ALLOC( Aig_Man_t, 1 ); 00050 memset( p, 0, sizeof(Aig_Man_t) ); 00051 // perform initializations 00052 p->nTravIds = 1; 00053 p->fCatchExor = 0; 00054 // allocate arrays for nodes 00055 p->vPis = Vec_PtrAlloc( 100 ); 00056 p->vPos = Vec_PtrAlloc( 100 ); 00057 p->vObjs = Vec_PtrAlloc( 1000 ); 00058 p->vBufs = Vec_PtrAlloc( 100 ); 00059 // prepare the internal memory manager 00060 p->pMemObjs = Aig_MmFixedStart( sizeof(Aig_Obj_t), nNodesMax ); 00061 // create the constant node 00062 p->pConst1 = Aig_ManFetchMemory( p ); 00063 p->pConst1->Type = AIG_OBJ_CONST1; 00064 p->pConst1->fPhase = 1; 00065 p->nObjs[AIG_OBJ_CONST1]++; 00066 // start the table 00067 p->nTableSize = Aig_PrimeCudd( nNodesMax ); 00068 p->pTable = ALLOC( Aig_Obj_t *, p->nTableSize ); 00069 memset( p->pTable, 0, sizeof(Aig_Obj_t *) * p->nTableSize ); 00070 return p; 00071 }

Function*************************************************************

Synopsis [Duplicates the AIG manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 84 of file aigMan.c.

00085 { 00086 Aig_Man_t * pNew; 00087 Aig_Obj_t * pObj; 00088 int i; 00089 // create the new manager 00090 pNew = Aig_ManStart( Aig_ManObjNumMax(p) ); 00091 pNew->pName = Aig_UtilStrsav( p->pName ); 00092 // create the PIs 00093 Aig_ManConst1(p)->pData = Aig_ManConst1(pNew); 00094 Aig_ManForEachPi( p, pObj, i ) 00095 pObj->pData = Aig_ObjCreatePi(pNew); 00096 return pNew; 00097 }

| void Aig_ManStartMemory | ( | Aig_Man_t * | p | ) |

| void Aig_ManStartReverseLevels | ( | Aig_Man_t * | p, | |

| int | nMaxLevelIncrease | |||

| ) |

Function*************************************************************

Synopsis [Prepares for the computation of required levels.]

Description [This procedure should be called before the required times are used. It starts internal data structures, which records the level from the COs of the network nodes in reverse topologogical order.]

SideEffects []

SeeAlso []

Definition at line 139 of file aigTiming.c.

00140 { 00141 Vec_Ptr_t * vNodes; 00142 Aig_Obj_t * pObj; 00143 int i; 00144 assert( p->pFanData != NULL ); 00145 assert( p->vLevelR == NULL ); 00146 // remember the maximum number of direct levels 00147 p->nLevelMax = Aig_ManLevels(p) + nMaxLevelIncrease; 00148 // start the reverse levels 00149 p->vLevelR = Vec_IntAlloc( 0 ); 00150 Vec_IntFill( p->vLevelR, Aig_ManObjNumMax(p), 0 ); 00151 // compute levels in reverse topological order 00152 vNodes = Aig_ManDfsReverse( p ); 00153 Vec_PtrForEachEntry( vNodes, pObj, i ) 00154 { 00155 assert( pObj->fMarkA == 0 ); 00156 Aig_ObjSetReverseLevel( p, pObj, Aig_ObjReverseLevelNew(p, pObj) ); 00157 } 00158 Vec_PtrFree( vNodes ); 00159 }

| void Aig_ManStop | ( | Aig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Stops the AIG manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 227 of file aigMan.c.

00228 { 00229 Aig_Obj_t * pObj; 00230 int i; 00231 if ( p->vMapped ) 00232 Vec_PtrFree( p->vMapped ); 00233 // print time 00234 if ( p->time1 ) { PRT( "time1", p->time1 ); } 00235 if ( p->time2 ) { PRT( "time2", p->time2 ); } 00236 // delete timing 00237 if ( p->pManTime ) 00238 Aig_TManStop( p->pManTime ); 00239 // delete fanout 00240 if ( p->pFanData ) 00241 Aig_ManFanoutStop( p ); 00242 // make sure the nodes have clean marks 00243 Aig_ManForEachObj( p, pObj, i ) 00244 assert( !pObj->fMarkA && !pObj->fMarkB ); 00245 // Aig_TableProfile( p ); 00246 Aig_MmFixedStop( p->pMemObjs, 0 ); 00247 if ( p->vPis ) Vec_PtrFree( p->vPis ); 00248 if ( p->vPos ) Vec_PtrFree( p->vPos ); 00249 if ( p->vObjs ) Vec_PtrFree( p->vObjs ); 00250 if ( p->vBufs ) Vec_PtrFree( p->vBufs ); 00251 if ( p->vLevelR ) Vec_IntFree( p->vLevelR ); 00252 if ( p->vLevels ) Vec_VecFree( p->vLevels ); 00253 if ( p->vFlopNums) Vec_IntFree( p->vFlopNums ); 00254 FREE( p->pName ); 00255 FREE( p->pObjCopies ); 00256 FREE( p->pReprs ); 00257 FREE( p->pEquivs ); 00258 free( p->pTable ); 00259 free( p ); 00260 }

| void Aig_ManStopMemory | ( | Aig_Man_t * | p | ) |

| void Aig_ManStopReverseLevels | ( | Aig_Man_t * | p | ) |

Function*************************************************************

Synopsis [Cleans the data structures used to compute required levels.]

Description []

SideEffects []

SeeAlso []

Definition at line 172 of file aigTiming.c.

Function*************************************************************

Synopsis [Computes supports of the POs in the multi-output AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 267 of file aigPart.c.