partial_map.h File Reference

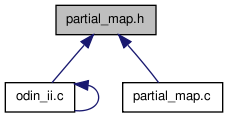

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Functions | |

| void | partial_map_top (netlist_t *netlist) |

| void | instantiate_add_w_carry (nnode_t *node, short mark, netlist_t *netlist) |

Function Documentation

Definition at line 587 of file partial_map.c.

00588 { 00589 int width; 00590 int width_a; 00591 int width_b; 00592 int i; 00593 nnode_t **new_add_cells; 00594 nnode_t **new_carry_cells; 00595 00596 oassert(node->num_input_pins > 0); 00597 oassert(node->num_input_port_sizes == 2); 00598 width = node->output_port_sizes[0]; 00599 width_a = node->input_port_sizes[0]; 00600 width_b = node->input_port_sizes[1]; 00601 00602 new_add_cells = (nnode_t**)malloc(sizeof(nnode_t*)*width); 00603 new_carry_cells = (nnode_t**)malloc(sizeof(nnode_t*)*width); 00604 00605 /* create the adder units and the zero unit */ 00606 for (i = 0; i < width; i++) 00607 { 00608 new_add_cells[i] = make_3port_gate(ADDER_FUNC, 1, 1, 1, 1, node, mark); 00609 if (i < width - 1) 00610 { 00611 new_carry_cells[i] = make_3port_gate(CARRY_FUNC, 1, 1, 1, 1, node, mark); 00612 } 00613 } 00614 00615 /* ground first carry in */ 00616 add_a_input_pin_to_node_spot_idx(new_add_cells[0], get_a_zero_pin(netlist), 0); 00617 if (i > 1) 00618 { 00619 add_a_input_pin_to_node_spot_idx(new_carry_cells[0], get_a_zero_pin(netlist), 0); 00620 } 00621 00622 /* connect inputs */ 00623 for(i = 0; i < width; i++) 00624 { 00625 if (i < width_a) 00626 { 00627 /* join the A port up to adder */ 00628 remap_pin_to_new_node(node->input_pins[i], new_add_cells[i], 1); 00629 if (i < width - 1) 00630 add_a_input_pin_to_node_spot_idx(new_carry_cells[i], copy_input_npin(new_add_cells[i]->input_pins[1]), 1); 00631 } 00632 else 00633 { 00634 add_a_input_pin_to_node_spot_idx(new_add_cells[i], get_a_zero_pin(netlist), 1); 00635 if (i < width - 1) 00636 add_a_input_pin_to_node_spot_idx(new_carry_cells[i], get_a_zero_pin(netlist), 1); 00637 } 00638 00639 if (i < width_b) 00640 { 00641 /* join the B port up to adder */ 00642 remap_pin_to_new_node(node->input_pins[i+width_a], new_add_cells[i], 2); 00643 if (i < width - 1) 00644 add_a_input_pin_to_node_spot_idx(new_carry_cells[i], copy_input_npin(new_add_cells[i]->input_pins[2]), 2); 00645 } 00646 else 00647 { 00648 add_a_input_pin_to_node_spot_idx(new_add_cells[i], get_a_zero_pin(netlist), 2); 00649 if (i < width - 1) 00650 add_a_input_pin_to_node_spot_idx(new_carry_cells[i], get_a_zero_pin(netlist), 2); 00651 } 00652 00653 /* join that gate to the output */ 00654 remap_pin_to_new_node(node->output_pins[i], new_add_cells[i], 0); 00655 } 00656 00657 /* connect carry outs with carry ins */ 00658 for(i = 1; i < width; i++) 00659 { 00660 connect_nodes(new_carry_cells[i-1], 0, new_add_cells[i], 0); 00661 if (i < width - 1) 00662 connect_nodes(new_carry_cells[i-1], 0, new_carry_cells[i], 0); 00663 } 00664 00665 free(new_add_cells); 00666 free(new_carry_cells); 00667 }

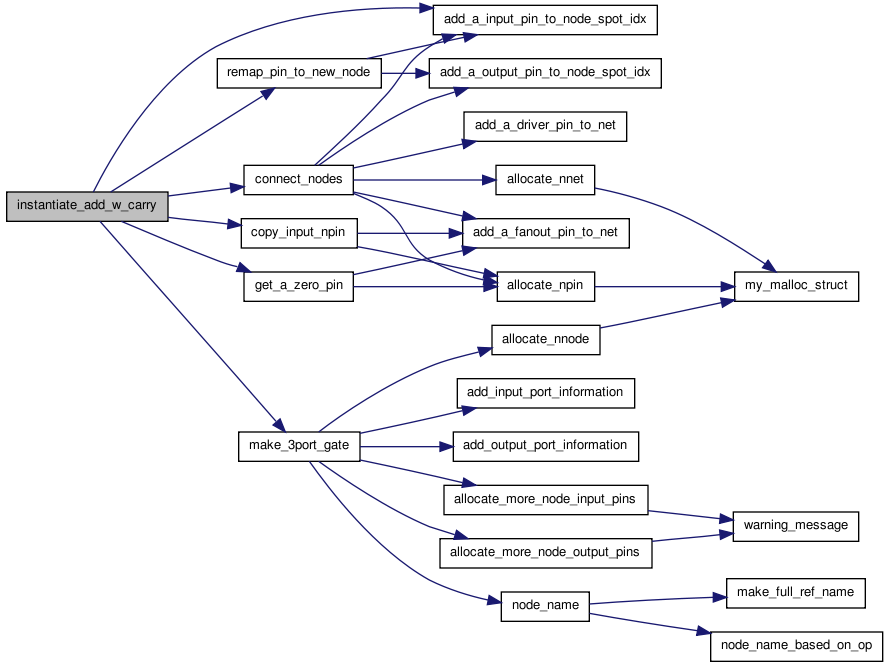

Here is the call graph for this function:

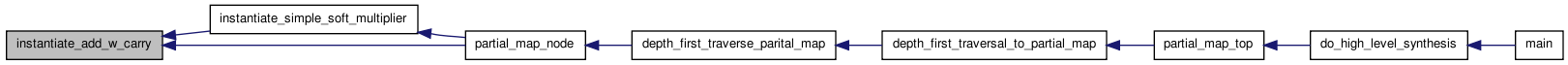

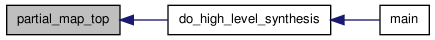

Here is the caller graph for this function:

| void partial_map_top | ( | netlist_t * | netlist | ) |

Definition at line 61 of file partial_map.c.

00062 { 00063 /* depending on the output target choose how to do partial mapping */ 00064 if (strcmp(configuration.output_type, "blif") == 0) 00065 { 00066 /* do the partial map without any larger structures identified */ 00067 depth_first_traversal_to_partial_map(PARTIAL_MAP_TRAVERSE_VALUE, netlist); 00068 } 00069 }

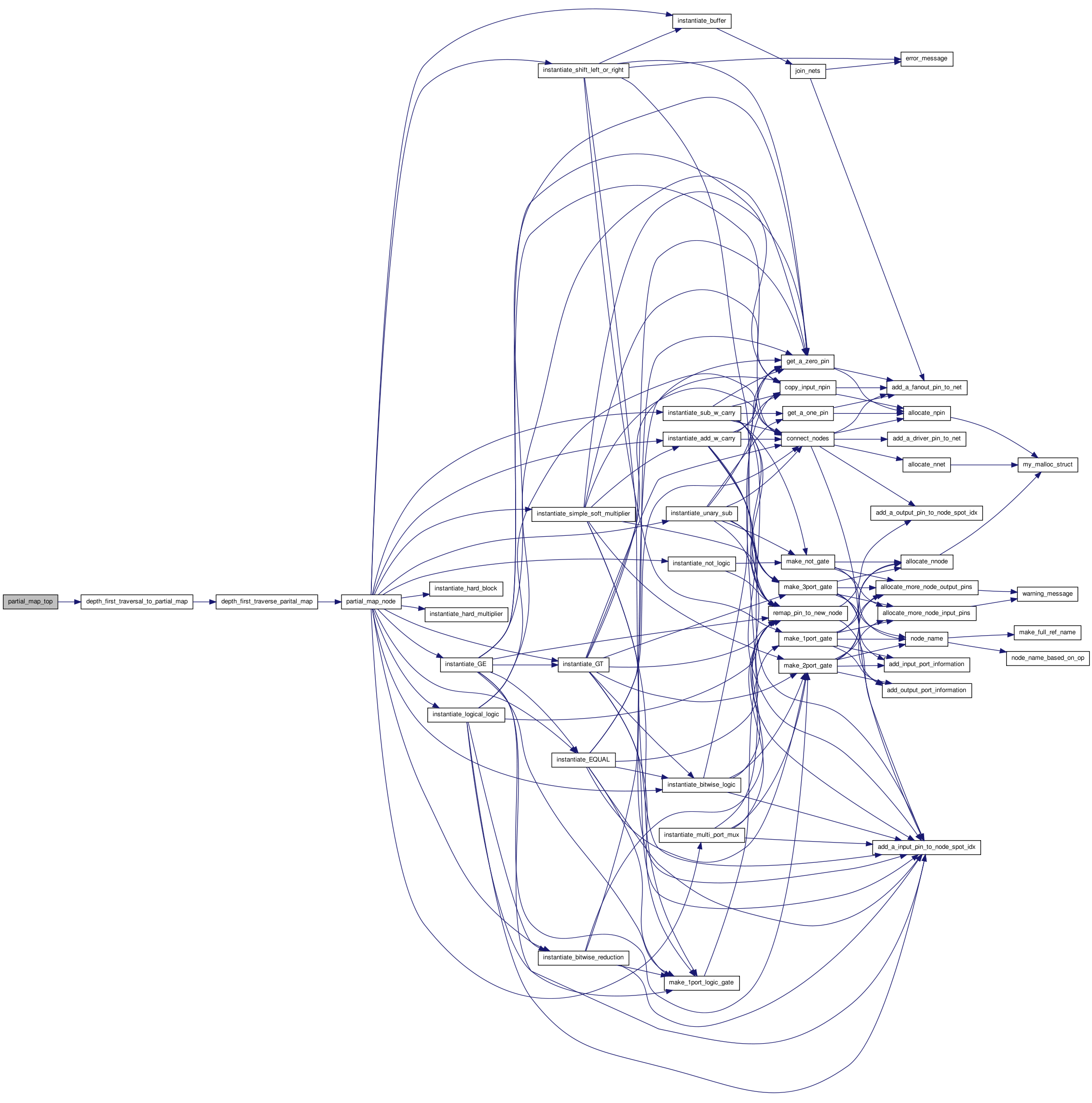

Here is the call graph for this function:

Here is the caller graph for this function:

1.6.3

1.6.3