vpr/SRC/base/read_blif.h File Reference

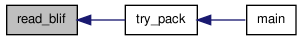

This graph shows which files directly or indirectly include this file:

This graph shows which files directly or indirectly include this file:Go to the source code of this file.

Functions | |

| void | read_blif (char *blif_file, boolean sweep_hanging_nets_and_inputs, t_model *user_models, t_model *library_models) |

| void | echo_input (char *blif_file, char *echo_file, t_model *library_models) |

Function Documentation

| void echo_input | ( | char * | blif_file, |

| char * | echo_file, | ||

| t_model * | library_models | ||

| ) |

Echo back the netlist data structures to file input.echo to allow the user to look at the internal state of the program and check the parsing.

Definition at line 1007 of file read_blif.c.

{

int i, j;

FILE *fp;

t_model_ports *port;

t_model *latch_model;

t_model *logic_model;

t_model *cur;

int *lut_distribution;

int num_absorbable_latch;

int inet;

cur = library_models;

logic_model = latch_model = NULL;

while(cur) {

if(strcmp(cur->name, MODEL_LOGIC) == 0) {

logic_model = cur;

assert(logic_model->inputs->next == NULL);

} else if(strcmp(cur->name, MODEL_LATCH) == 0) {

latch_model = cur;

assert(latch_model->inputs->size == 1);

}

cur = cur->next;

}

lut_distribution = my_calloc(logic_model->inputs[0].size + 1, sizeof(int));

num_absorbable_latch = 0;

for(i = 0; i < num_logical_blocks; i++) {

if(logical_block[i].model == logic_model) {

if(logic_model == NULL)

continue;

for(j = 0; j < logic_model->inputs[0].size; j++) {

if(logical_block[i].input_nets[0][j] == OPEN) {

break;

}

}

lut_distribution[j]++;

} else if (logical_block[i].model == latch_model) {

if(latch_model == NULL)

continue;

inet = logical_block[i].input_nets[0][0];

if (vpack_net[inet].num_sinks == 1 && logical_block[vpack_net[inet].node_block[0]].model == logic_model) {

num_absorbable_latch++;

}

}

}

printf("Input netlist file: %s Model: %s\n", blif_file, model);

printf("Primary Inputs: %d. Primary Outputs: %d.\n", num_p_inputs, num_p_outputs);

printf("LUTs: %d. Latches: %d Subckts: %d.\n", num_luts, num_latches, num_subckts);

printf("# Standard absorbable latches: %d\n", num_absorbable_latch);

for(i = 0; i < logic_model->inputs[0].size + 1; i++) {

printf("LUT size %d = %d, ", i, lut_distribution[i]);

}

printf("\n");

printf("Total Blocks: %d. Total Nets: %d\n", num_logical_blocks, num_logical_nets);

fp = my_fopen(echo_file, "w", 0);

fprintf(fp, "Input netlist file: %s Model: %s\n", blif_file, model);

fprintf(fp, "num_p_inputs: %d, num_p_outputs: %d, num_luts: %d," " num_latches: %d\n", num_p_inputs, num_p_outputs, num_luts, num_latches);

fprintf(fp, "num_logical_blocks: %d, num_logical_nets: %d\n", num_logical_blocks, num_logical_nets);

fprintf(fp, "\nNet\tName\t\t#Pins\tDriver\tRecvs.\n");

for(i = 0; i < num_logical_nets; i++)

{

fprintf(fp, "\n%d\t%s\t", i, vpack_net[i].name);

if(strlen(vpack_net[i].name) < 8)

fprintf(fp, "\t"); /* Name field is 16 chars wide */

fprintf(fp, "%d", vpack_net[i].num_sinks + 1);

for(j = 0; j <= vpack_net[i].num_sinks; j++)

fprintf(fp, "\t(%d,%d,%d)", vpack_net[i].node_block[j], vpack_net[i].node_block_port[j], vpack_net[i].node_block_pin[j]);

}

fprintf(fp, "\n\n\nBlocks\t\t\tBlock Type Legend:\n");

fprintf(fp, "\t\t\tINPAD = %d\tOUTPAD = %d\n", VPACK_INPAD, VPACK_OUTPAD);

fprintf(fp, "\t\t\tCOMB = %d\t\tLATCH = %d\n", VPACK_COMB, VPACK_LATCH);

fprintf(fp, "\t\t\tEMPTY = %d\n", VPACK_EMPTY);

for(i = 0; i < num_logical_blocks; i++)

{

fprintf(fp, "\nblock %d\t%s\t", i, logical_block[i].name);

fprintf(fp, "type: %d\n", logical_block[i].type);

fprintf(fp, "model name: %s\n", logical_block[i].model->name);

port = logical_block[i].model->inputs;

while(port) {

fprintf(fp, "\tInput Port: %s\n", port->name);

for(j = 0; j < port->size; j++) {

if(logical_block[i].input_nets[port->index][j] == OPEN)

fprintf(fp, "\tOPEN");

else

fprintf(fp, "\t%d", logical_block[i].input_nets[port->index][j]);

}

port = port->next;

}

port = logical_block[i].model->outputs;

while(port) {

fprintf(fp, "\tOutput Port: %s\n", port->name);

for(j = 0; j < port->size; j++) {

if(logical_block[i].output_nets[port->index][j] == OPEN) {

fprintf(fp, "\tOPEN");

} else {

fprintf(fp, "\t%d", logical_block[i].output_nets[port->index][j]);

}

}

port = port->next;

}

fprintf(fp, "\n\tclock net %d\n", logical_block[i].clock_net);

}

fprintf(fp, "\n");

fclose(fp);

}

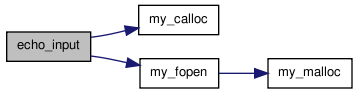

Here is the call graph for this function:

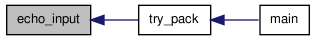

Here is the call graph for this function: Here is the caller graph for this function:

Here is the caller graph for this function:| void read_blif | ( | char * | blif_file, |

| boolean | sweep_hanging_nets_and_inputs, | ||

| t_model * | user_models, | ||

| t_model * | library_models | ||

| ) |

Definition at line 82 of file read_blif.c.

{

char buffer[BUFSIZE];

int pass, doall;

boolean done;

boolean add_truth_table;

t_model *inpad_model, *outpad_model, *logic_model, *latch_model;

blif = fopen(blif_file, "r");

if(blif == NULL) {

printf("Failed to open blif file %s\n", blif_file);

exit(1);

}

load_default_models(library_models, &inpad_model, &outpad_model, &logic_model, &latch_model);

/* doall = 0 means do a counting pass, doall = 1 means allocate and load data structures */

for(doall = 0; doall <= 1; doall++)

{

init_parse(doall);

/* Three passes to ensure inputs are first blocks, outputs second and *

* LUTs and latches third, subckts last. Just makes the output netlist more readable. */

for(pass = 0; pass <= 4; pass++)

{

linenum = 0; /* Reset line number. */

done = FALSE;

add_truth_table = FALSE;

model_lines = 0;

while(my_fgets(buffer, BUFSIZE, blif) != NULL)

{

get_tok(buffer, pass, doall, &done, &add_truth_table, inpad_model, outpad_model, logic_model, latch_model, user_models);

}

rewind(blif); /* Start at beginning of file again */

}

}

fclose(blif);

check_net(sweep_hanging_nets_and_inputs);

free_parse();

}

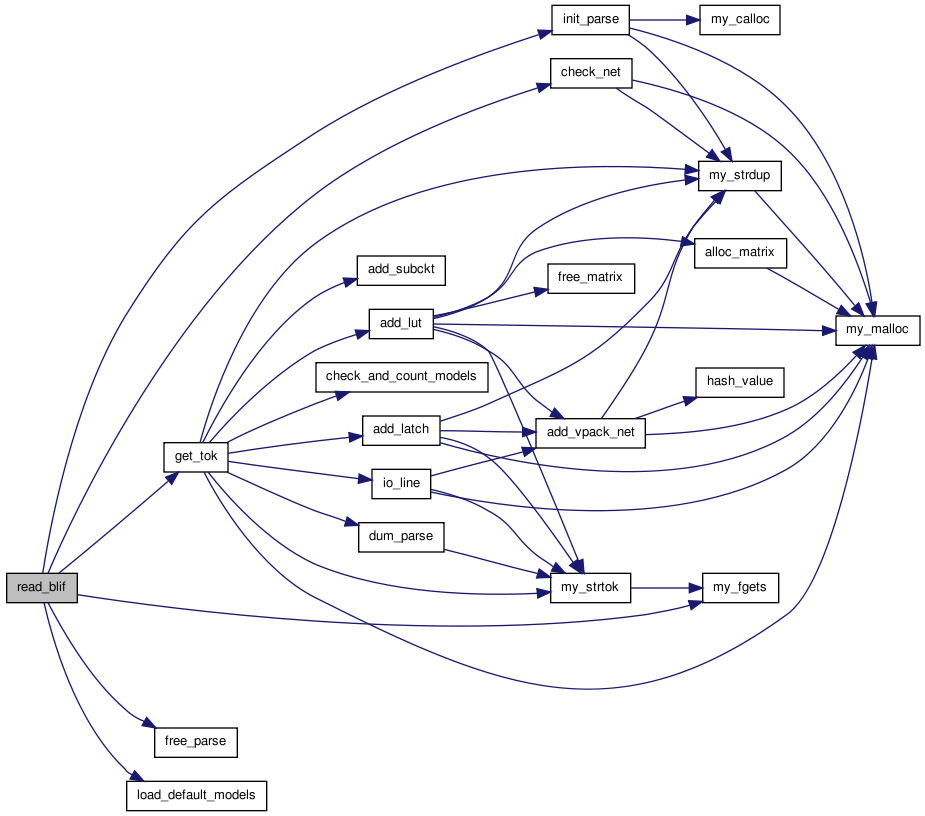

Here is the call graph for this function:

Here is the call graph for this function: Here is the caller graph for this function:

Here is the caller graph for this function: