vpr/SRC/base/read_netlist.h File Reference

This graph shows which files directly or indirectly include this file:

This graph shows which files directly or indirectly include this file:Go to the source code of this file.

Functions | |

| void | read_netlist (INP const char *net_file, INP const t_arch *arch, OUTP int *num_blocks, OUTP struct s_block *block_list[], OUTP int *num_nets, OUTP struct s_net *net_list[]) |

| void | free_logical_blocks () |

| void | free_logical_nets () |

Detailed Description

Author: Jason Luu Date: May 2009

Read a circuit netlist in XML format and populate the netlist data structures for VPR

Definition in file read_netlist.h.

Function Documentation

| void free_logical_blocks | ( | ) |

Free logical blocks of netlist

Definition at line 1142 of file read_netlist.c.

{

int iblk, i;

t_model_ports *port;

struct s_linked_vptr *tvptr, *next;

for (iblk=0;iblk<num_logical_blocks;iblk++) {

port = logical_block[iblk].model->inputs;

i = 0;

while(port) {

if(!port->is_clock) {

free(logical_block[iblk].input_nets[i]);

if(logical_block[iblk].input_net_tnodes) {

if(logical_block[iblk].input_net_tnodes[i])

free(logical_block[iblk].input_net_tnodes[i]);

}

i++;

}

port = port->next;

}

if(logical_block[iblk].input_net_tnodes) {

free(logical_block[iblk].input_net_tnodes);

}

free(logical_block[iblk].input_nets);

port = logical_block[iblk].model->outputs;

i = 0;

while(port) {

free(logical_block[iblk].output_nets[i]);

if(logical_block[iblk].output_net_tnodes) {

if(logical_block[iblk].output_net_tnodes[i])

free(logical_block[iblk].output_net_tnodes[i]);

}

i++;

port = port->next;

}

if(logical_block[iblk].output_net_tnodes) {

free(logical_block[iblk].output_net_tnodes);

}

free(logical_block[iblk].output_nets);

free(logical_block[iblk].name);

tvptr = logical_block[iblk].truth_table;

while(tvptr != NULL) {

if(tvptr->data_vptr)

free(tvptr->data_vptr);

next = tvptr->next;

free(tvptr);

tvptr = next;

}

}

free(logical_block);

}

Here is the caller graph for this function:

Here is the caller graph for this function:| void free_logical_nets | ( | ) |

Free logical blocks of netlist

Definition at line 1194 of file read_netlist.c.

{

int inet;

for (inet=0;inet<num_logical_nets;inet++) {

free(vpack_net[inet].name);

free(vpack_net[inet].node_block);

free(vpack_net[inet].node_block_port);

free(vpack_net[inet].node_block_pin);

}

free(vpack_net);

}

Here is the caller graph for this function:

Here is the caller graph for this function:| void read_netlist | ( | INP const char * | net_file, |

| INP const t_arch * | arch, | ||

| OUTP int * | num_blocks, | ||

| OUTP struct s_block * | block_list[], | ||

| OUTP int * | num_nets, | ||

| OUTP struct s_net * | net_list[] | ||

| ) |

Initializes the block_list with info from a netlist

- Parameters:

-

net_file - Name of the netlist file to read num_blocks - number of CLBs in netlist block_list - array of blocks in netlist [0..num_blocks - 1] num_nets - number of nets in netlist net_list - nets in netlist [0..num_nets - 1]

Definition at line 77 of file read_netlist.c.

{

ezxml_t Cur, Prev, Top;

int i, j;

const char *Prop;

int bcount;

struct s_block *blist;

int ncount, ext_ncount;

struct s_net *nlist, *ext_nlist;

struct s_hash **nhash;

char **circuit_inputs, **circuit_outputs, **circuit_globals;

int Count, Len;

int num_primitives = 0;

/* Parse the file */

printf("Begin parsing packed FPGA netlist file\n");

Top = ezxml_parse_file(net_file);

if(NULL == Top)

{

printf(ERRTAG "Unable to load netlist file '%s'.\n", net_file);

exit(1);

}

printf("Finished parsing packed FPGA netlist file\n");

/* Root node should be block */

CheckElement(Top, "block");

/* Check top-level netlist attributes */

Prop = FindProperty(Top, "name", TRUE);

printf("Netlist generated from file %s\n", Prop);

ezxml_set_attr(Top, "name", NULL);

Prop = FindProperty(Top, "instance", TRUE);

if(strcmp(Prop, "FPGA_packed_netlist[0]") != 0) {

printf(ERRTAG "[Line %d] Expected instance to be \"FPGA_packed_netlist[0]\", found %s", Top->line, Prop);

exit(1);

}

ezxml_set_attr(Top, "instance", NULL);

/* Parse top-level netlist I/Os */

Cur = FindElement(Top, "inputs", TRUE);

circuit_inputs = GetNodeTokens(Cur);

FreeNode(Cur);

Cur = FindElement(Top, "outputs", TRUE);

circuit_outputs = GetNodeTokens(Cur);

FreeNode(Cur);

Cur = FindElement(Top, "globals", TRUE);

CountTokensInString(Cur->txt, &Count, &Len);

if(Count > 0) {

circuit_globals = GetNodeTokens(Cur);

} else {

circuit_globals = NULL;

}

FreeNode(Cur);

/* Parse all CLB blocks and all nets*/

bcount = CountChildren(Top, "block", 1);

blist = my_calloc(bcount, sizeof(t_block));

nhash = alloc_hash_table();

ncount = 0;

logical_block = my_calloc(num_saved_logical_blocks, sizeof(t_logical_block));

num_logical_blocks = num_saved_logical_blocks;

Cur = Top->child;

i = 0;

while(Cur) {

if(0 == strcmp(Cur->name, "block"))

{

CheckElement(Cur, "block");

processComplexBlock(Cur, blist, i, &ncount, nhash, &num_primitives, arch);

Prev = Cur;

Cur = Cur->next;

FreeNode(Prev);

i++;

} else {

Cur = Cur->next;

}

}

assert(i == bcount);

if(saved_logical_blocks != NULL) {

assert(num_primitives == num_saved_logical_blocks);

}

nlist = alloc_and_init_netlist_from_hash(ncount, nhash);

mark_constant_generators(bcount, blist, ncount, nlist);

load_external_nets_and_cb(bcount, blist, ncount, nlist, &ext_ncount, &ext_nlist, circuit_globals);

/* TODO: create this function later

check_top_IO_matches_IO_blocks(circuit_inputs, circuit_outputs, circuit_globals, blist, bcount);

*/

free_hash_table(nhash);

FreeTokens(&circuit_inputs);

FreeTokens(&circuit_outputs);

if(circuit_globals)

FreeTokens(&circuit_globals);

FreeNode(Top);

/* load mapping between external nets and all nets */

/* jluu TODO: Should use local variables here then assign to globals later, clean up later */

vpack_net = nlist;

num_logical_nets = ncount;

clb_to_vpack_net_mapping = my_malloc(ext_ncount * sizeof(int));

vpack_to_clb_net_mapping = my_malloc(ncount * sizeof(int));

for(i = 0; i < ncount; i++) {

vpack_to_clb_net_mapping[i] = OPEN;

}

for(i = 0; i < ext_ncount; i++) {

for(j = 0; j < ncount; j++) {

if(strcmp(ext_nlist[i].name, nlist[j].name) == 0) {

clb_to_vpack_net_mapping[i] = j;

vpack_to_clb_net_mapping[j] = i;

break;

}

}

assert(j != ncount);

}

if(saved_logical_blocks != NULL) {

free(saved_logical_blocks);

saved_logical_blocks = NULL;

free(saved_logical_nets);

saved_logical_nets = NULL;

}

/* Return blocks and nets */

*num_blocks = bcount;

*block_list = blist;

*num_nets = ext_ncount;

*net_list = ext_nlist;

}

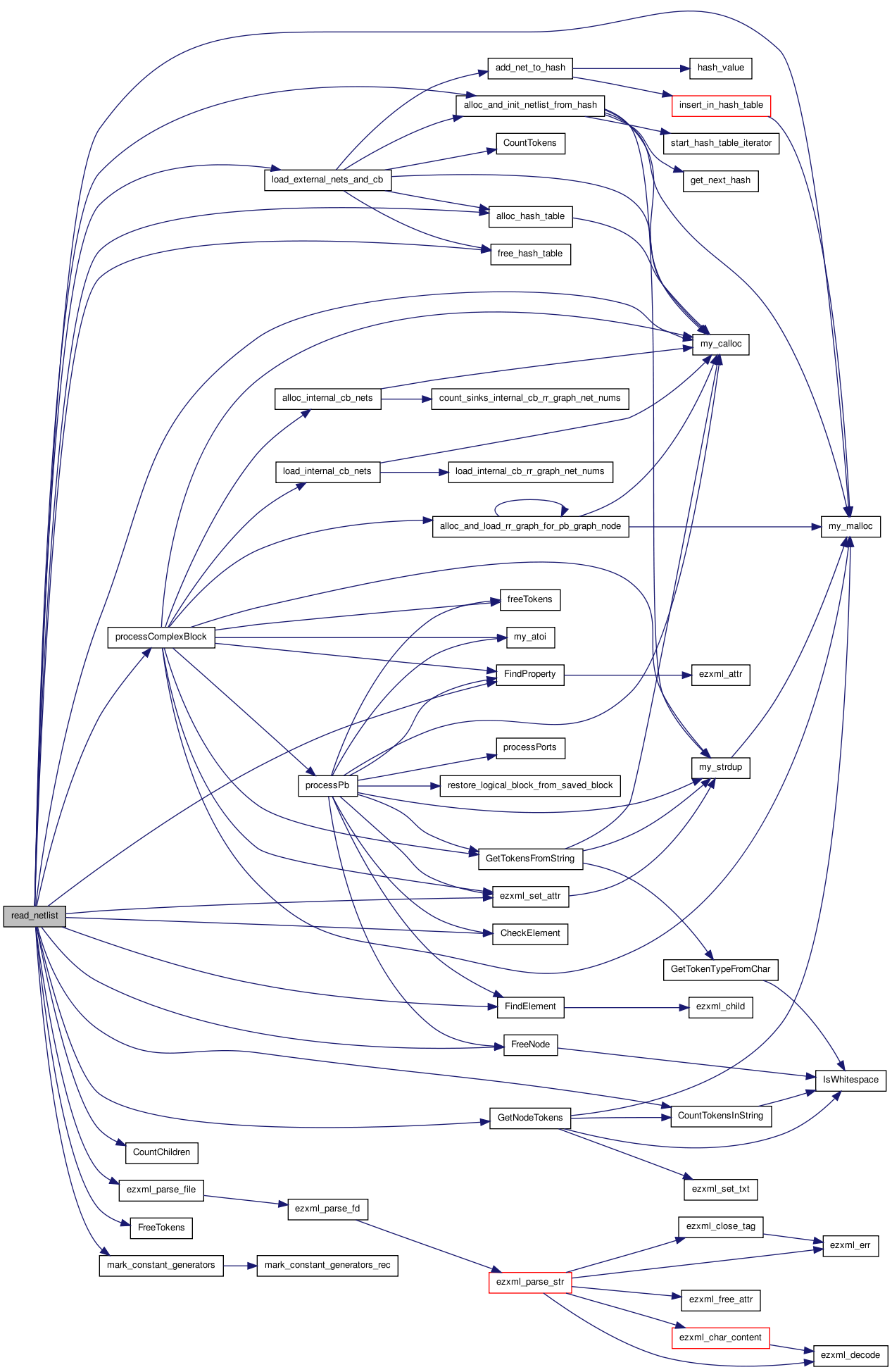

Here is the call graph for this function:

Here is the call graph for this function: Here is the caller graph for this function:

Here is the caller graph for this function: