vpr/SRC/pack/output_blif.h File Reference

This graph shows which files directly or indirectly include this file:

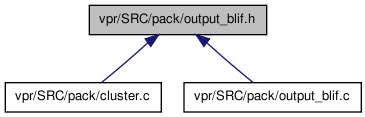

This graph shows which files directly or indirectly include this file:Go to the source code of this file.

Functions | |

| void | output_blif (t_block *clb, int num_clusters, boolean global_clocks, boolean *is_clock, char *out_fname, boolean skip_clustering) |

Function Documentation

| void output_blif | ( | t_block * | clb, |

| int | num_clusters, | ||

| boolean | global_clocks, | ||

| boolean * | is_clock, | ||

| char * | out_fname, | ||

| boolean | skip_clustering | ||

| ) |

This routine dumps out the output netlist in a format suitable for input to vpr. This routine also dumps out the internal structure of the cluster, in essentially a graph based format.

Definition at line 403 of file output_blif.c.

{

FILE *fpout;

int bnum, column;

struct s_linked_vptr *p_io_removed;

fpout = my_fopen(out_fname, "w", 0);

column = 0;

fprintf(fpout, ".model %s\n", blif_circuit_name);

/* Print out all input and output pads. */

fprintf(fpout, "\n.inputs ");

for(bnum = 0; bnum < num_logical_blocks; bnum++)

{

if(logical_block[bnum].type == VPACK_INPAD) {

print_string(logical_block[bnum].name, &column, fpout);

}

}

p_io_removed = circuit_p_io_removed;

while(p_io_removed) {

print_string((char*)p_io_removed->data_vptr, &column, fpout);

p_io_removed = p_io_removed->next;

}

column = 0;

fprintf(fpout, "\n.outputs ");

for(bnum = 0; bnum < num_logical_blocks; bnum++)

{

if(logical_block[bnum].type == VPACK_OUTPAD) {

/* remove output prefix "out:" */

print_string(logical_block[bnum].name + 4, &column, fpout);

}

}

column = 0;

fprintf(fpout, "\n\n");

print_clusters(clb, num_clusters, fpout);

fprintf(fpout, "\n.end\n");

fclose(fpout);

}

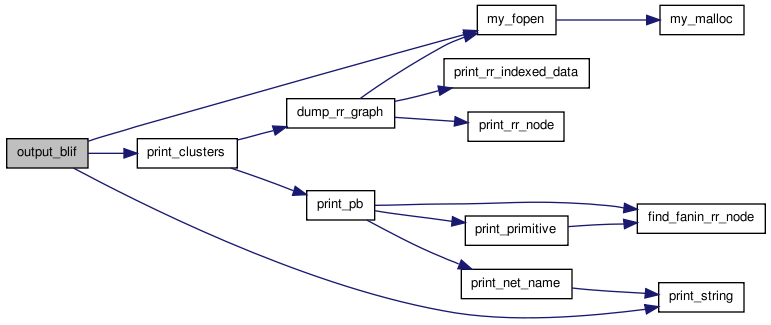

Here is the call graph for this function:

Here is the call graph for this function: Here is the caller graph for this function:

Here is the caller graph for this function: