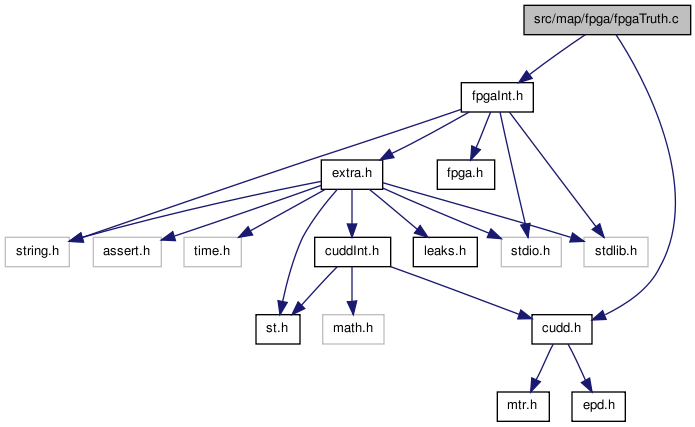

src/map/fpga/fpgaTruth.c File Reference

#include "fpgaInt.h"#include "cudd.h"

Go to the source code of this file.

Functions | |

| DdNode * | Fpga_TruthsCutBdd_rec (DdManager *dd, Fpga_Cut_t *pCut, Fpga_NodeVec_t *vVisited) |

| void * | Fpga_TruthsCutBdd (void *dd, Fpga_Cut_t *pCut) |

| void | Fpga_CutVolume_rec (Fpga_Cut_t *pCut, Fpga_NodeVec_t *vVisited) |

| int | Fpga_CutVolume (Fpga_Cut_t *pCut) |

Function Documentation

| int Fpga_CutVolume | ( | Fpga_Cut_t * | pCut | ) |

Function*************************************************************

Synopsis [Derives the truth table for one cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 137 of file fpgaTruth.c.

00138 { 00139 Fpga_NodeVec_t * vVisited; 00140 int Volume, i; 00141 assert( pCut->nLeaves > 1 ); 00142 // set the leaf variables 00143 for ( i = 0; i < pCut->nLeaves; i++ ) 00144 pCut->ppLeaves[i]->pCuts->fMark = 1; 00145 // recursively compute the function 00146 vVisited = Fpga_NodeVecAlloc( 10 ); 00147 Fpga_CutVolume_rec( pCut, vVisited ); 00148 // clean the marks 00149 for ( i = 0; i < pCut->nLeaves; i++ ) 00150 pCut->ppLeaves[i]->pCuts->fMark = 0; 00151 for ( i = 0; i < vVisited->nSize; i++ ) 00152 { 00153 pCut = (Fpga_Cut_t *)vVisited->pArray[i]; 00154 pCut->fMark = 0; 00155 } 00156 Volume = vVisited->nSize; 00157 printf( "%d ", Volume ); 00158 Fpga_NodeVecFree( vVisited ); 00159 return Volume; 00160 }

| void Fpga_CutVolume_rec | ( | Fpga_Cut_t * | pCut, | |

| Fpga_NodeVec_t * | vVisited | |||

| ) |

Function*************************************************************

Synopsis [Recursively derives the truth table for the cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 115 of file fpgaTruth.c.

00116 { 00117 assert( !Fpga_IsComplement(pCut) ); 00118 if ( pCut->fMark ) 00119 return; 00120 pCut->fMark = 1; 00121 Fpga_CutVolume_rec( Fpga_CutRegular(pCut->pOne), vVisited ); 00122 Fpga_CutVolume_rec( Fpga_CutRegular(pCut->pTwo), vVisited ); 00123 Fpga_NodeVecPush( vVisited, (Fpga_Node_t *)pCut ); 00124 }

| void* Fpga_TruthsCutBdd | ( | void * | dd, | |

| Fpga_Cut_t * | pCut | |||

| ) |

Function*************************************************************

Synopsis [Derives the truth table for one cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 76 of file fpgaTruth.c.

00077 { 00078 Fpga_NodeVec_t * vVisited; 00079 DdNode * bFunc; 00080 int i; 00081 assert( pCut->nLeaves > 1 ); 00082 // set the leaf variables 00083 for ( i = 0; i < pCut->nLeaves; i++ ) 00084 pCut->ppLeaves[i]->pCuts->uSign = (unsigned)Cudd_bddIthVar( dd, i ); 00085 // recursively compute the function 00086 vVisited = Fpga_NodeVecAlloc( 10 ); 00087 bFunc = Fpga_TruthsCutBdd_rec( dd, pCut, vVisited ); Cudd_Ref( bFunc ); 00088 // clean the intermediate BDDs 00089 for ( i = 0; i < pCut->nLeaves; i++ ) 00090 pCut->ppLeaves[i]->pCuts->uSign = 0; 00091 for ( i = 0; i < vVisited->nSize; i++ ) 00092 { 00093 pCut = (Fpga_Cut_t *)vVisited->pArray[i]; 00094 Cudd_RecursiveDeref( dd, (DdNode*)pCut->uSign ); 00095 pCut->uSign = 0; 00096 } 00097 // printf( "%d ", vVisited->nSize ); 00098 Fpga_NodeVecFree( vVisited ); 00099 Cudd_Deref( bFunc ); 00100 return bFunc; 00101 }

| DdNode* Fpga_TruthsCutBdd_rec | ( | DdManager * | dd, | |

| Fpga_Cut_t * | pCut, | |||

| Fpga_NodeVec_t * | vVisited | |||

| ) |

CFile****************************************************************

FileName [fpgaTruth.c]

PackageName [MVSIS 1.3: Multi-valued logic synthesis system.]

Synopsis [Technology mapping for variable-size-LUT FPGAs.]

Author [MVSIS Group]

Affiliation [UC Berkeley]

Date [Ver. 2.0. Started - August 18, 2004.]

Revision [

- Id

- fpgaTruth.c,v 1.4 2005/01/23 06:59:42 alanmi Exp

] DECLARATIONS /// FUNCTION DEFINITIONS ///Function*************************************************************

Synopsis [Recursively derives the truth table for the cut.]

Description []

SideEffects []

SeeAlso []

Definition at line 41 of file fpgaTruth.c.

00042 { 00043 DdNode * bFunc, * bFunc0, * bFunc1; 00044 assert( !Fpga_IsComplement(pCut) ); 00045 // if the cut is visited, return the result 00046 if ( pCut->uSign ) 00047 return (DdNode *)pCut->uSign; 00048 // compute the functions of the children 00049 bFunc0 = Fpga_TruthsCutBdd_rec( dd, Fpga_CutRegular(pCut->pOne), vVisited ); Cudd_Ref( bFunc0 ); 00050 bFunc0 = Cudd_NotCond( bFunc0, Fpga_CutIsComplement(pCut->pOne) ); 00051 bFunc1 = Fpga_TruthsCutBdd_rec( dd, Fpga_CutRegular(pCut->pTwo), vVisited ); Cudd_Ref( bFunc1 ); 00052 bFunc1 = Cudd_NotCond( bFunc1, Fpga_CutIsComplement(pCut->pTwo) ); 00053 // get the function of the cut 00054 bFunc = Cudd_bddAnd( dd, bFunc0, bFunc1 ); Cudd_Ref( bFunc ); 00055 bFunc = Cudd_NotCond( bFunc, pCut->Phase ); 00056 Cudd_RecursiveDeref( dd, bFunc0 ); 00057 Cudd_RecursiveDeref( dd, bFunc1 ); 00058 assert( pCut->uSign == 0 ); 00059 pCut->uSign = (unsigned)bFunc; 00060 // add this cut to the visited list 00061 Fpga_NodeVecPush( vVisited, (Fpga_Node_t *)pCut ); 00062 return bFunc; 00063 }

1.6.1

1.6.1