2023-09-04

Welcome to ELEX 2117. Our first lecture will be on Wednesday, September 6.

Labs will begin the week of September 11. Parts kits for the labs will be available for purchase from the BCIT bookstore for $6.95. These are only available to students registered in the course -- you will need to ask for the "ELEX 2117 Parts Kit" at the front counter and show ID. You will also need some components from your Level 1 parts kit (the EPM240 CPLD board, USB-Blaster, Dupont/Berg jumper wires, and some space on your breadboard).

2023-09-04

|

ELEX |

Day: |

Mon |

Tue |

Wed |

Thu |

Fri |

|

|

Lectures: |

1:30 |

|

9:30 |

|

9:30 |

|

week |

Lab Sets: |

2A (10:30) |

2D (8:30) |

|

2C (10:30) |

|

|

1 |

Sep 04 |

holiday |

|

|

|

|

|

2 |

Sep 11 |

L0 |

|

|

|

|

|

3 |

Sep 18 |

L1 |

|

|

|

Q1 |

|

4 |

Sep 25 |

L2 |

|

|

|

|

|

5 |

Oct 02 |

holiday |

|

|

|

MT1 |

|

6 |

Oct 09 |

holiday |

|

|

|

|

|

7 |

Oct 16 |

L3 |

|

|

|

Q2 |

|

8 |

Oct 23 |

L4 |

|

|

|

|

|

9 |

Oct 30 |

L5 |

|

|

|

MT2 |

|

10 |

Nov 06 |

L6 |

|

|

|

|

|

11 |

Nov 13 |

holiday |

WD |

|

|

|

|

12 |

Nov 20 |

L7 |

|

|

|

Q3 |

|

13 |

Nov 27 |

L8 |

|

|

|

|

|

14 |

Dec 04 |

|

|

|

|

|

|

15 |

Dec 11 |

exams |

exams |

exams |

exams |

exams |

|

Ln=Lab n, Qn = Quiz n, MTn=Midterm n, WD = Course withdrawal deadline. |

||||||

Tentative, subject to change.

2023-09-19

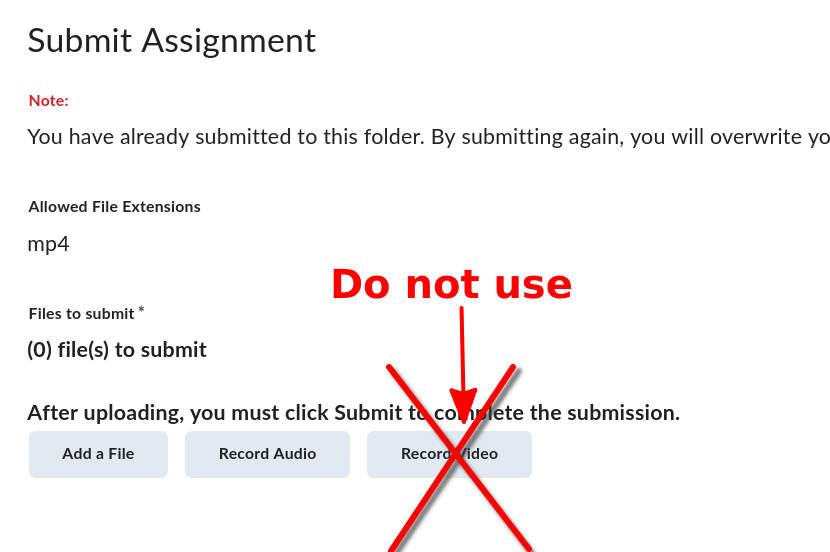

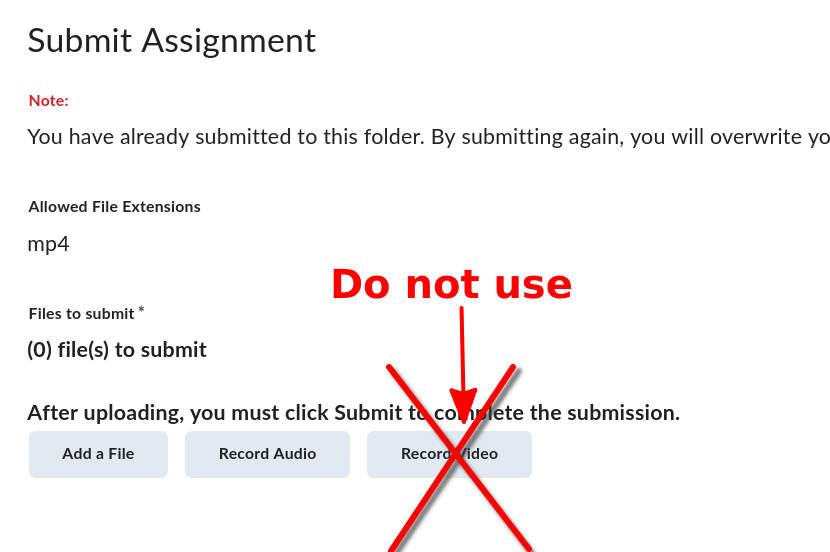

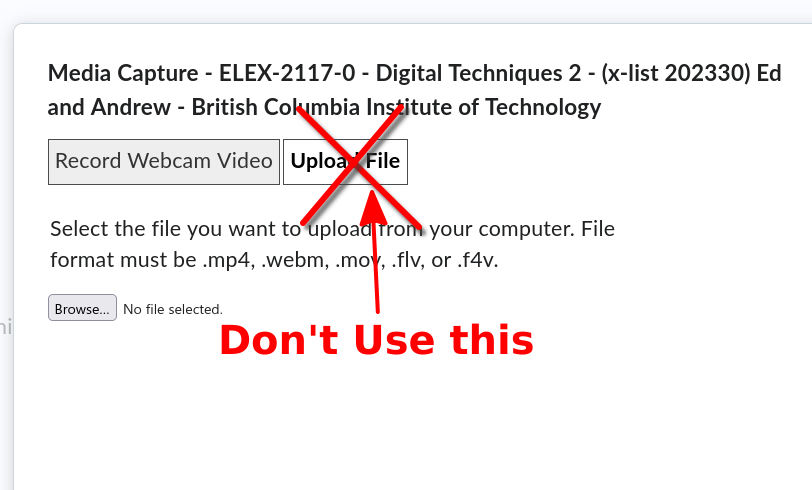

When you submit a video, do not use the "Record Video" button:

not even to upload an existing video file:

Videos uploaded this way can't be downloaded and will not get marked.

Instead, save your video to a file (with .mp4 extension). Then upload it and verify that you can download and view the file with your browser.

Try to take the video in a suitable format and orientation. But if necessary you can use a simple video editor such as avidemux to convert the file (trim, crop, rotate, change encoding, etc).

2023-09-21

Quiz 1 will cover Lecture 1 up to the assign statement.

It will be open-book but all electronics device other than calculators must be left at side, back, or front of the room. Please wait outside the classroom (SW01-1021) until I ask you to come in. This will allow me to put out the exam papers in alphabetical order. You must write your own exam at the location where it is placed.

2023-09-27

The proctored lab sessions are set to begin this weekend.

Sessions will be held on weekends only this term in SW1-3055. Proctor lab sessions are available to all ECET/ROBT Level 1 and Level 2 students.

|

DAY |

LAB |

HOURS |

SESSION |

|

Saturday |

SW1-3055 |

12:00 – 17:00 |

A |

|

Sunday |

SW1-3055 |

12:00 – 17:00 |

B |

Start Session: (Week 4) Saturday, Sep. 30, 2023

Final Session: (Week 13) Sunday, Dec. 03, 2023

|

Proctor* |

Wk4 |

Wk5 |

Wk6 |

Wk7 |

Wk8 |

Wk9 |

Wk10 |

Wk11 |

Wk12 |

Wk13 |

|

Faniel Yemane |

A |

B |

A |

B |

A |

B |

A |

B |

A |

B |

|

Federico Sarabia |

B |

A |

B |

A |

B |

A |

B |

A |

B |

A |

*May be subject to change

2023-10-04

The first midterm exam will be held on Friday, October 6 at 3:30 PM (not the regular lecture time) in SW03-1750 (not the regular lecture room).

The exam is nominally one hour but is not time-limited (the room is booked until 6:20).

The exam will cover all material up to and including "State Encodings" in Lecture 2 (with the exception of component instantiations and arrays of arrays in Lecture 1 that we did not cover in class).

2023-10-17

As stated at the top of the Lab3 notes:

Note: You must attend your lab session and demonstrate your solution to get marks for completing this lab.

and in the section titled "Lab Demonstration":

You must demonstrate your lab during your scheduled lab period. I recommend that you have working design before coming to your lab session. After successfully demonstrating the behaviour described above, the lab instructor will ask you to make a simple change to the behaviour of your design to demonstrate your understanding. Successfully making the change will count for half of this lab’s completion mark.

This lab's marking policy will not be changed so as to be fair to students who followed the recommendation to complete the lab beforehand.

Remember that the lowest and highest lab marks will not be counted. Therefore, not completing this lab may not affect your final mark.

2023-10-19

Quiz 2 will be held tomorrow, Friday, October 20, at 9:30 AM in SW1-1021 (the regular lecture time and location).

It will cover Lecture 5 "More Verilog". The learning objectives are:

After this lecture you should be able to: convert between high/low logic levels and true/false truth values for active-high and active-low interfaces, declare modules with parameters and ports, and instantiate modules using positional, named and wildcard parameters and signals.

You can take up to one hour to complete the quiz (and should have plenty of time). You can leave when you are done but cannot leave for the first 20 minutes or arrive more than 20 minutes late. As usual, there will be assigned seating and multiple versions of each question. The test is open-book but no electronic devices other than a calculator are allowed.

2023-10-30

The second midterm exam will be held on Friday, November 3 at 3:30 PM (not the regular lecture time) in SW03-1750 (not the regular lecture room).

The exam is nominally one hour but is not time-limited (the room is booked until 6:20).

The exam will cover all material from "State Encodings" in Lecture 2 to the end of Lecture 7 (Interfaces).

2023-11-06

Due to a scheduling conflict, office hours on Tuesday, November 7 will be held from 4:30 to 5:20 PM (Level 2 students should be free then).

2023-11-10

If you left your first-year parts kit in SW1-1025 on Friday, Nov. 10 then see Lito.

2023-11-15

I need to the reschedule office hours for this Friday, November 17 at 12:30 (only) to Monday, November 20 at 1:00.

2023-11-16

The final exam for ELEX2117 will be held on Friday, December 15 from 0900 to 1200 in SW03-1750.

2023-11-17

Due to a scheduling conflict I need to reschedule the office hours on Tuesday, November 21 at 12:30 to Thursday, November 23 (also from 12:30 to 1:20).

2023-11-21

Quiz 3 will be held on Friday, November 24, at 9:30 AM in SW1-1021 (the regular lecture time and location).

It will cover Lectures 8 (Timing Analysis), Lecture 9 (Implementation of Digital Logic), and Lecture 10 (Analog Interfaces) up to, but not including, the section Digital to Analog Converters.

You can take up to one hour to complete the quiz (and should have plenty of time). You can leave when you are done but cannot leave for the first 20 minutes or arrive more than 20 minutes late. As usual, there will be assigned seating and multiple versions of each question. The test is open-book but no electronic devices other than a calculator are allowed.

2023-12-16

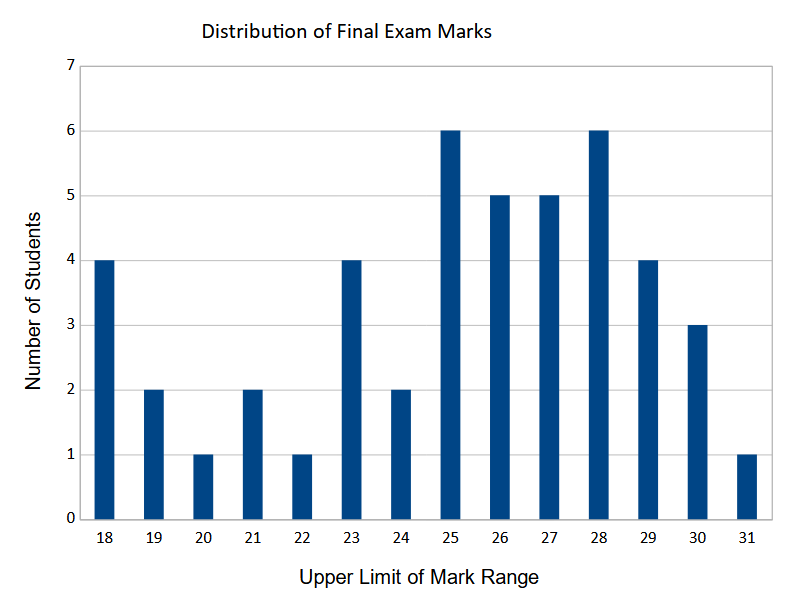

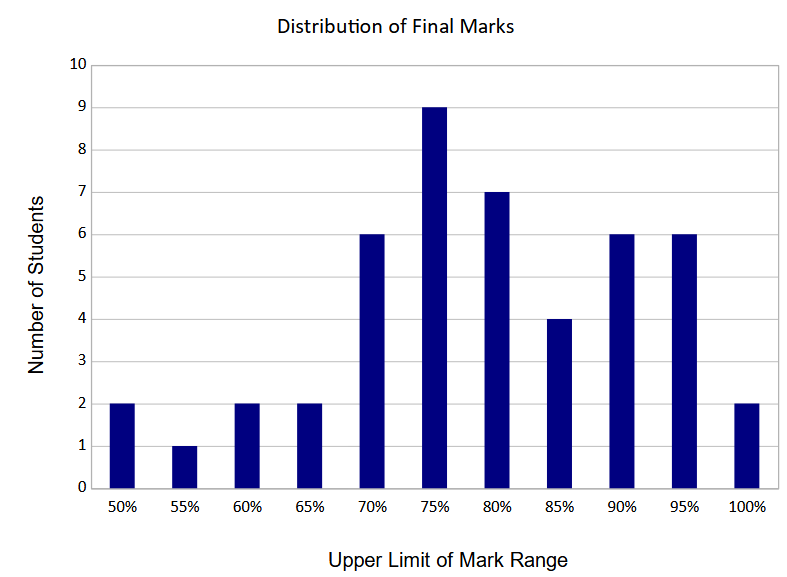

The final exam has been marked and emailed back. The solutions and the marking scheme have been posted. Let me know as soon as possible if you see any errors (before noon on Monday if at all possible).

The unofficial final marks have been computed but are subject to change.

The distributions of the final exam marks and unofficial final course marks are shown below.