Efficient Architecture

This project investigates future architectures which provide general purpose computing orders of magnitude more efficiently versus today's superscalar out-of-order CPUs. This project was started while I was on sabbatical at Stanford during 2012-2013. The initial approach explored was rethinking CPU architecture remove sources of inefficiency both in the compute core and the memory hierarchy. The results of this initial approach have been published in several of the papers found below.

More recently, motivated by the increasing use of field programmable gate arrays (FPGAs) inside the datacenter, we have explored how FPGA architecture should change to support a wider range of applications. More broadly I am interested in investigating alternative architectures that balance easy of programming with hardware efficiency. Funding for this research is provided in part by an NSERC Discovery Accelerator.

Talks

Efficient and Easily Programmable Accelerator Architectures (PDF) - invited talk, Stanford Pervasive Parallelism Lab Retreat, May 2013Publications

|

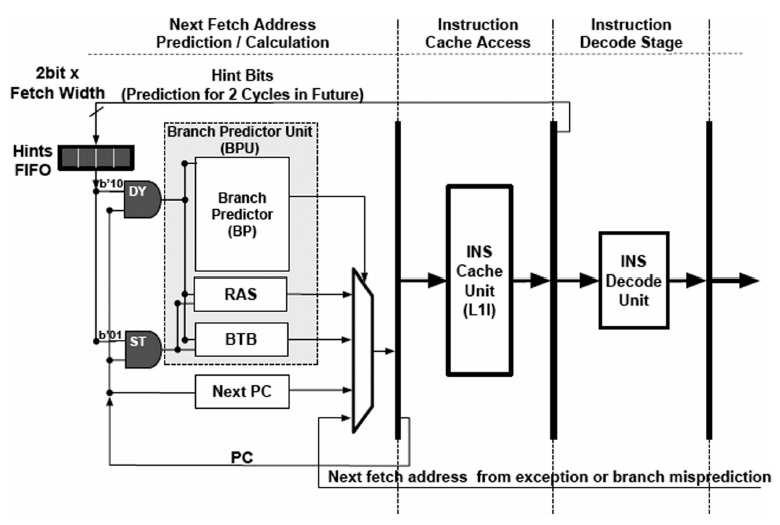

Milad Mohammadi, Song Han, Ehsan Atoofian, Amirali Baniasadi, Tor M. Aamodt, William J. Dally, Energy Efficient On-Demand Dynamic Branch Prediction Models, IEEE Transactions on Computers, pp. 453 - 465, v69, n3, March 1, 2020. |

|

Shadi Asadi, Jennifer Ongko, Tor M. Aamodt, A State Machine Block for High-Level Synthesis, In proceedings of the IEEE International Conference on Field Programmable Technology (FPT), Melbourne, Australia, December 11-13, 2017. |

|

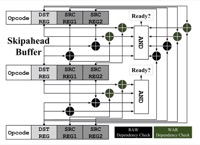

Milad Mohammadi, Tor M Aamodt, William J Dally, CG-OoO: Energy-Efficient Coarse-Grain Out-of-Order Execution Near In-Order Energy with Near Out-of-Order Performance, ACM Transactions on Architecture and Code Optimization (TACO), Volume 14, Issue 4, December 2017. |

|

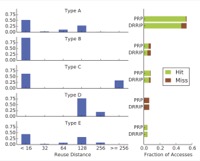

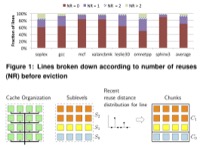

Subhasis Das, Tor M Aamodt, William J Dally, Reuse distance-based probabilistic cache replacement, ACM Transactions on Architecture and Code Optimization (TACO), Volume 12, Issue 4, January 2016. |

|

Subhasis Das, Tor M. Aamodt, William J. Dally, SLIP: Reducing Wire Energy in the Memory Hierarchy, in proceedings of the ACM/IEEE International Symposium on Computer Architecture (ISCA 2015), pp. 349-361, Portland, OR, June 13-17, 2015. (acceptance rate: 58/305 ≈ 19.0%) |

|

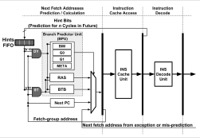

Milad Mohammadi, Song Hang, Tor M. Aamodt, William J. Dally, On-Demand Dynamic Branch Prediction, in IEEE Computer Architecture Letters, vol. 14, no. 1, pp. 50-53, June 2015. |