netlist_create_from_ast.h File Reference

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Functions | |

| void | create_netlist () |

| void | connect_memory_and_alias (ast_node_t *hb_instance, char *instance_name_prefix) |

Function Documentation

| void connect_memory_and_alias | ( | ast_node_t * | hb_instance, | |

| char * | instance_name_prefix | |||

| ) |

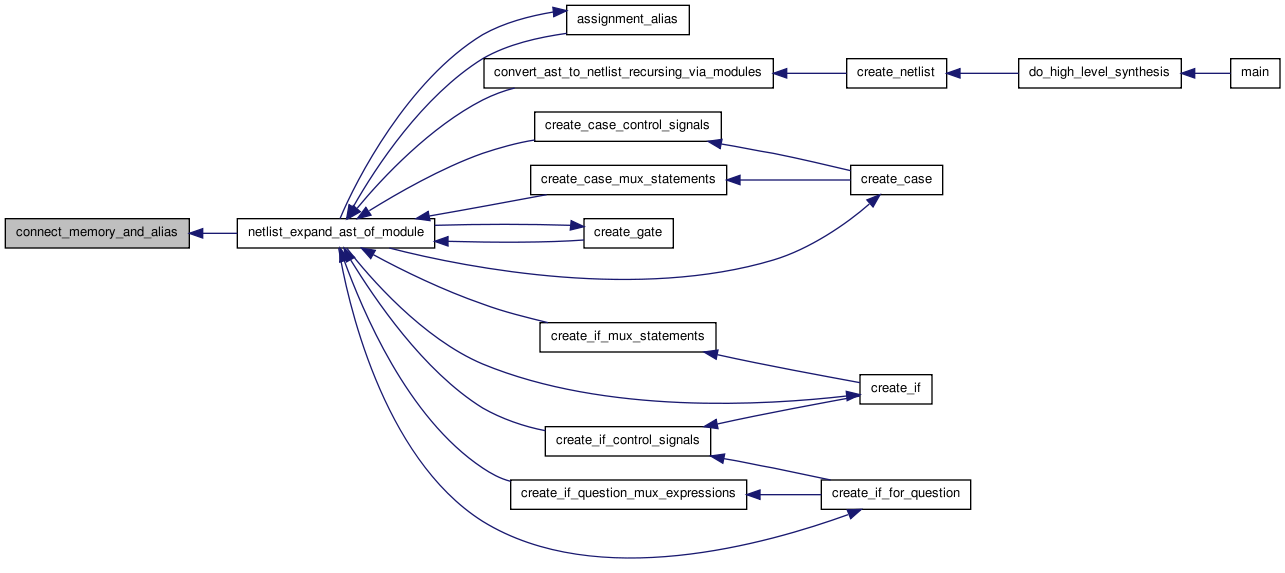

Here is the caller graph for this function:

| void create_netlist | ( | ) |

Definition at line 129 of file netlist_create_from_ast.c.

00130 { 00131 /* just build all the fundamental elements, and then hookup with port definitions...every net has a named net as a variable instance...even modules...the only trick with modules will be instance names. There are a few implied nets as in Muxes for cases, signals for flip-flops and memories */ 00132 00133 /* we will find the top module */ 00134 top_module = find_top_module(); 00135 if (!global_args.output_file) 00136 { 00137 global_args.output_file = malloc(strlen(top_module->children[0]->types.identifier) + 5 + 1); 00138 sprintf(global_args.output_file, "%s.blif", top_module->children[0]->types.identifier); 00139 } 00140 00141 /* Since the modules are in a tree, we will bottom up build the netlist. Essentially, we will go to the leafs of the module tree, build them upwards such that when we search for the nets, we will find them and can hook them up at that point */ 00142 /* PASS 1 - we make all the nets based on registers defined in modules */ 00143 00144 /* initialize the string caches that hold the aliasing of module nets and input pins */ 00145 output_nets_sc = sc_new_string_cache(); 00146 input_nets_sc = sc_new_string_cache(); 00147 /* initialize the storage of the top level drivers. Assigned in create_top_driver_nets */ 00148 verilog_netlist = allocate_netlist(); 00149 00150 /* now recursively parse the modules by going through the tree of modules starting at top */ 00151 create_top_driver_nets(top_module, "top"); 00152 convert_ast_to_netlist_recursing_via_modules(top_module, "top", 0); 00153 create_top_output_nodes(top_module, "top"); 00154 00155 /* now look for high-level signals */ 00156 look_for_clocks(verilog_netlist); 00157 }

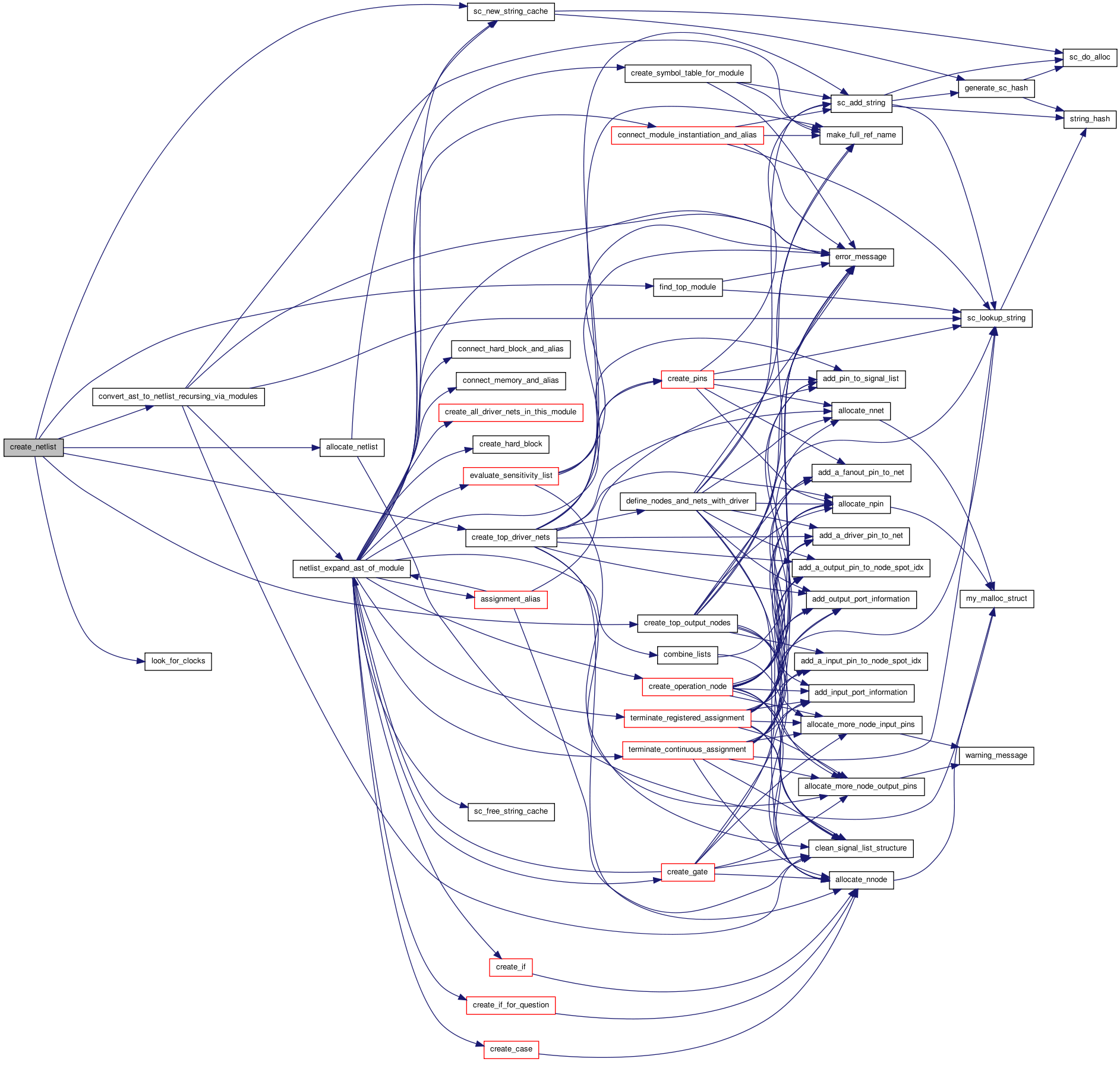

Here is the call graph for this function:

Here is the caller graph for this function:

1.6.3

1.6.3