src/aig/fra/fraInd.c File Reference

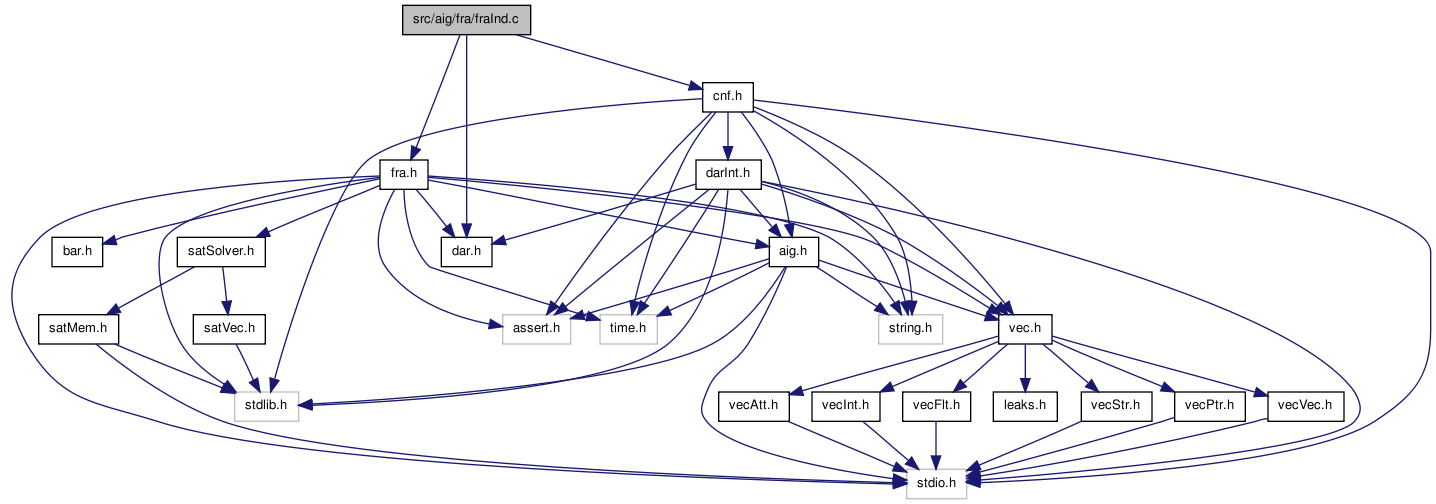

#include "fra.h"#include "cnf.h"#include "dar.h"

Go to the source code of this file.

Functions | |

| void | Fra_FraigInductionRewrite (Fra_Man_t *p) |

| static void | Fra_FramesConstrainNode (Aig_Man_t *pManFraig, Aig_Obj_t *pObj, int iFrame) |

| Aig_Man_t * | Fra_FramesWithClasses (Fra_Man_t *p) |

| void | Fra_FramesAddMore (Aig_Man_t *p, int nFrames) |

| Aig_Man_t * | Fra_FraigInduction (Aig_Man_t *pManAig, int nFramesP, int nFramesK, int nMaxImps, int fRewrite, int fUseImps, int fLatchCorr, int fWriteImps, int fVerbose, int *pnIter) |

Function Documentation

| Aig_Man_t* Fra_FraigInduction | ( | Aig_Man_t * | pManAig, | |

| int | nFramesP, | |||

| int | nFramesK, | |||

| int | nMaxImps, | |||

| int | fRewrite, | |||

| int | fUseImps, | |||

| int | fLatchCorr, | |||

| int | fWriteImps, | |||

| int | fVerbose, | |||

| int * | pnIter | |||

| ) |

Function*************************************************************

Synopsis [Performs choicing of the AIG.]

Description []

SideEffects []

SeeAlso []

Definition at line 247 of file fraInd.c.

00248 { 00249 int fUseSimpleCnf = 0; 00250 int fUseOldSimulation = 0; 00251 // other paramaters affecting performance 00252 // - presence of FRAIGing in Abc_NtkDarSeqSweep() 00253 // - using distance-1 patterns in Fra_SmlAssignDist1() 00254 // - the number of simulation patterns 00255 // - the number of BMC frames 00256 00257 Fra_Man_t * p; 00258 Fra_Par_t Pars, * pPars = &Pars; 00259 Aig_Obj_t * pObj; 00260 Cnf_Dat_t * pCnf; 00261 Aig_Man_t * pManAigNew; 00262 int nNodesBeg, nRegsBeg; 00263 int nIter, i, clk = clock(), clk2; 00264 00265 if ( Aig_ManNodeNum(pManAig) == 0 ) 00266 { 00267 if ( pnIter ) *pnIter = 0; 00268 return Aig_ManDup(pManAig, 1); 00269 } 00270 assert( Aig_ManLatchNum(pManAig) == 0 ); 00271 assert( Aig_ManRegNum(pManAig) > 0 ); 00272 assert( nFramesK > 0 ); 00273 //Aig_ManShow( pManAig, 0, NULL ); 00274 00275 nNodesBeg = Aig_ManNodeNum(pManAig); 00276 nRegsBeg = Aig_ManRegNum(pManAig); 00277 00278 // enhance the AIG by adding timeframes 00279 // Fra_FramesAddMore( pManAig, 3 ); 00280 00281 // get parameters 00282 Fra_ParamsDefaultSeq( pPars ); 00283 pPars->nFramesP = nFramesP; 00284 pPars->nFramesK = nFramesK; 00285 pPars->nMaxImps = nMaxImps; 00286 pPars->fVerbose = fVerbose; 00287 pPars->fRewrite = fRewrite; 00288 pPars->fLatchCorr = fLatchCorr; 00289 pPars->fUseImps = fUseImps; 00290 pPars->fWriteImps = fWriteImps; 00291 00292 // start the fraig manager for this run 00293 p = Fra_ManStart( pManAig, pPars ); 00294 // derive and refine e-classes using K initialized frames 00295 if ( fUseOldSimulation ) 00296 { 00297 if ( pPars->nFramesP > 0 ) 00298 { 00299 pPars->nFramesP = 0; 00300 printf( "Fra_FraigInduction(): Prefix cannot be used.\n" ); 00301 } 00302 p->pSml = Fra_SmlStart( pManAig, 0, pPars->nFramesK + 1, pPars->nSimWords ); 00303 Fra_SmlSimulate( p, 1 ); 00304 } 00305 else 00306 { 00307 // bug: r iscas/blif/s5378.blif ; st; ssw -v 00308 // bug: r iscas/blif/s1238.blif ; st; ssw -v 00309 // refine the classes with more simulation rounds 00310 if ( fVerbose ) 00311 printf( "Simulating %d AIG nodes for %d cycles ... ", Aig_ManNodeNum(pManAig), pPars->nFramesP + 32 ); 00312 p->pSml = Fra_SmlSimulateSeq( pManAig, pPars->nFramesP, 32, 1 ); //pPars->nFramesK + 1, 1 ); 00313 if ( fVerbose ) 00314 { 00315 PRT( "Time", clock() - clk ); 00316 } 00317 Fra_ClassesPrepare( p->pCla, p->pPars->fLatchCorr ); 00318 // Fra_ClassesPostprocess( p->pCla ); 00319 // allocate new simulation manager for simulating counter-examples 00320 Fra_SmlStop( p->pSml ); 00321 p->pSml = Fra_SmlStart( pManAig, 0, pPars->nFramesK + 1, pPars->nSimWords ); 00322 } 00323 00324 // select the most expressive implications 00325 if ( pPars->fUseImps ) 00326 p->pCla->vImps = Fra_ImpDerive( p, 5000000, pPars->nMaxImps, pPars->fLatchCorr ); 00327 00328 // perform BMC (for the min number of frames) 00329 Fra_BmcPerform( p, pPars->nFramesP, pPars->nFramesK+1 ); // +1 is needed to prevent non-refinement 00330 //Fra_ClassesPrint( p->pCla, 1 ); 00331 // if ( p->vCex == NULL ) 00332 // p->vCex = Vec_IntAlloc( 1000 ); 00333 00334 p->nLitsBeg = Fra_ClassesCountLits( p->pCla ); 00335 p->nNodesBeg = nNodesBeg; // Aig_ManNodeNum(pManAig); 00336 p->nRegsBeg = nRegsBeg; // Aig_ManRegNum(pManAig); 00337 00338 // dump AIG of the timeframes 00339 // pManAigNew = Fra_ClassesDeriveAig( p->pCla, pPars->nFramesK ); 00340 // Aig_ManDumpBlif( pManAigNew, "frame_aig.blif" ); 00341 // Fra_ManPartitionTest2( pManAigNew ); 00342 // Aig_ManStop( pManAigNew ); 00343 00344 // iterate the inductive case 00345 p->pCla->fRefinement = 1; 00346 for ( nIter = 0; p->pCla->fRefinement; nIter++ ) 00347 { 00348 int nLitsOld = Fra_ClassesCountLits(p->pCla); 00349 int nImpsOld = p->pCla->vImps? Vec_IntSize(p->pCla->vImps) : 0; 00350 // mark the classes as non-refined 00351 p->pCla->fRefinement = 0; 00352 // derive non-init K-timeframes while implementing e-classes 00353 clk2 = clock(); 00354 p->pManFraig = Fra_FramesWithClasses( p ); 00355 p->timeTrav += clock() - clk2; 00356 //Aig_ManDumpBlif( p->pManFraig, "testaig.blif" ); 00357 00358 // perform AIG rewriting 00359 if ( p->pPars->fRewrite ) 00360 Fra_FraigInductionRewrite( p ); 00361 00362 // convert the manager to SAT solver (the last nLatches outputs are inputs) 00363 if ( fUseSimpleCnf || pPars->fUseImps ) 00364 pCnf = Cnf_DeriveSimple( p->pManFraig, Aig_ManRegNum(p->pManFraig) ); 00365 else 00366 pCnf = Cnf_Derive( p->pManFraig, Aig_ManRegNum(p->pManFraig) ); 00367 //Cnf_DataWriteIntoFile( pCnf, "temp.cnf", 1 ); 00368 00369 p->pSat = Cnf_DataWriteIntoSolver( pCnf ); 00370 p->nSatVars = pCnf->nVars; 00371 assert( p->pSat != NULL ); 00372 if ( p->pSat == NULL ) 00373 printf( "Fra_FraigInduction(): Computed CNF is not valid.\n" ); 00374 if ( pPars->fUseImps ) 00375 { 00376 Fra_ImpAddToSolver( p, p->pCla->vImps, pCnf->pVarNums ); 00377 if ( p->pSat == NULL ) 00378 printf( "Fra_FraigInduction(): Adding implicationsn to CNF led to a conflict.\n" ); 00379 } 00380 00381 // set the pointers to the manager 00382 Aig_ManForEachObj( p->pManFraig, pObj, i ) 00383 pObj->pData = p; 00384 00385 // prepare solver for fraiging the last timeframe 00386 Fra_ManClean( p, Aig_ManObjNumMax(p->pManFraig) + Aig_ManNodeNum(p->pManAig) ); 00387 00388 // transfer PI/LO variable numbers 00389 Aig_ManForEachObj( p->pManFraig, pObj, i ) 00390 { 00391 if ( pCnf->pVarNums[pObj->Id] == -1 ) 00392 continue; 00393 Fra_ObjSetSatNum( pObj, pCnf->pVarNums[pObj->Id] ); 00394 Fra_ObjSetFaninVec( pObj, (void *)1 ); 00395 } 00396 Cnf_DataFree( pCnf ); 00397 00398 // report the intermediate results 00399 if ( fVerbose ) 00400 { 00401 printf( "%3d : Const = %6d. Class = %6d. L = %6d. LR = %6d. ", 00402 nIter, Vec_PtrSize(p->pCla->vClasses1), Vec_PtrSize(p->pCla->vClasses), 00403 Fra_ClassesCountLits(p->pCla), p->pManFraig->nAsserts ); 00404 if ( p->pCla->vImps ) 00405 printf( "I = %6d. ", Vec_IntSize(p->pCla->vImps) ); 00406 printf( "NR = %6d.\n", Aig_ManNodeNum(p->pManFraig) ); 00407 } 00408 00409 // perform sweeping 00410 p->nSatCallsRecent = 0; 00411 p->nSatCallsSkipped = 0; 00412 Fra_FraigSweep( p ); 00413 00414 // Sat_SolverPrintStats( stdout, p->pSat ); 00415 00416 // remove FRAIG and SAT solver 00417 Aig_ManStop( p->pManFraig ); p->pManFraig = NULL; 00418 sat_solver_delete( p->pSat ); p->pSat = NULL; 00419 memset( p->pMemFraig, 0, sizeof(Aig_Obj_t *) * p->nSizeAlloc * p->nFramesAll ); 00420 // printf( "Recent SAT called = %d. Skipped = %d.\n", p->nSatCallsRecent, p->nSatCallsSkipped ); 00421 assert( p->vTimeouts == NULL ); 00422 if ( p->vTimeouts ) 00423 printf( "Fra_FraigInduction(): SAT solver timed out!\n" ); 00424 // check if refinement has happened 00425 // p->pCla->fRefinement = (int)(nLitsOld != Fra_ClassesCountLits(p->pCla)); 00426 if ( p->pCla->fRefinement && 00427 nLitsOld == Fra_ClassesCountLits(p->pCla) && 00428 nImpsOld == (p->pCla->vImps? Vec_IntSize(p->pCla->vImps) : 0) ) 00429 { 00430 printf( "Fra_FraigInduction(): Internal error. The result may not verify.\n" ); 00431 break; 00432 } 00433 } 00434 /* 00435 // verify implications using simulation 00436 if ( p->pCla->vImps && Vec_IntSize(p->pCla->vImps) ) 00437 { 00438 int Temp, clk = clock(); 00439 if ( Temp = Fra_ImpVerifyUsingSimulation( p ) ) 00440 printf( "Implications failing the simulation test = %d (out of %d). ", Temp, Vec_IntSize(p->pCla->vImps) ); 00441 else 00442 printf( "All %d implications have passed the simulation test. ", Vec_IntSize(p->pCla->vImps) ); 00443 PRT( "Time", clock() - clk ); 00444 } 00445 */ 00446 00447 // move the classes into representatives and reduce AIG 00448 clk2 = clock(); 00449 // Fra_ClassesPrint( p->pCla, 1 ); 00450 Fra_ClassesSelectRepr( p->pCla ); 00451 Fra_ClassesCopyReprs( p->pCla, p->vTimeouts ); 00452 pManAigNew = Aig_ManDupRepr( pManAig, 0 ); 00453 // add implications to the manager 00454 if ( fWriteImps && p->pCla->vImps && Vec_IntSize(p->pCla->vImps) ) 00455 Fra_ImpRecordInManager( p, pManAigNew ); 00456 // cleanup the new manager 00457 Aig_ManSeqCleanup( pManAigNew ); 00458 // Aig_ManCountMergeRegs( pManAigNew ); 00459 p->timeTrav += clock() - clk2; 00460 p->timeTotal = clock() - clk; 00461 // get the final stats 00462 p->nLitsEnd = Fra_ClassesCountLits( p->pCla ); 00463 p->nNodesEnd = Aig_ManNodeNum(pManAigNew); 00464 p->nRegsEnd = Aig_ManRegNum(pManAigNew); 00465 // free the manager 00466 Fra_ManStop( p ); 00467 // check the output 00468 // if ( Aig_ManPoNum(pManAigNew) - Aig_ManRegNum(pManAigNew) == 1 ) 00469 // if ( Aig_ObjChild0( Aig_ManPo(pManAigNew,0) ) == Aig_ManConst0(pManAigNew) ) 00470 // printf( "Proved output constant 0.\n" ); 00471 if ( pnIter ) *pnIter = nIter; 00472 return pManAigNew; 00473 }

| void Fra_FraigInductionRewrite | ( | Fra_Man_t * | p | ) |

CFile****************************************************************

FileName [fraInd.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [New FRAIG package.]

Synopsis [Inductive prover.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 30, 2007.]

Revision [

- Id

- fraInd.c,v 1.00 2007/06/30 00:00:00 alanmi Exp

] DECLARATIONS /// FUNCTION DEFINITIONS ///Function*************************************************************

Synopsis [Performs AIG rewriting on the constaint manager.]

Description []

SideEffects []

SeeAlso []

Definition at line 44 of file fraInd.c.

00045 { 00046 Aig_Man_t * pTemp; 00047 Aig_Obj_t * pObj, * pObjPo; 00048 int nTruePis, k, i, clk = clock(); 00049 // perform AIG rewriting on the speculated frames 00050 pTemp = Aig_ManDup( p->pManFraig, 0 ); 00051 // pTemp = Dar_ManRwsat( pTemp, 1, 0 ); 00052 pTemp = Dar_ManRewriteDefault( pTemp ); 00053 // printf( "Before = %6d. After = %6d.\n", Aig_ManNodeNum(p->pManFraig), Aig_ManNodeNum(pTemp) ); 00054 //Aig_ManDumpBlif( p->pManFraig, "1.blif" ); 00055 //Aig_ManDumpBlif( pTemp, "2.blif" ); 00056 // Fra_FramesWriteCone( pTemp ); 00057 // Aig_ManStop( pTemp ); 00058 // transfer PI/register pointers 00059 assert( p->pManFraig->nRegs == pTemp->nRegs ); 00060 assert( p->pManFraig->nAsserts == pTemp->nAsserts ); 00061 nTruePis = Aig_ManPiNum(p->pManAig) - Aig_ManRegNum(p->pManAig); 00062 memset( p->pMemFraig, 0, sizeof(Aig_Obj_t *) * p->nSizeAlloc * p->nFramesAll ); 00063 Fra_ObjSetFraig( Aig_ManConst1(p->pManAig), p->pPars->nFramesK, Aig_ManConst1(pTemp) ); 00064 Aig_ManForEachPiSeq( p->pManAig, pObj, i ) 00065 Fra_ObjSetFraig( pObj, p->pPars->nFramesK, Aig_ManPi(pTemp,nTruePis*p->pPars->nFramesK+i) ); 00066 k = 0; 00067 assert( Aig_ManRegNum(p->pManAig) == Aig_ManPoNum(pTemp) - pTemp->nAsserts ); 00068 Aig_ManForEachLoSeq( p->pManAig, pObj, i ) 00069 { 00070 pObjPo = Aig_ManPo(pTemp, pTemp->nAsserts + k++); 00071 Fra_ObjSetFraig( pObj, p->pPars->nFramesK, Aig_ObjChild0(pObjPo) ); 00072 } 00073 // exchange 00074 Aig_ManStop( p->pManFraig ); 00075 p->pManFraig = pTemp; 00076 p->timeRwr += clock() - clk; 00077 }

| void Fra_FramesAddMore | ( | Aig_Man_t * | p, | |

| int | nFrames | |||

| ) |

Function*************************************************************

Synopsis [Prepares the inductive case with speculative reduction.]

Description []

SideEffects []

SeeAlso []

Definition at line 192 of file fraInd.c.

00193 { 00194 Aig_Obj_t * pObj, ** pLatches; 00195 int i, k, f, nNodesOld; 00196 // set copy pointer of each object to point to itself 00197 Aig_ManForEachObj( p, pObj, i ) 00198 pObj->pData = pObj; 00199 // iterate and add objects 00200 nNodesOld = Aig_ManObjNumMax(p); 00201 pLatches = ALLOC( Aig_Obj_t *, Aig_ManRegNum(p) ); 00202 for ( f = 0; f < nFrames; f++ ) 00203 { 00204 // clean latch inputs and outputs 00205 Aig_ManForEachLiSeq( p, pObj, i ) 00206 pObj->pData = NULL; 00207 Aig_ManForEachLoSeq( p, pObj, i ) 00208 pObj->pData = NULL; 00209 // save the latch input values 00210 k = 0; 00211 Aig_ManForEachLiSeq( p, pObj, i ) 00212 { 00213 if ( Aig_ObjFanin0(pObj)->pData ) 00214 pLatches[k++] = Aig_ObjChild0Copy(pObj); 00215 else 00216 pLatches[k++] = NULL; 00217 } 00218 // insert them as the latch output values 00219 k = 0; 00220 Aig_ManForEachLoSeq( p, pObj, i ) 00221 pObj->pData = pLatches[k++]; 00222 // create the next time frame of nodes 00223 Aig_ManForEachNode( p, pObj, i ) 00224 { 00225 if ( i > nNodesOld ) 00226 break; 00227 if ( Aig_ObjFanin0(pObj)->pData && Aig_ObjFanin1(pObj)->pData ) 00228 pObj->pData = Aig_And( p, Aig_ObjChild0Copy(pObj), Aig_ObjChild1Copy(pObj) ); 00229 else 00230 pObj->pData = NULL; 00231 } 00232 } 00233 free( pLatches ); 00234 }

| static void Fra_FramesConstrainNode | ( | Aig_Man_t * | pManFraig, | |

| Aig_Obj_t * | pObj, | |||

| int | iFrame | |||

| ) | [inline, static] |

Function*************************************************************

Synopsis [Performs speculative reduction for one node.]

Description []

SideEffects []

SeeAlso []

Definition at line 90 of file fraInd.c.

00091 { 00092 Aig_Obj_t * pObjNew, * pObjNew2, * pObjRepr, * pObjReprNew, * pMiter; 00093 // skip nodes without representative 00094 if ( (pObjRepr = Fra_ClassObjRepr(pObj)) == NULL ) 00095 return; 00096 assert( pObjRepr->Id < pObj->Id ); 00097 // get the new node 00098 pObjNew = Fra_ObjFraig( pObj, iFrame ); 00099 // get the new node of the representative 00100 pObjReprNew = Fra_ObjFraig( pObjRepr, iFrame ); 00101 // if this is the same node, no need to add constraints 00102 if ( Aig_Regular(pObjNew) == Aig_Regular(pObjReprNew) ) 00103 return; 00104 // these are different nodes - perform speculative reduction 00105 pObjNew2 = Aig_NotCond( pObjReprNew, pObj->fPhase ^ pObjRepr->fPhase ); 00106 // set the new node 00107 Fra_ObjSetFraig( pObj, iFrame, pObjNew2 ); 00108 // add the constraint 00109 pMiter = Aig_Exor( pManFraig, Aig_Regular(pObjNew), Aig_Regular(pObjReprNew) ); 00110 pMiter = Aig_NotCond( pMiter, Aig_Regular(pMiter)->fPhase ^ Aig_IsComplement(pMiter) ); 00111 pMiter = Aig_Not( pMiter ); 00112 Aig_ObjCreatePo( pManFraig, pMiter ); 00113 }

Function*************************************************************

Synopsis [Prepares the inductive case with speculative reduction.]

Description []

SideEffects []

SeeAlso []

Definition at line 126 of file fraInd.c.

00127 { 00128 Aig_Man_t * pManFraig; 00129 Aig_Obj_t * pObj, * pObjLi, * pObjLo, * pObjNew; 00130 int i, k, f; 00131 assert( p->pManFraig == NULL ); 00132 assert( Aig_ManRegNum(p->pManAig) > 0 ); 00133 assert( Aig_ManRegNum(p->pManAig) < Aig_ManPiNum(p->pManAig) ); 00134 00135 // start the fraig package 00136 pManFraig = Aig_ManStart( Aig_ManObjNumMax(p->pManAig) * p->nFramesAll ); 00137 pManFraig->pName = Aig_UtilStrsav( p->pManAig->pName ); 00138 pManFraig->nRegs = p->pManAig->nRegs; 00139 // create PI nodes for the frames 00140 for ( f = 0; f < p->nFramesAll; f++ ) 00141 Fra_ObjSetFraig( Aig_ManConst1(p->pManAig), f, Aig_ManConst1(pManFraig) ); 00142 for ( f = 0; f < p->nFramesAll; f++ ) 00143 Aig_ManForEachPiSeq( p->pManAig, pObj, i ) 00144 Fra_ObjSetFraig( pObj, f, Aig_ObjCreatePi(pManFraig) ); 00145 // create latches for the first frame 00146 Aig_ManForEachLoSeq( p->pManAig, pObj, i ) 00147 Fra_ObjSetFraig( pObj, 0, Aig_ObjCreatePi(pManFraig) ); 00148 00149 // add timeframes 00150 // pManFraig->fAddStrash = 1; 00151 for ( f = 0; f < p->nFramesAll - 1; f++ ) 00152 { 00153 // set the constraints on the latch outputs 00154 Aig_ManForEachLoSeq( p->pManAig, pObj, i ) 00155 Fra_FramesConstrainNode( pManFraig, pObj, f ); 00156 // add internal nodes of this frame 00157 Aig_ManForEachNode( p->pManAig, pObj, i ) 00158 { 00159 pObjNew = Aig_And( pManFraig, Fra_ObjChild0Fra(pObj,f), Fra_ObjChild1Fra(pObj,f) ); 00160 Fra_ObjSetFraig( pObj, f, pObjNew ); 00161 Fra_FramesConstrainNode( pManFraig, pObj, f ); 00162 } 00163 // transfer latch input to the latch outputs 00164 Aig_ManForEachLiLoSeq( p->pManAig, pObjLi, pObjLo, k ) 00165 Fra_ObjSetFraig( pObjLo, f+1, Fra_ObjChild0Fra(pObjLi,f) ); 00166 } 00167 // pManFraig->fAddStrash = 0; 00168 // mark the asserts 00169 pManFraig->nAsserts = Aig_ManPoNum(pManFraig); 00170 // add the POs for the latch outputs of the last frame 00171 Aig_ManForEachLoSeq( p->pManAig, pObj, i ) 00172 Aig_ObjCreatePo( pManFraig, Fra_ObjFraig(pObj,p->nFramesAll-1) ); 00173 00174 // remove dangling nodes 00175 Aig_ManCleanup( pManFraig ); 00176 // make sure the satisfying assignment is node assigned 00177 assert( pManFraig->pData == NULL ); 00178 return pManFraig; 00179 }

1.6.1

1.6.1