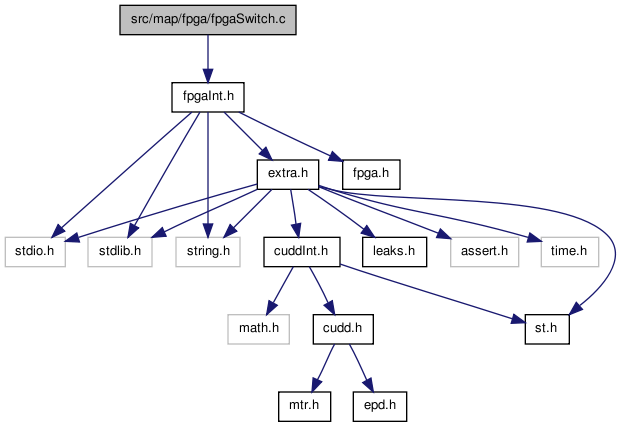

src/map/fpga/fpgaSwitch.c File Reference

#include "fpgaInt.h"

Go to the source code of this file.

Functions | |

| float | Fpga_CutGetSwitchDerefed (Fpga_Man_t *pMan, Fpga_Node_t *pNode, Fpga_Cut_t *pCut) |

| float | Fpga_CutRefSwitch (Fpga_Man_t *pMan, Fpga_Node_t *pNode, Fpga_Cut_t *pCut, int fFanouts) |

| float | Fpga_CutDerefSwitch (Fpga_Man_t *pMan, Fpga_Node_t *pNode, Fpga_Cut_t *pCut, int fFanouts) |

| float | Fpga_MappingGetSwitching (Fpga_Man_t *pMan, Fpga_NodeVec_t *vMapping) |

Function Documentation

| float Fpga_CutDerefSwitch | ( | Fpga_Man_t * | pMan, | |

| Fpga_Node_t * | pNode, | |||

| Fpga_Cut_t * | pCut, | |||

| int | fFanouts | |||

| ) |

function*************************************************************

synopsis [Dereferences the cut.]

description [This procedure is similar to the procedure NodeRecusiveDeref.]

sideeffects []

seealso []

Definition at line 92 of file fpgaSwitch.c.

00093 { 00094 Fpga_Node_t * pNodeChild; 00095 float aArea; 00096 int i; 00097 // start the area of this cut 00098 aArea = pNode->Switching; 00099 if ( pCut->nLeaves == 1 ) 00100 return aArea; 00101 // go through the children 00102 for ( i = 0; i < pCut->nLeaves; i++ ) 00103 { 00104 pNodeChild = pCut->ppLeaves[i]; 00105 assert( pNodeChild->nRefs > 0 ); 00106 if ( --pNodeChild->nRefs > 0 ) 00107 continue; 00108 aArea += Fpga_CutDerefSwitch( pMan, pNodeChild, pNodeChild->pCutBest, fFanouts ); 00109 } 00110 return aArea; 00111 }

| float Fpga_CutGetSwitchDerefed | ( | Fpga_Man_t * | pMan, | |

| Fpga_Node_t * | pNode, | |||

| Fpga_Cut_t * | pCut | |||

| ) |

CFile****************************************************************

FileName [fpgaSwitch.c]

PackageName [MVSIS 1.3: Multi-valued logic synthesis system.]

Synopsis [Generic technology mapping engine.]

Author [MVSIS Group]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - September 8, 2003.]

Revision [

- Id

- fpgaSwitch.h,v 1.0 2003/09/08 00:00:00 alanmi Exp

] DECLARATIONS /// FUNCTION DEFINITIONS ///function*************************************************************

synopsis [Computes the exact area associated with the cut.]

description []

sideeffects []

seealso []

Definition at line 40 of file fpgaSwitch.c.

00041 { 00042 float aResult, aResult2; 00043 aResult2 = Fpga_CutRefSwitch( pMan, pNode, pCut, 0 ); 00044 aResult = Fpga_CutDerefSwitch( pMan, pNode, pCut, 0 ); 00045 // assert( aResult == aResult2 ); 00046 return aResult; 00047 }

| float Fpga_CutRefSwitch | ( | Fpga_Man_t * | pMan, | |

| Fpga_Node_t * | pNode, | |||

| Fpga_Cut_t * | pCut, | |||

| int | fFanouts | |||

| ) |

function*************************************************************

synopsis [References the cut.]

description [This procedure is similar to the procedure NodeReclaim.]

sideeffects []

seealso []

Definition at line 60 of file fpgaSwitch.c.

00061 { 00062 Fpga_Node_t * pNodeChild; 00063 float aArea; 00064 int i; 00065 // start the area of this cut 00066 aArea = pNode->Switching; 00067 if ( pCut->nLeaves == 1 ) 00068 return aArea; 00069 // go through the children 00070 for ( i = 0; i < pCut->nLeaves; i++ ) 00071 { 00072 pNodeChild = pCut->ppLeaves[i]; 00073 assert( pNodeChild->nRefs >= 0 ); 00074 if ( pNodeChild->nRefs++ > 0 ) 00075 continue; 00076 aArea += Fpga_CutRefSwitch( pMan, pNodeChild, pNodeChild->pCutBest, fFanouts ); 00077 } 00078 return aArea; 00079 }

| float Fpga_MappingGetSwitching | ( | Fpga_Man_t * | pMan, | |

| Fpga_NodeVec_t * | vMapping | |||

| ) |

Function*************************************************************

Synopsis [Computes the array of mapping.]

Description []

SideEffects []

SeeAlso []

Definition at line 124 of file fpgaSwitch.c.

00125 { 00126 Fpga_Node_t * pNode; 00127 float Switch; 00128 int i; 00129 Switch = 0.0; 00130 for ( i = 0; i < vMapping->nSize; i++ ) 00131 { 00132 pNode = vMapping->pArray[i]; 00133 // at least one phase has the best cut assigned 00134 assert( !Fpga_NodeIsAnd(pNode) || pNode->pCutBest != NULL ); 00135 // at least one phase is used in the mapping 00136 assert( pNode->nRefs > 0 ); 00137 // compute the array due to the supergate 00138 Switch += pNode->Switching; 00139 } 00140 // add buffer for each CO driven by a CI 00141 for ( i = 0; i < pMan->nOutputs; i++ ) 00142 if ( Fpga_NodeIsVar(pMan->pOutputs[i]) && !Fpga_IsComplement(pMan->pOutputs[i]) ) 00143 Switch += pMan->pOutputs[i]->Switching; 00144 return Switch; 00145 }

1.6.1

1.6.1