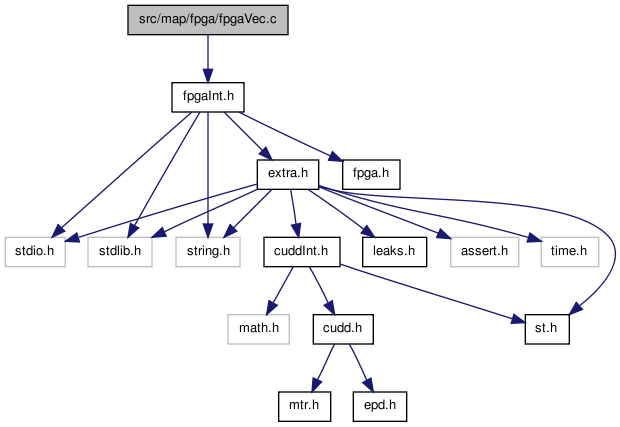

src/map/fpga/fpgaVec.c File Reference

#include "fpgaInt.h"

Go to the source code of this file.

Function Documentation

| Fpga_NodeVec_t* Fpga_NodeVecAlloc | ( | int | nCap | ) |

FUNCTION DEFINITIONS ///Function*************************************************************

Synopsis [Allocates a vector with the given capacity.]

Description []

SideEffects []

SeeAlso []

Definition at line 42 of file fpgaVec.c.

00043 { 00044 Fpga_NodeVec_t * p; 00045 p = ALLOC( Fpga_NodeVec_t, 1 ); 00046 if ( nCap > 0 && nCap < 16 ) 00047 nCap = 16; 00048 p->nSize = 0; 00049 p->nCap = nCap; 00050 p->pArray = p->nCap? ALLOC( Fpga_Node_t *, p->nCap ) : NULL; 00051 return p; 00052 }

| void Fpga_NodeVecClear | ( | Fpga_NodeVec_t * | p | ) |

| int Fpga_NodeVecCompareArrivals | ( | Fpga_Node_t ** | ppS1, | |

| Fpga_Node_t ** | ppS2 | |||

| ) |

Function*************************************************************

Synopsis [Compares the arrival times.]

Description []

SideEffects []

SeeAlso []

| int Fpga_NodeVecCompareLevels | ( | Fpga_Node_t ** | pp1, | |

| Fpga_Node_t ** | pp2 | |||

| ) | [static] |

CFile****************************************************************

FileName [fpgaVec.c]

PackageName [MVSIS 1.3: Multi-valued logic synthesis system.]

Synopsis [Technology mapping for variable-size-LUT FPGAs.]

Author [MVSIS Group]

Affiliation [UC Berkeley]

Date [Ver. 2.0. Started - August 18, 2004.]

Revision [

- Id

- fpgaVec.c,v 1.3 2005/01/23 06:59:42 alanmi Exp

] DECLARATIONS ///

Function*************************************************************

Synopsis [Comparison procedure for two nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 260 of file fpgaVec.c.

00261 { 00262 int Level1 = Fpga_Regular(*pp1)->Level; 00263 int Level2 = Fpga_Regular(*pp2)->Level; 00264 if ( Level1 < Level2 ) 00265 return -1; 00266 if ( Level1 > Level2 ) 00267 return 1; 00268 if ( Fpga_Regular(*pp1)->Num < Fpga_Regular(*pp2)->Num ) 00269 return -1; 00270 if ( Fpga_Regular(*pp1)->Num > Fpga_Regular(*pp2)->Num ) 00271 return 1; 00272 return 0; 00273 }

| void Fpga_NodeVecFree | ( | Fpga_NodeVec_t * | p | ) |

| void Fpga_NodeVecGrow | ( | Fpga_NodeVec_t * | p, | |

| int | nCapMin | |||

| ) |

Function*************************************************************

Synopsis [Resizes the vector to the given capacity.]

Description []

SideEffects []

SeeAlso []

| Fpga_Node_t* Fpga_NodeVecPop | ( | Fpga_NodeVec_t * | p | ) |

| void Fpga_NodeVecPush | ( | Fpga_NodeVec_t * | p, | |

| Fpga_Node_t * | Entry | |||

| ) |

Function*************************************************************

Synopsis []

Description []

SideEffects []

SeeAlso []

Definition at line 166 of file fpgaVec.c.

00167 { 00168 if ( p->nSize == p->nCap ) 00169 { 00170 if ( p->nCap < 16 ) 00171 Fpga_NodeVecGrow( p, 16 ); 00172 else 00173 Fpga_NodeVecGrow( p, 2 * p->nCap ); 00174 } 00175 p->pArray[p->nSize++] = Entry; 00176 }

| void Fpga_NodeVecPushOrder | ( | Fpga_NodeVec_t * | vNodes, | |

| Fpga_Node_t * | pNode, | |||

| int | fIncreasing | |||

| ) |

Function*************************************************************

Synopsis [Inserts a new node in the order by arrival times.]

Description []

SideEffects []

SeeAlso []

Definition at line 363 of file fpgaVec.c.

00364 { 00365 Fpga_Node_t * pNode1, * pNode2; 00366 int i; 00367 Fpga_NodeVecPush( vNodes, pNode ); 00368 // find the place of the node 00369 for ( i = vNodes->nSize-1; i > 0; i-- ) 00370 { 00371 pNode1 = vNodes->pArray[i ]; 00372 pNode2 = vNodes->pArray[i-1]; 00373 if ( fIncreasing && pNode1->pCutBest->tArrival >= pNode2->pCutBest->tArrival || 00374 !fIncreasing && pNode1->pCutBest->tArrival <= pNode2->pCutBest->tArrival ) 00375 break; 00376 vNodes->pArray[i ] = pNode2; 00377 vNodes->pArray[i-1] = pNode1; 00378 } 00379 }

| int Fpga_NodeVecPushUnique | ( | Fpga_NodeVec_t * | p, | |

| Fpga_Node_t * | Entry | |||

| ) |

Function*************************************************************

Synopsis [Add the element while ensuring uniqueness.]

Description [Returns 1 if the element was found, and 0 if it was new. ]

SideEffects []

SeeAlso []

Definition at line 189 of file fpgaVec.c.

00190 { 00191 int i; 00192 for ( i = 0; i < p->nSize; i++ ) 00193 if ( p->pArray[i] == Entry ) 00194 return 1; 00195 Fpga_NodeVecPush( p, Entry ); 00196 return 0; 00197 }

| Fpga_Node_t** Fpga_NodeVecReadArray | ( | Fpga_NodeVec_t * | p | ) |

| Fpga_Node_t* Fpga_NodeVecReadEntry | ( | Fpga_NodeVec_t * | p, | |

| int | i | |||

| ) |

| int Fpga_NodeVecReadSize | ( | Fpga_NodeVec_t * | p | ) |

| void Fpga_NodeVecReverse | ( | Fpga_NodeVec_t * | vNodes | ) |

Function*************************************************************

Synopsis [Inserts a new node in the order by arrival times.]

Description []

SideEffects []

SeeAlso []

| void Fpga_NodeVecShrink | ( | Fpga_NodeVec_t * | p, | |

| int | nSizeNew | |||

| ) |

| void Fpga_NodeVecSortByLevel | ( | Fpga_NodeVec_t * | p | ) |

Function*************************************************************

Synopsis [Sorting the entries by their integer value.]

Description []

SideEffects []

SeeAlso []

Definition at line 286 of file fpgaVec.c.

00287 { 00288 qsort( (void *)p->pArray, p->nSize, sizeof(Fpga_Node_t *), 00289 (int (*)(const void *, const void *)) Fpga_NodeVecCompareLevels ); 00290 }

| void Fpga_NodeVecUnion | ( | Fpga_NodeVec_t * | p, | |

| Fpga_NodeVec_t * | p1, | |||

| Fpga_NodeVec_t * | p2 | |||

| ) |

Function*************************************************************

Synopsis [Computes the union of nodes in two arrays.]

Description []

SideEffects []

SeeAlso []

Definition at line 342 of file fpgaVec.c.

00343 { 00344 int i; 00345 Fpga_NodeVecClear( p ); 00346 for ( i = 0; i < p1->nSize; i++ ) 00347 Fpga_NodeVecPush( p, p1->pArray[i] ); 00348 for ( i = 0; i < p2->nSize; i++ ) 00349 Fpga_NodeVecPush( p, p2->pArray[i] ); 00350 }

| void Fpga_NodeVecWriteEntry | ( | Fpga_NodeVec_t * | p, | |

| int | i, | |||

| Fpga_Node_t * | Entry | |||

| ) |

| void Fpga_SortNodesByArrivalTimes | ( | Fpga_NodeVec_t * | p | ) |

Function*************************************************************

Synopsis [Orders the nodes in the increasing order of the arrival times.]

Description []

SideEffects []

SeeAlso []

Definition at line 323 of file fpgaVec.c.

00324 { 00325 qsort( (void *)p->pArray, p->nSize, sizeof(Fpga_Node_t *), 00326 (int (*)(const void *, const void *)) Fpga_NodeVecCompareArrivals ); 00327 // assert( Fpga_CompareNodesByLevel( p->pArray, p->pArray + p->nSize - 1 ) <= 0 ); 00328 }

1.6.1

1.6.1