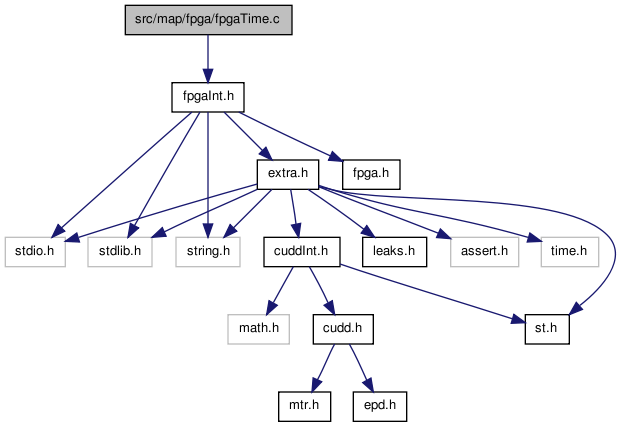

src/map/fpga/fpgaTime.c File Reference

#include "fpgaInt.h"

Go to the source code of this file.

Functions | |

| float | Fpga_TimeCutComputeArrival (Fpga_Man_t *pMan, Fpga_Cut_t *pCut) |

| float | Fpga_TimeCutComputeArrival_rec (Fpga_Man_t *pMan, Fpga_Cut_t *pCut) |

| float | Fpga_TimeComputeArrivalMax (Fpga_Man_t *p) |

| void | Fpga_TimeComputeRequiredGlobal (Fpga_Man_t *p, int fFirstTime) |

| void | Fpga_TimeComputeRequired (Fpga_Man_t *p, float fRequired) |

| void | Fpga_TimePropagateRequired (Fpga_Man_t *p, Fpga_NodeVec_t *vNodes) |

| void | Fpga_TimePropagateArrival (Fpga_Man_t *p) |

Function Documentation

| float Fpga_TimeComputeArrivalMax | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis [Computes the maximum arrival times.]

Description []

SideEffects []

SeeAlso []

Definition at line 86 of file fpgaTime.c.

00087 { 00088 float fRequired; 00089 int i; 00090 if ( p->fLatchPaths && p->nLatches == 0 ) 00091 { 00092 printf( "Delay optimization of latch path is not performed because there is no latches.\n" ); 00093 p->fLatchPaths = 0; 00094 } 00095 // get the critical PO arrival time 00096 fRequired = -FPGA_FLOAT_LARGE; 00097 if ( p->fLatchPaths ) 00098 { 00099 for ( i = p->nOutputs - p->nLatches; i < p->nOutputs; i++ ) 00100 { 00101 if ( Fpga_NodeIsConst(p->pOutputs[i]) ) 00102 continue; 00103 fRequired = FPGA_MAX( fRequired, Fpga_Regular(p->pOutputs[i])->pCutBest->tArrival ); 00104 // printf( " %5.1f", Fpga_Regular(p->pOutputs[i])->pCutBest->tArrival ); 00105 } 00106 // printf( "Required latches = %5.1f\n", fRequired ); 00107 } 00108 else 00109 { 00110 for ( i = 0; i < p->nOutputs; i++ ) 00111 { 00112 if ( Fpga_NodeIsConst(p->pOutputs[i]) ) 00113 continue; 00114 fRequired = FPGA_MAX( fRequired, Fpga_Regular(p->pOutputs[i])->pCutBest->tArrival ); 00115 // printf( " %5.1f", Fpga_Regular(p->pOutputs[i])->pCutBest->tArrival ); 00116 } 00117 // printf( "Required outputs = %5.1f\n", fRequired ); 00118 } 00119 return fRequired; 00120 }

| void Fpga_TimeComputeRequired | ( | Fpga_Man_t * | p, | |

| float | fRequired | |||

| ) |

Function*************************************************************

Synopsis [Computes the required times of all nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 165 of file fpgaTime.c.

00166 { 00167 int i; 00168 // clean the required times and the fanout counts for all nodes 00169 for ( i = 0; i < p->vAnds->nSize; i++ ) 00170 p->vAnds->pArray[i]->tRequired = FPGA_FLOAT_LARGE; 00171 // set the required times for the POs 00172 if ( p->fLatchPaths ) 00173 for ( i = p->nOutputs - p->nLatches; i < p->nOutputs; i++ ) 00174 Fpga_Regular(p->pOutputs[i])->tRequired = fRequired; 00175 else 00176 for ( i = 0; i < p->nOutputs; i++ ) 00177 Fpga_Regular(p->pOutputs[i])->tRequired = fRequired; 00178 // collect nodes reachable from POs in the DFS order through the best cuts 00179 Fpga_TimePropagateRequired( p, p->vMapping ); 00180 /* 00181 { 00182 int Counter = 0; 00183 for ( i = 0; i < p->vAnds->nSize; i++ ) 00184 if ( p->vAnds->pArray[i]->tRequired > FPGA_FLOAT_LARGE - 100 ) 00185 Counter++; 00186 printf( "The number of nodes with large required times = %d.\n", Counter ); 00187 } 00188 */ 00189 }

| void Fpga_TimeComputeRequiredGlobal | ( | Fpga_Man_t * | p, | |

| int | fFirstTime | |||

| ) |

Function*************************************************************

Synopsis [Computes the required times of all nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 133 of file fpgaTime.c.

00134 { 00135 p->fRequiredGlo = Fpga_TimeComputeArrivalMax( p ); 00136 // update the required times according to the target 00137 if ( p->DelayTarget != -1 ) 00138 { 00139 if ( p->fRequiredGlo > p->DelayTarget + p->fEpsilon ) 00140 { 00141 if ( fFirstTime ) 00142 printf( "Cannot meet the target required times (%4.2f). Mapping continues anyway.\n", p->DelayTarget ); 00143 } 00144 else if ( p->fRequiredGlo < p->DelayTarget - p->fEpsilon ) 00145 { 00146 if ( fFirstTime ) 00147 printf( "Relaxing the required times from (%4.2f) to the target (%4.2f).\n", p->fRequiredGlo, p->DelayTarget ); 00148 p->fRequiredGlo = p->DelayTarget; 00149 } 00150 } 00151 Fpga_TimeComputeRequired( p, p->fRequiredGlo ); 00152 }

| float Fpga_TimeCutComputeArrival | ( | Fpga_Man_t * | pMan, | |

| Fpga_Cut_t * | pCut | |||

| ) |

CFile****************************************************************

FileName [fpgaTime.c]

PackageName [MVSIS 1.3: Multi-valued logic synthesis system.]

Synopsis [Technology mapping for variable-size-LUT FPGAs.]

Author [MVSIS Group]

Affiliation [UC Berkeley]

Date [Ver. 2.0. Started - August 18, 2004.]

Revision [

- Id

- fpgaTime.c,v 1.1 2005/01/23 06:59:42 alanmi Exp

] DECLARATIONS /// FUNCTION DEFINITIONS ///Function*************************************************************

Synopsis [Computes the arrival times of the cut.]

Description [Computes the maximum arrival time of the cut leaves and adds the delay of the LUT.]

SideEffects []

SeeAlso []

Definition at line 41 of file fpgaTime.c.

00042 { 00043 int i; 00044 float tArrival; 00045 tArrival = -FPGA_FLOAT_LARGE; 00046 for ( i = 0; i < pCut->nLeaves; i++ ) 00047 if ( tArrival < pCut->ppLeaves[i]->pCutBest->tArrival ) 00048 tArrival = pCut->ppLeaves[i]->pCutBest->tArrival; 00049 tArrival += pMan->pLutLib->pLutDelays[pCut->nLeaves][0]; 00050 return tArrival; 00051 }

| float Fpga_TimeCutComputeArrival_rec | ( | Fpga_Man_t * | pMan, | |

| Fpga_Cut_t * | pCut | |||

| ) |

Function*************************************************************

Synopsis [Computes the arrival times of the cut recursively.]

Description [When computing the arrival time for the previously unused cuts, their arrival time may be incorrect because their fanins have incorrect arrival time. This procedure is called to fix this problem.]

SideEffects []

SeeAlso []

Definition at line 66 of file fpgaTime.c.

00067 { 00068 int i; 00069 for ( i = 0; i < pCut->nLeaves; i++ ) 00070 if ( pCut->ppLeaves[i]->nRefs == 0 ) 00071 Fpga_TimeCutComputeArrival_rec( pMan, pCut->ppLeaves[i]->pCutBest ); 00072 return Fpga_TimeCutComputeArrival( pMan, pCut ); 00073 }

| void Fpga_TimePropagateArrival | ( | Fpga_Man_t * | p | ) |

Function*************************************************************

Synopsis [Computes the required times of all nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 242 of file fpgaTime.c.

00243 { 00244 Fpga_Node_t * pNode; 00245 Fpga_Cut_t * pCut; 00246 int i; 00247 00248 // clean the required times and the fanout counts for all nodes 00249 for ( i = 0; i < p->vAnds->nSize; i++ ) 00250 { 00251 pNode = p->vAnds->pArray[i]; 00252 for ( pCut = pNode->pCuts->pNext; pCut; pCut = pCut->pNext ) 00253 pCut->tArrival = Fpga_TimeCutComputeArrival( p, pCut ); 00254 } 00255 }

| void Fpga_TimePropagateRequired | ( | Fpga_Man_t * | p, | |

| Fpga_NodeVec_t * | vNodes | |||

| ) |

Function*************************************************************

Synopsis [Computes the required times of the given nodes.]

Description []

SideEffects []

SeeAlso []

Definition at line 202 of file fpgaTime.c.

00203 { 00204 Fpga_Node_t * pNode, * pChild; 00205 float fRequired; 00206 int i, k; 00207 00208 // sorts the nodes in the decreasing order of levels 00209 // Fpga_MappingSortByLevel( p, vNodes, 0 ); 00210 // the nodes area already sorted in Fpga_MappingSetRefsAndArea() 00211 00212 // go through the nodes in the reverse topological order 00213 for ( k = 0; k < vNodes->nSize; k++ ) 00214 { 00215 pNode = vNodes->pArray[k]; 00216 if ( !Fpga_NodeIsAnd(pNode) ) 00217 continue; 00218 // get the required time for children 00219 fRequired = pNode->tRequired - p->pLutLib->pLutDelays[pNode->pCutBest->nLeaves][0]; 00220 // update the required time of the children 00221 for ( i = 0; i < pNode->pCutBest->nLeaves; i++ ) 00222 { 00223 pChild = pNode->pCutBest->ppLeaves[i]; 00224 pChild->tRequired = FPGA_MIN( pChild->tRequired, fRequired ); 00225 } 00226 } 00227 }

1.6.1

1.6.1