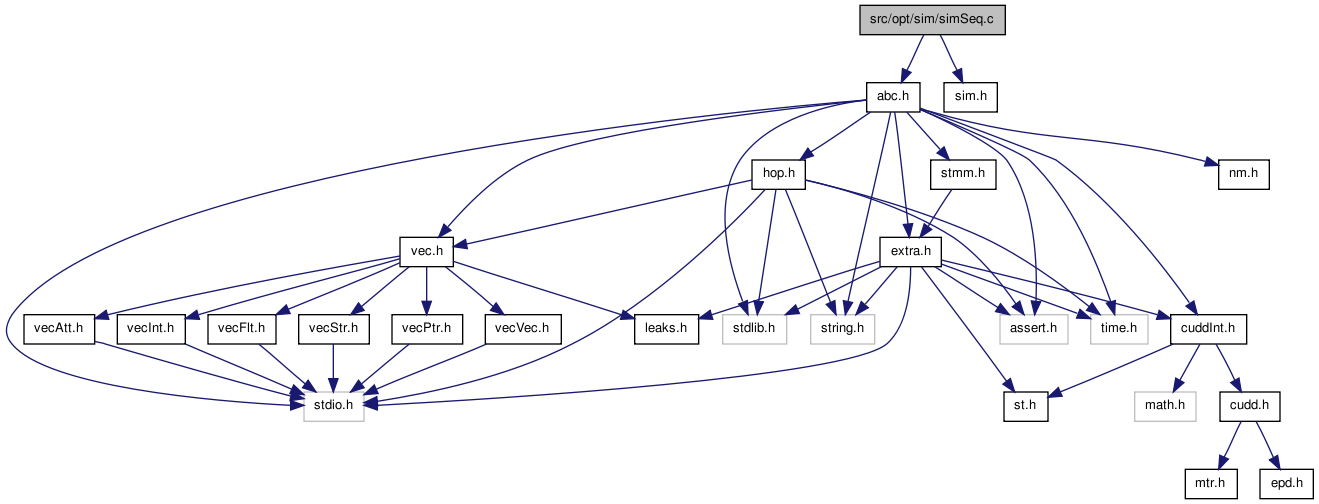

src/opt/sim/simSeq.c File Reference

#include "abc.h"#include "sim.h"

Go to the source code of this file.

Functions | |

| static void | Sim_SimulateSeqFrame (Vec_Ptr_t *vInfo, Abc_Ntk_t *pNtk, int iFrames, int nWords, int fTransfer) |

| Vec_Ptr_t * | Sim_SimulateSeqRandom (Abc_Ntk_t *pNtk, int nFrames, int nWords) |

| Vec_Ptr_t * | Sim_SimulateSeqModel (Abc_Ntk_t *pNtk, int nFrames, int *pModel) |

Function Documentation

| void Sim_SimulateSeqFrame | ( | Vec_Ptr_t * | vInfo, | |

| Abc_Ntk_t * | pNtk, | |||

| int | iFrames, | |||

| int | nWords, | |||

| int | fTransfer | |||

| ) | [static] |

CFile****************************************************************

FileName [simSeq.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Network and node package.]

Synopsis [Simulation for sequential circuits.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 20, 2005.]

Revision [

- Id

- simUtils.c,v 1.00 2005/06/20 00:00:00 alanmi Exp

] DECLARATIONS ///

Function*************************************************************

Synopsis [Simulates one frame of sequential circuit.]

Description [Assumes that the latches and POs are already initialized. In the end transfers the data to the latches of the next frame.]

SideEffects []

SeeAlso []

Definition at line 152 of file simSeq.c.

00153 { 00154 Abc_Obj_t * pNode; 00155 int i; 00156 Abc_NtkForEachNode( pNtk, pNode, i ) 00157 Sim_UtilSimulateNodeOne( pNode, vInfo, nWords, iFrames * nWords ); 00158 Abc_NtkForEachPo( pNtk, pNode, i ) 00159 Sim_UtilTransferNodeOne( pNode, vInfo, nWords, iFrames * nWords, 0 ); 00160 if ( !fTransfer ) 00161 return; 00162 Abc_NtkForEachLatch( pNtk, pNode, i ) 00163 Sim_UtilTransferNodeOne( pNode, vInfo, nWords, iFrames * nWords, 1 ); 00164 }

Function*************************************************************

Synopsis [Simulates sequential circuit.]

Description [Takes sequential circuit (pNtk). Simulates the given number (nFrames) of the circuit with the given model. The model is assumed to contain values of PIs for each frame. The latches are initialized to the initial state. One word of data is simulated.]

SideEffects []

SeeAlso []

Definition at line 89 of file simSeq.c.

00090 { 00091 Vec_Ptr_t * vInfo; 00092 Abc_Obj_t * pNode; 00093 unsigned * pUnsigned; 00094 int i, k; 00095 vInfo = Sim_UtilInfoAlloc( Abc_NtkObjNumMax(pNtk), nFrames, 0 ); 00096 // set the constant data 00097 pNode = Abc_AigConst1(pNtk); 00098 Sim_UtilSetConst( Sim_SimInfoGet(vInfo,pNode), nFrames, 1 ); 00099 // set the random PI data 00100 Abc_NtkForEachPi( pNtk, pNode, i ) 00101 { 00102 pUnsigned = Sim_SimInfoGet(vInfo,pNode); 00103 for ( k = 0; k < nFrames; k++ ) 00104 pUnsigned[k] = pModel[k * Abc_NtkPiNum(pNtk) + i] ? ~((unsigned)0) : 0; 00105 } 00106 // set the initial state data 00107 Abc_NtkForEachLatch( pNtk, pNode, i ) 00108 { 00109 pUnsigned = Sim_SimInfoGet(vInfo,pNode); 00110 if ( Abc_LatchIsInit0(pNode) ) 00111 pUnsigned[0] = 0; 00112 else if ( Abc_LatchIsInit1(pNode) ) 00113 pUnsigned[0] = ~((unsigned)0); 00114 else 00115 pUnsigned[0] = SIM_RANDOM_UNSIGNED; 00116 } 00117 // simulate the nodes for the given number of timeframes 00118 for ( i = 0; i < nFrames; i++ ) 00119 Sim_SimulateSeqFrame( vInfo, pNtk, i, 1, (int)(i < nFrames-1) ); 00120 /* 00121 // print the simulated values 00122 for ( i = 0; i < nFrames; i++ ) 00123 { 00124 printf( "Frame %d : ", i+1 ); 00125 Abc_NtkForEachPi( pNtk, pNode, k ) 00126 printf( "%d", Sim_SimInfoGet(vInfo,pNode)[i] > 0 ); 00127 printf( " " ); 00128 Abc_NtkForEachLatch( pNtk, pNode, k ) 00129 printf( "%d", Sim_SimInfoGet(vInfo,pNode)[i] > 0 ); 00130 printf( " " ); 00131 Abc_NtkForEachPo( pNtk, pNode, k ) 00132 printf( "%d", Sim_SimInfoGet(vInfo,pNode)[i] > 0 ); 00133 printf( "\n" ); 00134 } 00135 printf( "\n" ); 00136 */ 00137 return vInfo; 00138 }

FUNCTION DEFINITIONS ///Function*************************************************************

Synopsis [Simulates sequential circuit.]

Description [Takes sequential circuit (pNtk). Simulates the given number (nFrames) of the circuit with the given number of machine words (nWords) of random simulation data, starting from the initial state. If the initial state of some latches is a don't-care, uses random input for that latch.]

SideEffects []

SeeAlso []

Definition at line 48 of file simSeq.c.

00049 { 00050 Vec_Ptr_t * vInfo; 00051 Abc_Obj_t * pNode; 00052 int i; 00053 assert( Abc_NtkIsStrash(pNtk) ); 00054 vInfo = Sim_UtilInfoAlloc( Abc_NtkObjNumMax(pNtk), nWords * nFrames, 0 ); 00055 // set the constant data 00056 pNode = Abc_AigConst1(pNtk); 00057 Sim_UtilSetConst( Sim_SimInfoGet(vInfo,pNode), nWords * nFrames, 1 ); 00058 // set the random PI data 00059 Abc_NtkForEachPi( pNtk, pNode, i ) 00060 Sim_UtilSetRandom( Sim_SimInfoGet(vInfo,pNode), nWords * nFrames ); 00061 // set the initial state data 00062 Abc_NtkForEachLatch( pNtk, pNode, i ) 00063 if ( Abc_LatchIsInit0(pNode) ) 00064 Sim_UtilSetConst( Sim_SimInfoGet(vInfo,pNode), nWords, 0 ); 00065 else if ( Abc_LatchIsInit1(pNode) ) 00066 Sim_UtilSetConst( Sim_SimInfoGet(vInfo,pNode), nWords, 1 ); 00067 else 00068 Sim_UtilSetRandom( Sim_SimInfoGet(vInfo,pNode), nWords ); 00069 // simulate the nodes for the given number of timeframes 00070 for ( i = 0; i < nFrames; i++ ) 00071 Sim_SimulateSeqFrame( vInfo, pNtk, i, nWords, (int)(i < nFrames-1) ); 00072 return vInfo; 00073 }

1.6.1

1.6.1