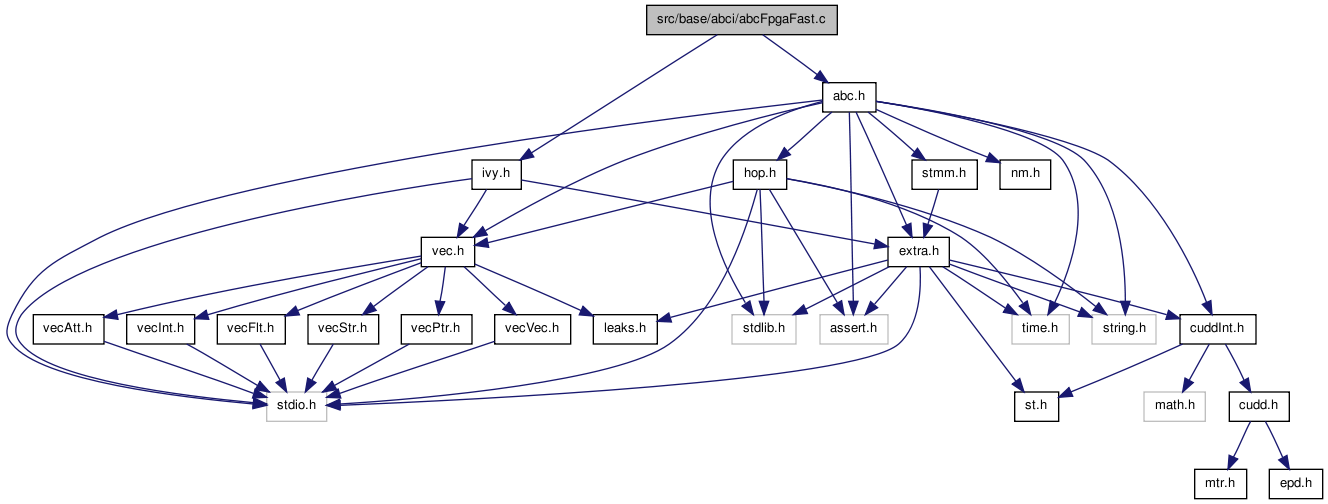

src/base/abci/abcFpgaFast.c File Reference

#include "abc.h"#include "ivy.h"

Go to the source code of this file.

Functions | |

| Ivy_Man_t * | Abc_NtkIvyBefore (Abc_Ntk_t *pNtk, int fSeq, int fUseDc) |

| static Abc_Ntk_t * | Ivy_ManFpgaToAbc (Abc_Ntk_t *pNtk, Ivy_Man_t *pMan) |

| static Abc_Obj_t * | Ivy_ManToAbcFast_rec (Abc_Ntk_t *pNtkNew, Ivy_Man_t *pMan, Ivy_Obj_t *pObjIvy, Vec_Int_t *vNodes) |

| static void | Abc_ObjSetIvy2Abc (Ivy_Man_t *p, int IvyId, Abc_Obj_t *pObjAbc) |

| static Abc_Obj_t * | Abc_ObjGetIvy2Abc (Ivy_Man_t *p, int IvyId) |

| Abc_Ntk_t * | Abc_NtkFpgaFast (Abc_Ntk_t *pNtk, int nLutSize, int fRecovery, int fVerbose) |

Function Documentation

FUNCTION DEFINITIONS ///Function*************************************************************

Synopsis [Performs fast FPGA mapping of the network.]

Description [Takes the AIG to be mapped, the LUT size, and verbosity flag. Produces the new network by fast FPGA mapping of the current network. If the current network in ABC in not an AIG, the user should run command "strash" to make sure that the current network into an AIG before calling this procedure.]

SideEffects []

SeeAlso []

Definition at line 55 of file abcFpgaFast.c.

00056 { 00057 Ivy_Man_t * pMan; 00058 Abc_Ntk_t * pNtkNew; 00059 // make sure the network is an AIG 00060 assert( Abc_NtkIsStrash(pNtk) ); 00061 // convert the network into the AIG 00062 pMan = Abc_NtkIvyBefore( pNtk, 0, 0 ); 00063 // perform fast FPGA mapping 00064 Ivy_FastMapPerform( pMan, nLutSize, fRecovery, fVerbose ); 00065 // convert back into the ABC network 00066 pNtkNew = Ivy_ManFpgaToAbc( pNtk, pMan ); 00067 Ivy_FastMapStop( pMan ); 00068 Ivy_ManStop( pMan ); 00069 // make sure that the final network passes the test 00070 if ( pNtkNew != NULL && !Abc_NtkCheck( pNtkNew ) ) 00071 { 00072 printf( "Abc_NtkFastMap: The network check has failed.\n" ); 00073 Abc_NtkDelete( pNtkNew ); 00074 return NULL; 00075 } 00076 return pNtkNew; 00077 }

CFile****************************************************************

FileName [abcFpgaFast.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Network and node package.]

Synopsis [Fast FPGA mapper.]

Author [Sungmin Cho]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 20, 2005.]

Revision [

- Id

- abcFpgaFast.c,v 1.00 2006/09/02 00:00:00 alanmi Exp

] DECLARATIONS ///

FUNCTION DEFINITIONS ///Function*************************************************************

Synopsis [Prepares the IVY package.]

Description []

SideEffects []

SeeAlso []

Definition at line 73 of file abcIvy.c.

00074 { 00075 Ivy_Man_t * pMan; 00076 int fCleanup = 1; 00077 //timeRetime = clock(); 00078 assert( !Abc_NtkIsNetlist(pNtk) ); 00079 if ( Abc_NtkIsBddLogic(pNtk) ) 00080 { 00081 if ( !Abc_NtkBddToSop(pNtk, 0) ) 00082 { 00083 printf( "Abc_NtkIvyBefore(): Converting to SOPs has failed.\n" ); 00084 return NULL; 00085 } 00086 } 00087 if ( fSeq && Abc_NtkCountSelfFeedLatches(pNtk) ) 00088 { 00089 printf( "Warning: The network has %d self-feeding latches.\n", Abc_NtkCountSelfFeedLatches(pNtk) ); 00090 // return NULL; 00091 } 00092 // print warning about choice nodes 00093 if ( Abc_NtkGetChoiceNum( pNtk ) ) 00094 printf( "Warning: The choice nodes in the initial AIG are removed by strashing.\n" ); 00095 // convert to the AIG manager 00096 pMan = Abc_NtkToIvy( pNtk ); 00097 if ( !Ivy_ManCheck( pMan ) ) 00098 { 00099 printf( "AIG check has failed.\n" ); 00100 Ivy_ManStop( pMan ); 00101 return NULL; 00102 } 00103 // Ivy_ManPrintStats( pMan ); 00104 if ( fSeq ) 00105 { 00106 int nLatches = Abc_NtkLatchNum(pNtk); 00107 Vec_Int_t * vInit = Abc_NtkCollectLatchValuesIvy( pNtk, fUseDc ); 00108 Ivy_ManMakeSeq( pMan, nLatches, vInit->pArray ); 00109 Vec_IntFree( vInit ); 00110 // Ivy_ManPrintStats( pMan ); 00111 } 00112 //timeRetime = clock() - timeRetime; 00113 return pMan; 00114 }

Definition at line 34 of file abcFpgaFast.c.

00034 { return Vec_PtrEntry( p->pCopy, IvyId ); }

Definition at line 33 of file abcFpgaFast.c.

00033 { assert(Vec_PtrEntry(p->pCopy, IvyId) == NULL); assert(!Abc_ObjIsComplement(pObjAbc)); Vec_PtrWriteEntry( p->pCopy, IvyId, pObjAbc ); }

Function*************************************************************

Synopsis [Constructs the ABC network after mapping.]

Description []

SideEffects []

SeeAlso []

Definition at line 90 of file abcFpgaFast.c.

00091 { 00092 Abc_Ntk_t * pNtkNew; 00093 Abc_Obj_t * pObjAbc, * pObj; 00094 Ivy_Obj_t * pObjIvy; 00095 Vec_Int_t * vNodes; 00096 int i; 00097 // start mapping from Ivy into Abc 00098 pMan->pCopy = Vec_PtrStart( Ivy_ManObjIdMax(pMan) + 1 ); 00099 // start the new ABC network 00100 pNtkNew = Abc_NtkStartFrom( pNtk, ABC_NTK_LOGIC, ABC_FUNC_AIG ); 00101 // transfer the pointers to the basic nodes 00102 Abc_ObjSetIvy2Abc( pMan, Ivy_ManConst1(pMan)->Id, Abc_NtkCreateNodeConst1(pNtkNew) ); 00103 Abc_NtkForEachCi( pNtkNew, pObjAbc, i ) 00104 Abc_ObjSetIvy2Abc( pMan, Ivy_ManPi(pMan, i)->Id, pObjAbc ); 00105 // recursively construct the network 00106 vNodes = Vec_IntAlloc( 100 ); 00107 Ivy_ManForEachPo( pMan, pObjIvy, i ) 00108 { 00109 // get the new ABC node corresponding to the old fanin of the PO in IVY 00110 pObjAbc = Ivy_ManToAbcFast_rec( pNtkNew, pMan, Ivy_ObjFanin0(pObjIvy), vNodes ); 00111 // consider the case of complemented fanin of the PO 00112 if ( Ivy_ObjFaninC0(pObjIvy) ) // complement 00113 { 00114 if ( Abc_ObjIsCi(pObjAbc) ) 00115 pObjAbc = Abc_NtkCreateNodeInv( pNtkNew, pObjAbc ); 00116 else 00117 { 00118 // clone the node 00119 pObj = Abc_NtkCloneObj( pObjAbc ); 00120 // set complemented functions 00121 pObj->pData = Hop_Not( pObjAbc->pData ); 00122 // return the new node 00123 pObjAbc = pObj; 00124 } 00125 } 00126 Abc_ObjAddFanin( Abc_NtkCo(pNtkNew, i), pObjAbc ); 00127 } 00128 Vec_IntFree( vNodes ); 00129 Vec_PtrFree( pMan->pCopy ); 00130 pMan->pCopy = NULL; 00131 // remove dangling nodes 00132 Abc_NtkCleanup( pNtkNew, 0 ); 00133 // fix CIs feeding directly into COs 00134 Abc_NtkLogicMakeSimpleCos( pNtkNew, 0 ); 00135 return pNtkNew; 00136 }

| Abc_Obj_t * Ivy_ManToAbcFast_rec | ( | Abc_Ntk_t * | pNtkNew, | |

| Ivy_Man_t * | pMan, | |||

| Ivy_Obj_t * | pObjIvy, | |||

| Vec_Int_t * | vNodes | |||

| ) | [static] |

Function*************************************************************

Synopsis [Recursively construct the new node.]

Description []

SideEffects []

SeeAlso []

Definition at line 149 of file abcFpgaFast.c.

00150 { 00151 Vec_Int_t Supp, * vSupp = &Supp; 00152 Abc_Obj_t * pObjAbc, * pFaninAbc; 00153 Ivy_Obj_t * pNodeIvy; 00154 int i, Entry; 00155 // skip the node if it is a constant or already processed 00156 pObjAbc = Abc_ObjGetIvy2Abc( pMan, pObjIvy->Id ); 00157 if ( pObjAbc ) 00158 return pObjAbc; 00159 assert( Ivy_ObjIsAnd(pObjIvy) || Ivy_ObjIsExor(pObjIvy) ); 00160 // get the support of K-LUT 00161 Ivy_FastMapReadSupp( pMan, pObjIvy, vSupp ); 00162 // create new ABC node and its fanins 00163 pObjAbc = Abc_NtkCreateNode( pNtkNew ); 00164 Vec_IntForEachEntry( vSupp, Entry, i ) 00165 { 00166 pFaninAbc = Ivy_ManToAbcFast_rec( pNtkNew, pMan, Ivy_ManObj(pMan, Entry), vNodes ); 00167 Abc_ObjAddFanin( pObjAbc, pFaninAbc ); 00168 } 00169 // collect the nodes used in the cut 00170 Ivy_ManCollectCut( pMan, pObjIvy, vSupp, vNodes ); 00171 // create the local function 00172 Ivy_ManForEachNodeVec( pMan, vNodes, pNodeIvy, i ) 00173 { 00174 if ( i < Vec_IntSize(vSupp) ) 00175 pNodeIvy->pEquiv = (Ivy_Obj_t *)Hop_IthVar( pNtkNew->pManFunc, i ); 00176 else 00177 pNodeIvy->pEquiv = (Ivy_Obj_t *)Hop_And( pNtkNew->pManFunc, (Hop_Obj_t *)Ivy_ObjChild0Equiv(pNodeIvy), (Hop_Obj_t *)Ivy_ObjChild1Equiv(pNodeIvy) ); 00178 } 00179 // set the local function 00180 pObjAbc->pData = (Abc_Obj_t *)pObjIvy->pEquiv; 00181 // set the node 00182 Abc_ObjSetIvy2Abc( pMan, pObjIvy->Id, pObjAbc ); 00183 return pObjAbc; 00184 }

1.6.1

1.6.1