simulate_blif.h File Reference

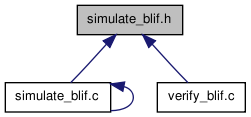

This graph shows which files directly or indirectly include this file:

Go to the source code of this file.

Defines | |

| #define | line_t struct line_t_t |

| #define | INPUT_VECTOR_FILE_NAME "input_vectors" |

| #define | OUTPUT_VECTOR_FILE_NAME "output_vectors" |

Functions | |

| void | simulate_blif (char *test_vector_file_name, netlist_t *netlist) |

| void | simulate_new_vectors (int num_test_vectors, netlist_t *netlist) |

Define Documentation

| #define INPUT_VECTOR_FILE_NAME "input_vectors" |

Definition at line 6 of file simulate_blif.h.

| #define line_t struct line_t_t |

Definition at line 4 of file simulate_blif.h.

| #define OUTPUT_VECTOR_FILE_NAME "output_vectors" |

Definition at line 7 of file simulate_blif.h.

Function Documentation

| void simulate_blif | ( | char * | test_vector_file_name, | |

| netlist_t * | netlist | |||

| ) |

Definition at line 95 of file simulate_blif.c.

00096 { 00097 FILE *in; 00098 char buffer[BUFFER_MAX_SIZE]; 00099 int cycle, i, lines_size; 00100 line_t **lines; 00101 00102 sim_type = TEST_EXISTING_VECTORS; 00103 sim_result = TRUE; //we're going to assume that everything goes OK for now 00104 modelsim_out = NULL; 00105 blocks = create_queue(); 00106 00107 //open our file 00108 in = fopen(test_vector_file_name, "r"); 00109 if (in == NULL) 00110 { 00111 error_message(SIMULATION_ERROR, -1, -1, "Could not open input vectors file %s\n", test_vector_file_name); 00112 } 00113 00114 //lines is an array of line_t structs that store a name and an array of pins 00115 lines = read_test_vector_headers(in, &lines_size, netlist->num_top_input_nodes + netlist->num_top_output_nodes); 00116 00117 //for each top input node, map it to a line 00118 for (i = 0; i < netlist->num_top_input_nodes; i++) 00119 assign_node_to_line(netlist->top_input_nodes[i], lines, lines_size, INPUT); 00120 //for each top output node, map it to a line 00121 for (i = 0; i < netlist->num_top_output_nodes; i++) 00122 assign_node_to_line(netlist->top_output_nodes[i], lines, lines_size, OUTPUT); 00123 00124 for (i = 0; i < lines_size; i++) 00125 { 00126 int j; 00127 for (j = 0; j < lines[i]->number_of_pins; j++) 00128 { 00129 if (NULL == lines[i]->pins[j]) 00130 { 00131 warning_message(SIMULATION_ERROR, -1, -1, "A line has a NULL pin. This may cause a segfault. This can be caused when registers are declared as reg [X:Y], where Y is greater than zero."); 00132 } 00133 } 00134 } 00135 00136 //get a line from our input vectors file and do stuff with it 00137 cycle = 0; 00138 while (fgets(buffer, BUFFER_MAX_SIZE, in) != NULL) 00139 { 00140 //continues while we can still read lines from the test vector file 00141 #ifdef DEBUG_SIMULATOR 00142 printf("Cycle: %d\nRead in from file: %s", cycle, buffer); 00143 #endif 00144 00145 //assigns the test values for the input lines ONLY 00146 assign_input_vector_to_lines(lines, buffer, cycle); 00147 00148 #ifdef DEBUG_SIMULATOR 00149 int m,n; 00150 for (m = 0; m < lines_size; m++) 00151 { 00152 printf("Line %s pin values %d through 0: ", lines[m]->name, lines[m]->number_of_pins-1); 00153 for (n = lines[m]->number_of_pins -1; n >= 0; n--) 00154 { 00155 printf("%d", lines[m]->pins[n]->sim_state->value); 00156 } 00157 printf("\n"); 00158 } 00159 #endif 00160 00161 simulate_cycle(netlist, cycle); 00162 //checks that the output test values match what we simulated 00163 verify_output_vectors(netlist, lines, lines_size, cycle); 00164 00165 cycle++; 00166 } 00167 00168 //if something went wrong, let the user know. They'll have to search the output 00169 //for specifics 00170 if (!sim_result) 00171 { 00172 printf("\nSimulation Error\n"); 00173 fprintf(stderr, "Simulation produced invalid data against the test vectors. Please see stderr output for details."); 00174 } 00175 00176 fclose(in); 00177 free_lines(lines, lines_size); 00178 free_blocks(); 00179 }

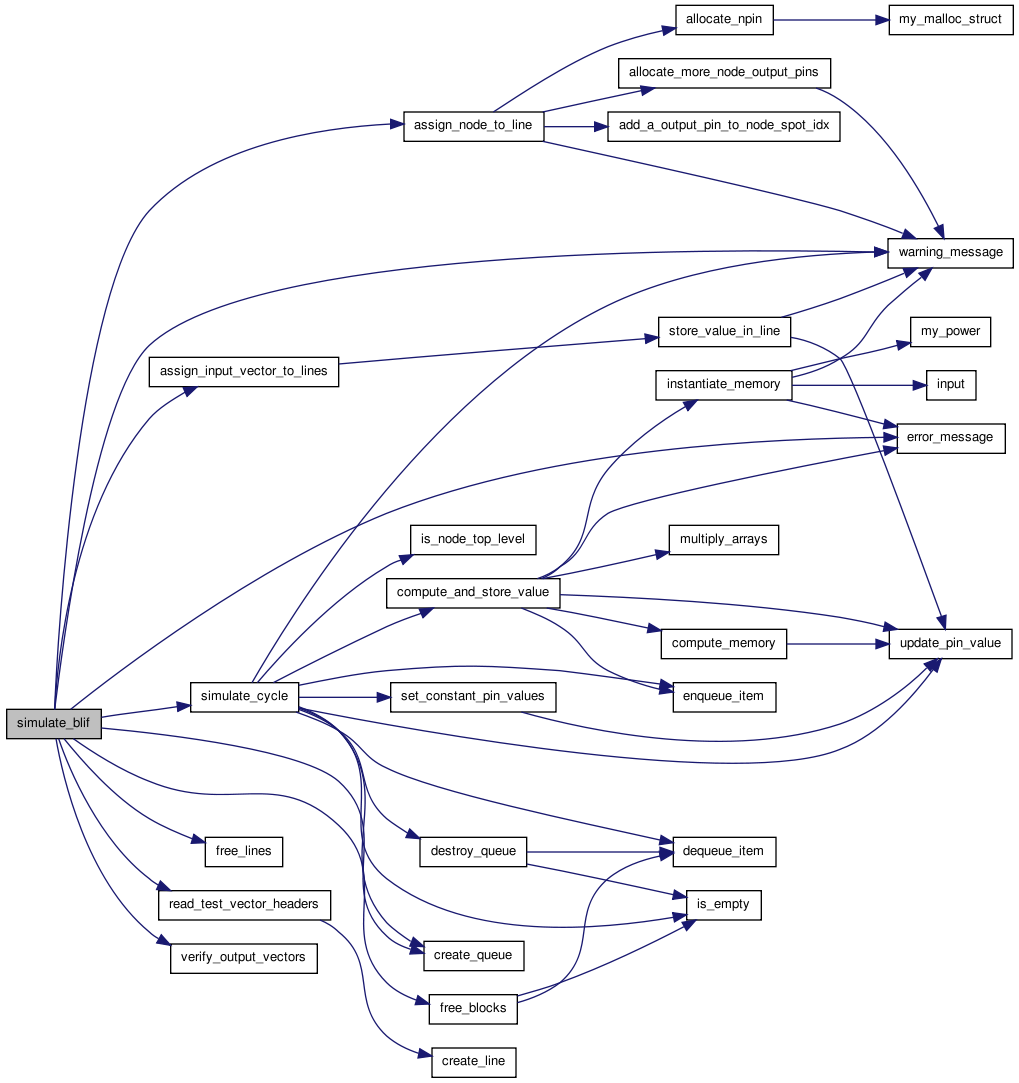

Here is the call graph for this function:

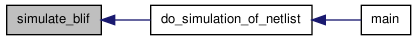

Here is the caller graph for this function:

| void simulate_new_vectors | ( | int | num_test_vectors, | |

| netlist_t * | netlist | |||

| ) |

Definition at line 187 of file simulate_blif.c.

00188 { 00189 FILE *iv, *outv; 00190 int cycle, lines_size; 00191 line_t **lines; 00192 int i; 00193 00194 sim_type = GENERATE_VECTORS; 00195 00196 blocks = create_queue(); 00197 00198 //open the input and output vector files 00199 iv = fopen(INPUT_VECTOR_FILE_NAME, "w"); 00200 if (NULL == iv) 00201 { 00202 error_message(SIMULATION_ERROR, -1, -1, "Could not write to input vectors file %s\n", INPUT_VECTOR_FILE_NAME); 00203 } 00204 outv = fopen(OUTPUT_VECTOR_FILE_NAME, "w"); 00205 if (NULL == outv) 00206 { 00207 error_message(SIMULATION_ERROR, -1, -1, "Could not write to output vectors file %s\n", OUTPUT_VECTOR_FILE_NAME); 00208 } 00209 modelsim_out = fopen("test.do", "w"); 00210 if (NULL == modelsim_out) 00211 { 00212 error_message(SIMULATION_ERROR, -1, -1, "Could not write to modelsim output file\n"); 00213 } 00214 00215 fprintf(modelsim_out, "force clock 1 0, 0 50 -repeat 100\n"); 00216 00217 //lines will be an array representing the I/O lines of our netlist 00218 lines = create_test_vector_lines(&lines_size, netlist); 00219 00220 for (i = 0; i < lines_size; i++) 00221 { 00222 int j; 00223 for (j = 0; j < lines[i]->number_of_pins; j++) 00224 { 00225 if (NULL == lines[i]->pins[j]) 00226 { 00227 warning_message(SIMULATION_ERROR, -1, -1, "A line has a NULL pin. This may cause a segfault.This can be caused when registers are declared as reg [X:Y], where Y is greater than zero."); 00228 } 00229 } 00230 } 00231 00232 //write the headers (names of I/O lines) to vector files 00233 //this is the same format that we're expecting to read in to verify 00234 //these later 00235 write_vector_headers(iv, outv, lines, lines_size); 00236 00237 //used to generate random test vectors 00238 srand((unsigned)(time(0))); 00239 00240 for (cycle = 0; cycle < num_test_vectors; cycle++) 00241 { 00242 #ifdef DEBUG_SIMULATOR 00243 int i; 00244 #endif 00245 00246 assign_random_vector_to_input_lines(lines, lines_size, cycle); 00247 00248 #ifdef DEBUG_SIMULATOR 00249 printf("Cycle: %d\n", cycle); 00250 for (i = 0; i < lines_size; i++) 00251 { 00252 int j; 00253 00254 if (lines[i]->type == OUTPUT) 00255 continue; 00256 00257 printf("Values for line %s from %d to 0: ", lines[i]->name, lines[i]->number_of_pins); 00258 00259 for (j = 0; j < lines[i]->number_of_pins; j++) 00260 { 00261 printf("%d", lines[i]->pins[j]->sim_state->value); 00262 } 00263 00264 printf("\n"); 00265 } 00266 #endif 00267 00268 write_vectors_to_file(lines, lines_size, iv, INPUT, cycle); 00269 simulate_cycle(netlist, cycle); 00270 write_vectors_to_file(lines, lines_size, outv, OUTPUT, cycle); 00271 } 00272 00273 fprintf(modelsim_out, "run %d\n", cycle*101); 00274 00275 fclose(iv); 00276 fclose(outv); 00277 fclose(modelsim_out); 00278 free_lines(lines, lines_size); 00279 free_blocks(); 00280 }

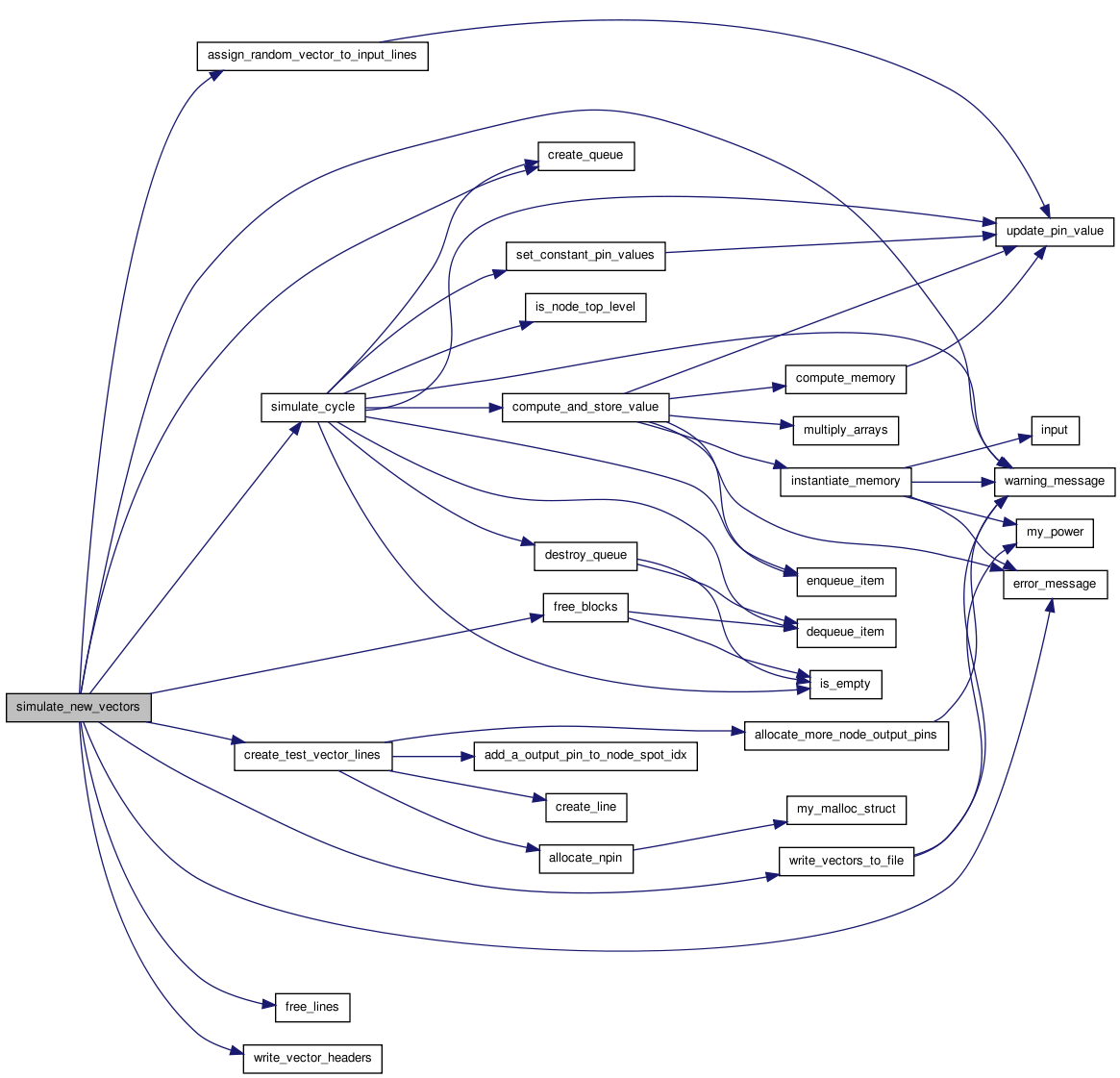

Here is the call graph for this function:

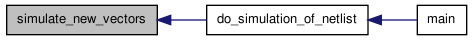

Here is the caller graph for this function:

1.6.3

1.6.3