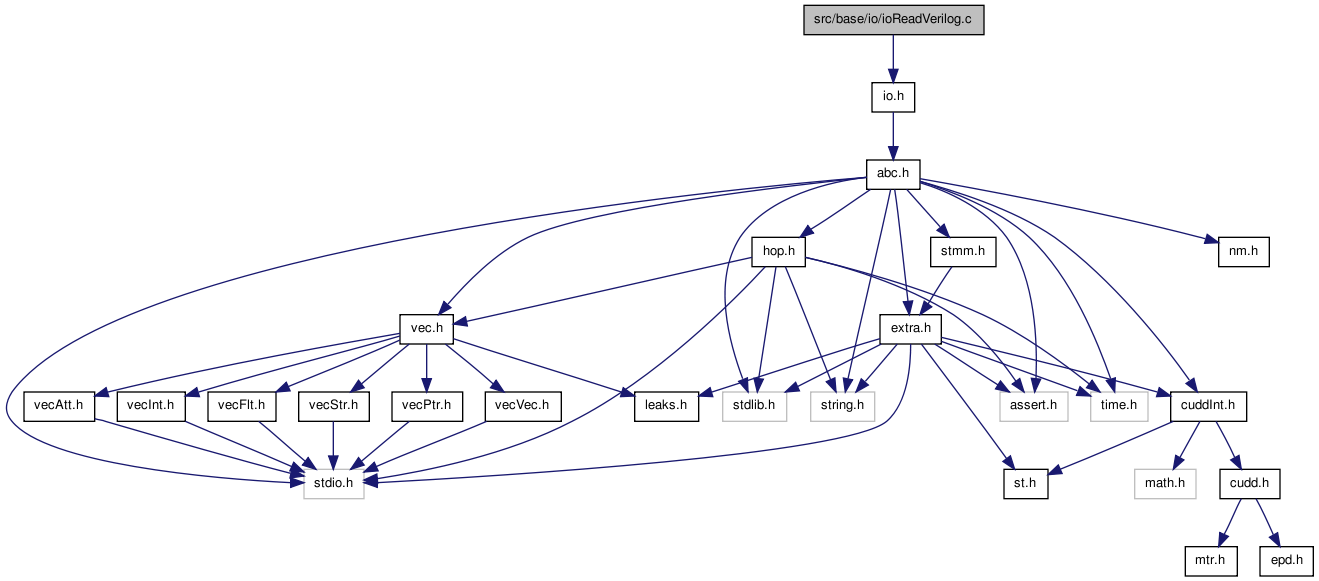

src/base/io/ioReadVerilog.c File Reference

#include "io.h"

Go to the source code of this file.

Functions | |

| Abc_Lib_t * | Ver_ParseFile (char *pFileName, Abc_Lib_t *pGateLib, int fCheck, int fUseMemMan) |

| Abc_Ntk_t * | Io_ReadVerilog (char *pFileName, int fCheck) |

Function Documentation

| Abc_Ntk_t* Io_ReadVerilog | ( | char * | pFileName, | |

| int | fCheck | |||

| ) |

FUNCTION DEFINITIONS ///Function*************************************************************

Synopsis [Reads hierarchical design from the Verilog file.]

Description []

SideEffects []

SeeAlso []

Definition at line 44 of file ioReadVerilog.c.

00045 { 00046 Abc_Ntk_t * pNtk; 00047 Abc_Lib_t * pDesign; 00048 int RetValue; 00049 00050 // parse the verilog file 00051 pDesign = Ver_ParseFile( pFileName, NULL, fCheck, 1 ); 00052 if ( pDesign == NULL ) 00053 return NULL; 00054 00055 // detect top-level model 00056 RetValue = Abc_LibFindTopLevelModels( pDesign ); 00057 pNtk = Vec_PtrEntry( pDesign->vTops, 0 ); 00058 if ( RetValue > 1 ) 00059 printf( "Warning: The design has %d root-level modules. The first one (%s) will be used.\n", 00060 Vec_PtrSize(pDesign->vTops), pNtk->pName ); 00061 00062 // extract the master network 00063 pNtk->pDesign = pDesign; 00064 pDesign->pManFunc = NULL; 00065 00066 // verify the design for cyclic dependence 00067 assert( Vec_PtrSize(pDesign->vModules) > 0 ); 00068 if ( Vec_PtrSize(pDesign->vModules) == 1 ) 00069 { 00070 // printf( "Warning: The design is not hierarchical.\n" ); 00071 Abc_LibFree( pDesign, pNtk ); 00072 pNtk->pDesign = NULL; 00073 pNtk->pSpec = Extra_UtilStrsav( pFileName ); 00074 } 00075 else 00076 { 00077 // check that there is no cyclic dependency 00078 Abc_NtkIsAcyclicHierarchy( pNtk ); 00079 } 00080 00081 //Io_WriteVerilog( pNtk, "_temp.v" ); 00082 return pNtk; 00083 }

CFile****************************************************************

FileName [ioReadVerilog.c]

SystemName [ABC: Logic synthesis and verification system.]

PackageName [Command processing package.]

Synopsis [Procedure to read network from file.]

Author [Alan Mishchenko]

Affiliation [UC Berkeley]

Date [Ver. 1.0. Started - June 20, 2005.]

Revision [

- Id

- ioReadVerilog.c,v 1.00 2005/06/20 00:00:00 alanmi Exp

] DECLARATIONS ///

Function*************************************************************

Synopsis [File parser.]

Description []

SideEffects []

SeeAlso []

Definition at line 155 of file verCore.c.

00156 { 00157 Ver_Man_t * p; 00158 Abc_Lib_t * pDesign; 00159 // start the parser 00160 p = Ver_ParseStart( pFileName, pGateLib ); 00161 p->fMapped = glo_fMapped; 00162 p->fCheck = fCheck; 00163 p->fUseMemMan = fUseMemMan; 00164 if ( glo_fMapped ) 00165 { 00166 Hop_ManStop(p->pDesign->pManFunc); 00167 p->pDesign->pManFunc = NULL; 00168 } 00169 // parse the file 00170 Ver_ParseInternal( p ); 00171 // save the result 00172 pDesign = p->pDesign; 00173 p->pDesign = NULL; 00174 // stop the parser 00175 Ver_ParseStop( p ); 00176 return pDesign; 00177 }

1.6.1

1.6.1