The installation files for Quartus II version 15.0.0.145 for Windows are available on ShareOut.

Due to issues with the installation of Quartus II in the lab, you will need to do the following each time the computer reboots

Your pre-lab reports are due immediately before the start of your lab. If your lab is on Monday it is due on Monday at 10:30. If your lab is on Thursday it is due on Thursday at 3:30. The lab reports are due on midnight on Thursday of the week after your lab.

Due to limitations in D2L I show the same pre-lab due date for both sets, but the above rules apply.

Additional information about due dates and penalties is in the course information handout.

A reminder: please do not send me e-mail from D2L. It generates an invalid return address that I cannot respond to from a regular e-mail program. Use a regular e-mail program (e.g. your mybcit e-mail account).

The Lab 1 Pre-Lab and Lab reports have been marked. Please check the feedback to avoid making the same errors in future labs.

Many people appear to not have read the course information handout. You are required to follow the instructions given there.

Information on how to access your marks (and lots of other essential information!) is there as well.

Many students seem to have missed the restrictions on using process statements given in bold on page 3 of lecture 2:

In this course you may only use processes to generate registers and may only use the single-if structure shown below.

The example process() is:

process(clk)

begin

if clk'event and clk = '1' then

q <= d ;

end if ;

end process ;

By "single-if structure" I mean that the only thing you may change is the signal names (clk, q and d). In some cases I may also allow more than one unconditional signal assignment within the if.

The purpose of this restriction is to help you understand how your VHDL will be converted to hardware. The simple process above maps into a register. The mapping of more complex process statements to sequential and combinational logic is more difficult for students to figure out.

Labs and assignments that include process statements that do not conform to the above restrictions will be considered incomplete or incorrect.

Many students seem to be confused about the meaning of "clock signal".

In synchronous logic design a clock is a signal that synchronizes assignments to register outputs.

In this course clock signals are those that appear in the sensitivity list of a process statement and whose 'event' attribute and level are tested in the process' if-statement to control the signal assignment. The name of the signal doesn't matter.

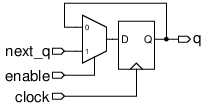

Specifically, enable signals are distinct from clocks. Enables control combinational logic outside the process. For example, in the following code 'enable' is an enable signal while 'clk' is a clock:

d <= next_q when enable = '1' else q ;

process(clk)

begin

if clk'event and clk = '1' then

q <= d ;

end if ;

end process ;

The logic generated is:

This is the single most important diagram and concept in the course. So be certain that you understand how this circuit works and how it is described in VHDL. It is a model for everything you will design in this course.

The midterm exam will be on Tuesday May 3 from 11:30 AM to 12:20 PM in SW1-2009. Note the room change!

You are responsble for the topics in the learning outcomes section of each of the lecture notes we cover.

There will be questions requiring you to (1) design a state machine and write the VHDL that would implement it and (2) convert between block diagrams (schematics) and VHDL (in both directions).

The final exam is scheduled for Tuesday, May 24 from 3:30 PM to 5:30 PM in NE1-239 (recent room change -- twice!).

It will be open-book and will cover all of the material listed in the learning outcomes section of each set of lecture notes.

You can expect questions on state machine design and converting from/to schematics to/from VHDL.

Has been changed to Saturday at midnight.

The solutions will be posted on Sunday morning and no submissions will be accepted after the solutions are posted.

I've collected exam and midterm questions from similar courses I've taught in the past into a single PDF file. Some have solutions. Some only ask for a state-machine design (but you can write the VHDL for the state machine as an exercise). The exams are in approximate chronological order with the more recent ones at the end.

These are take from my course archive site.

There have been a few changes over the past 20 years:

We will not have a new lab next week so that you can study for the mid-term. However, those who did not complete Lab 3 may demonstrate it during their scheduled lab section next week. You may be asked to modify the design in some way to demonstrate your understanding of your solution.

Update (April 29): After demonstrating Lab 3 you may work on and demonstrate Lab 4.

The report submission deadlines for Lab 3 and 4 have been changed to May 12 (midnight).

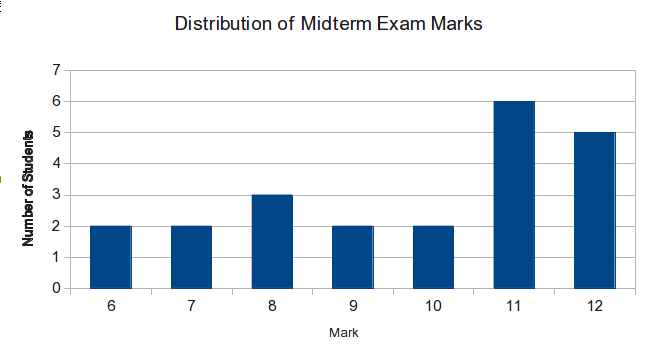

The midterm exam has been marked and the marks are available. The minimum, mean, median and maximum marks were 6, 9.8, 10.5 and 12 respectively. The distribution of marks was as follows:

The marks for Question 2 were significantly worse than those for Question 1. If you had problems with Question 2 then you may not understand how VHDL gets converted to digital logic and you may want to review some of the earlier lecture notes before the final exam.

Please ignore the announcement posted here briefly about re-scheduling the final exam. It was meant for a different course.

Everything except the final exam has been marked. Please check your marks. You can retrieve the password required to view your marks by clicking on the envelope icon on the top of page. Do not use the D2L e-mail system for anything else. The marking scheme explains how things were marked. The lowest lab mark and any labs or assignments for which a medical certificate was provided should have been omitted from the calculations. Please check the marking and the calculations and let me know if you have any questions.

Update (May 22): Jas found an error in my calculation of the lab marks: the lowest mark wasn't actually being omitted. I've fixed this and updated the marks.

Congratulations, everyone who wrote the final exam passed.

The final exam has been marked and the unofficial final marks computed. Please check your marks and let me know as soon as possible if you have any questions.

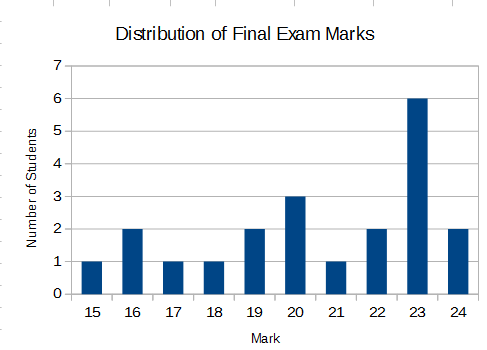

The final exam minimum/mean/median/maximum marks were 13.5, 20 21 and 24 out of 24.

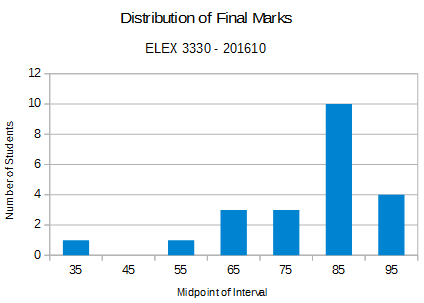

The final mark min/mean/median/max were: 38, 80, 85 and 100 percent.

The distribution of final exam marks is shown below:

The distribution of the final marks is:

If you would like to see your final exam I can scan it and e-mail it to you.