Teaching

Teaching and Learning Enhancement Fund project (TLEF)

We proposed to redesign Digital Systems Design course with ~450 student/year, to follow test-driven design methodologies currently used in the industry. For the 2019/2020 year, we have received $50,000 funding to develop the infrastructure. details ...

Teaching Assistantship

- [2017-2019] CPEN 311 - Digital Systems Design (4x TA)

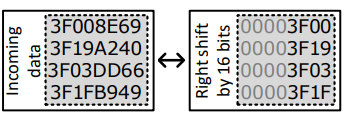

Students learn Advanced combinational and sequential electronic system design, hardware specification, modeling, and simulation using SystemVerilog, Design with programmable logic including FPGA's, pipelining, applications include complex state machines, microcontrollers, arithmetic circuits, and interface units. Students implement their work using Quartus software on DE1-SoC FPGA Board.

- [2015-2016] CPEN 211 - Introduction to Microcomputers (2× TA)

Students learn basics of digital systems and microcomputers including combinational and sequential circuits, organization and operation of microcomputers, memory addressing modes, instruction sets and NIOS II, and machine and assembly language programming. Students implement their work using Quartus software on DE2 FPGA boards.

- [2018-2019] IDSD 101 - Introduction to Digital Systems Design (2x TA)

Students learn basics of combinational and sequential electronic systems, hardware specification, modeling, and simulation using SystemVerilog, Design with programmable logic including FPGA's. Students implement their work using Quartus software on DE0-Nano FPGA Board.

- [2019] ELEC 391 - Electrical Engineering Design Studio II

Students learn basics of project management, design principles and practices, and testing and evaluation to be able to complete a final project. They also learn technical aspects such as electronics, communications, control systems, and motors and machines.

- [2015-2020] CPEN/ELEC 491 - Capstone Design Projects (4x TA)

- [2014] Embedded Systems Design

- [2013] Advanced Computer Architecture

- [2010] Computer Architecture

Supervising teaching assistant of senior students with the focus on working with a client from industry to design a product of significance, and solve an open-ended problem in electrical or computer engineering. Students learn how to formulate and analyze a problem, explore and propose a solution, run a cost evaluation, implement and validate a working prototype of the proposed solution. Here you can see a list of projects that I have assisted:

Hardware

2) Data transmission for remote villages.

3) Trackable baton for conducting AR app.

4) Connected and automated storage solutions.

5) Renewable energy for off-grid locations.

ML/AI

1) Realtime image classification on drones.

2) Deep learning for cancer detection.

3) Real-time vehicle classification on edge.

4) Satellite anomaly detection via ML.

5) Anomaly detection in sensor netoworks.

6) Volleyball analytics.

Software

1) Health care monitoring on embedded systems.

2) Home video-somnography for infants.

3) Smart home control app for IoT.

4) Sound synthesis via ML algorithms.

6) Android media center.

- [2014] Embedded Systems Design