## Introduction to Digital Design with Verilog HDL

**Exercise 1**: What changes would result in a 3-input OR gate?

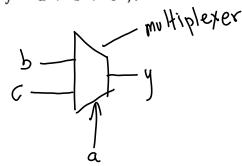

**Exercise 2**: What schematic would you expect if the statement was assign y = a ? b : c ;?

**Exercise 3**: What change might produce a 4-bit 4-to-1 multiplexer controlled by a 2-bit sel input?

endmodule

**Exercise 4**: If the signal i is declared as logic [2:0] i;, what is the 'width' of i? If i has the value 6 (decimal), what is the value of i[2]? Of i[0]?

**Exercise 5**: What are the values in decimal of the constants in the code above?

0:

$$d = 8 \text{ 'hc0}$$

;

1:  $d = 8 \text{ 'b1111_1001}$ ;  $\longrightarrow F9 = 249$

2:  $d = \text{ 'ha4}$ ;  $A = 169$

default:  $d = 176$ ;

**Exercise 6**: What is the output in binary when the input is a=2'  $b10 \rightarrow 2_{10}$

**Exercise 7**: Which ports are mapped by .\* in the instantiation of ex5?

Exercise 8: Write the module declaration for ex7. in Put [3:0] N ex7 ex7\_0 (

$$.n(count)$$

,  $.seg$ );

logic [3:0] count;

**Exercise 9**: Where in the code is the Device Under Test (DUT) instantiated?