## **Solutions to Assignment 3**

## **Question 1**

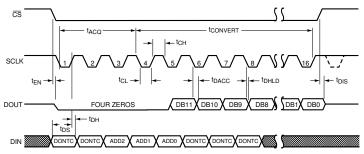

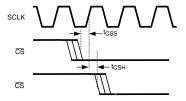

The pin functions described in Section 5, the timing specifications given in Section 6.6 and the timing diagrams given in Figures 2 and 3 from the TI ADC128S022 ADC data sheet are shown below.

- (a) *For the device*,  $\overline{CS}$  (CSn), DIN and SCLK are inputs. However, *for the FPGA*, DOUT is an input.

- (b) For the device, DOUT is an output. However, for the FPGA,  $\overline{CS}$  (CSn), DIN and SCLK are outputs.

- (c) The following table summarizes the 10 timing specifications ("req" means a timing requirement, "resp" means a guaranteed timing response):

| symbol              | from | to   | req./ | min./ | value            |

|---------------------|------|------|-------|-------|------------------|

| ,                   |      |      | resp. | max.  | (ns)             |

| $t_{\text{CSH}}$    | SCLK | CSn  | req   | min   | 10               |

| $t_{\mathrm{CSS}}$  | CSn  | SCLK | req   | min   | 10               |

| $t_{ m EN}$         | CSn  | DOUT | resp  | max   | 30               |

| $t_{\mathrm{DACC}}$ | SCLK | DOUT | resp  | max   | 27               |

| $t_{ m DHLD}$       | SCLK | DOUT | resp  | -     | -                |

| $t_{ m DS}$         | DIN  | SCLK | req   | min   | 10               |

| $t_{ m DH}$         | SCLK | DIN  | req   | min   | 10               |

| $t_{\mathrm{CH}}$   | SCLK | SCLK | req   | min   | $0.4t_{ m SCLK}$ |

| $t_{\rm CL}$        | SCLK | SCLK | req   | min   | $0.4t_{ m SCLK}$ |

| $t_{ m DIS}$        | CSn  | DOUT | resp  | max   | 20               |

(d) SDC timing contraints could be written as follows (tcl substitutes 490, the value of the expression in [expr...], for this argument):

```

t_{\text{CSH}}

```

$t_{\rm CSS}$

$t_{DACC}$

$t_{\rm DS}$

$t_{\rm DH}$ :

## Pin Functions

| PIN            |      |                 |                                                                                                                                                                                                                                                               |  |  |

|----------------|------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME           | NO.  | TYPE            | DESCRIPTION                                                                                                                                                                                                                                                   |  |  |

| CS             | 1    | Digital I/O     | Chip select. On the falling edge of $\overline{\text{CS}}$ , a conversion process begins. Conversions continue as long as $\overline{\text{CS}}$ is held low.                                                                                                 |  |  |

| V <sub>A</sub> | 2    | Power<br>Supply | Positive analog supply pin. This voltage is also used as the reference voltage. This pin should be connected to a quiet +2.7-V to +5.25-V source and bypassed to GND with 1-μF and 0.1-μF monolithic ceramic capacitors located within 1 cm of the power pin. |  |  |

| AGND           | 3    | Power<br>Supply | The ground return for the analog supply and signals.                                                                                                                                                                                                          |  |  |

| IN0 to IN7     | 4-11 | Analog I/O      | Analog inputs. These signals can range from 0 V to V <sub>REF</sub> .                                                                                                                                                                                         |  |  |

| DGND           | 12   | Power<br>Supply | The ground return for the digital supply and signals.                                                                                                                                                                                                         |  |  |

| V <sub>D</sub> | 13   | Power<br>Supply | Positive digital supply pin. This pin should be connected to a +2.7-V to $V_A$ supply, and bypassed to GND with a 0.1- $\mu$ F monolithic ceramic capacitor located within 1 cm of the power pin.                                                             |  |  |

| DIN            | 14   | Digital I/O     | Digital data input. The ADC128S022's Control Register is loaded through this pin on rising edges of the SCLK pin.                                                                                                                                             |  |  |

| DOUT           | 15   | Digital I/O     | Digital data output. The output samples are clocked out of this pin on the falling edges of the SCLK pin.                                                                                                                                                     |  |  |

| SCLK           | 16   | Digital I/O     | Digital clock input. The specified performance range of frequencies for this input is 0.8 MHz to 3.2 MHz. This clock directly controls the conversion and readout processes.                                                                                  |  |  |

## 6.6 Timing Specifications

The following specifications apply for  $V_A = V_D = 2.7$  V to 5.25 V, AGND = DGND = 0 V,  $f_{SCLK} = 0.8$  MHz to 3.2 MHz,  $f_{SAMPLE} = 50$  ksps to 200 ksps, and  $C_L = 50$  pF. Maximum and minimum limits apply for  $T_A = T_{MIN}$  to  $T_{MAX}$ : all other limits  $T_A = 2.5$  °C.

|                   | PARAMETER                                 | TEST CONDITIONS | MIN                     | NOM | MAX <sup>(1)</sup> | UNIT |

|-------------------|-------------------------------------------|-----------------|-------------------------|-----|--------------------|------|

| t <sub>CSH</sub>  | CS hold time after SCLK rising edge       |                 | 10                      | 0   |                    | ns   |

| t <sub>CSS</sub>  | CS set-up time prior to SCLK rising edge  |                 | 10                      | 4.5 |                    | ns   |

| t <sub>EN</sub>   | CS falling edge to DOUT enabled           |                 |                         | 5   | 30                 | ns   |

| tDACC             | DOUT access time after SCLK falling edge  |                 |                         | 17  | 27                 | ns   |

| t <sub>DHLD</sub> | DOUT hold time after SCLK falling edge    |                 |                         | 4   |                    | ns   |

| t <sub>DS</sub>   | DIN set-up time prior to SCLK rising edge |                 | 10                      | 3   |                    | ns   |

| t <sub>DH</sub>   | DIN hold time after SCLK rising edge      |                 | 10                      | 3   |                    | ns   |

| t <sub>CH</sub>   | SCLK high time                            |                 | 0.4 × t <sub>SCLK</sub> |     |                    | ns   |

| t <sub>CL</sub>   | SCLK low time                             |                 | 0.4 × t <sub>SCLK</sub> |     |                    | ns   |

| t <sub>DIS</sub>  | CS rising Edge to DOUT high-impedance     | DOUT falling    |                         | 2.4 | 20                 | ns   |

|                   | Co haing Lage to DOOT high-impedance      | DOUT rising     |                         | 0.9 | 20                 | ns   |

(1) Data sheet min/max specification limits are specified by design, test, or statistical analysis.

Figure 2. ADC128S022 Serial Timing Diagram

Figure 3. SCLK and  $\overline{\text{CS}}$  Timing Parameters