## Assignment 4

## **Due October 14, 1996**

The first question in this assignment asks you to select the appropriate PLD for various tasks. The other two questions ask you to verify the timing requirements of two combinations of microprocessors and memory/peripheral chips.

## **Question 1**

Select the type of PLD (PAL, CPLD or FPGA) that you would most likely use for each of the following purposes and briefly explain your choice.

- A device to implement the following on the same chip: a keypad scanning circuit (a combinational circuit requiring 12 i/o pins), a multiplexed 4-digit LED display driver (a sequential circuit using a 40 kHz clock, 4-bit counter, 16 bits of display memory and 11 i/o pins), and a 100 kHz 24-bit timer with a 16-bit CPU bus interface and internal configuration registers (a sequential circuit with two state machines for control and 56 bits of state for registers).

- 2. A wait-state generator requiring two enable signals and a 3-bit counter.

- A mailbox circuit that allows a 16-bit value to be exchanged between two independent CPUs. This requires one 16-bit register and a simple (4 i/o pin) combinational circuit to coordinate accesses to the register.

- 4. An address decoder with 8 address inputs, 2 chip select outputs and a requirement for a 10 ns maximum propagation delay

## **Question 2**

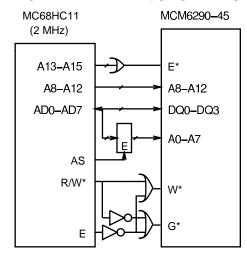

The following diagram shows the schematic of the interface between a Motorola MC68HC11 microprocessor and a Motorola MCM6290-45  $16kB \times 4$  static RAM.

The RAM has an enable (E\*) which is driven by an address decoder whose details are not relevant.

The 68HC11's address and data buses are multiplexed and a latch is used to demultiplex the address and data. The exact details are not relevant.

The RAM has write enable (W\*) and output enable (G\*) inputs. The two enables are driven by OR gates that ensure that W\* is only enabled during a write cycle and G\* is only enabled during a read cycle. The OR gates are also driven by the 68HC11's inverted E signal. This ensures these two enables are only active during the second half of a memory cycle – when E is high.

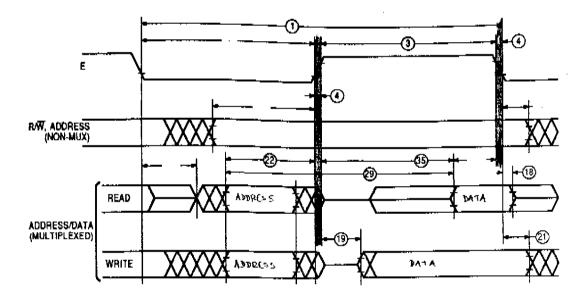

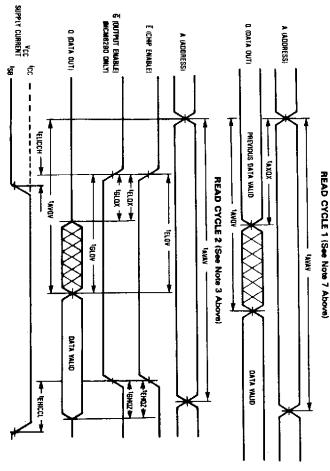

The timing diagram and timing specifications for the 68HC11 and are given in Figures **??** and **??**.

The timing diagram and timing specifications for the MCM6290-45 RAM are given below.

Assume that all the external logic devices (address decoder, latch, inverters and gates) have zero propagation delay. You should also assume that the rise and fall time (parameter 4) is zero.

The table below shows nine timing requirements that need to be met for the system to operate properly. Obtain expressions for these requirements in terms of the symbols for the timing specifications given in the

Figure 1: 68HC11 Timing Diagram.

| No. | Characteristic                     | Symbol        | Min | Max | Unit |

|-----|------------------------------------|---------------|-----|-----|------|

| 1   | Cycle Time                         | $t_{ m cyc}$  | 500 | 500 | ns   |

| 3   | Pulse Width, E high                | $PW_{EH}$     | 222 | —   | ns   |

| 18  | Read Data Hold Time                | $t_{\rm DHR}$ | 10  | 83  | ns   |

| 19  | Write Data Delay Time              | $t_{\rm DDW}$ | _   | 128 | ns   |

| 21  | Write Data Hold Time               | $t_{\rm DHW}$ | 33  | —   | ns   |

| 22  | Muxed Address Valid Time to E Rise | $t_{\rm AVM}$ | 84  | —   | ns   |

| 29  | MPU Address Access Time            | $t_{ACCA}$    | _   | 296 | ns   |

| 35  | MPU Access Time                    | $t_{ACCE}$    |     | 192 | ns   |

Figure 2: 68HC11 Timing Specifications.

data sheets. Obtain values for these expressions in nanoseconds. Find the amount by which the requirement is exceeded (in nanoseconds) and state whether the requirement is met or not (Y[es] or N[o]). Give your answer in the form of a table as shown below.

**Iportant:** Note that the first two requirements are maximum allowable access times and have been derived from the data setup time specification. All other requirements are minimums (setup times, pulse widths, hold times, etc).

Some specifications have been removed from the timing diagrams and tables.

## **Read Cycle**

| Requireme              | ent     | Guarante   | eed   | Margin | Met   |

|------------------------|---------|------------|-------|--------|-------|

| Symbol                 | Value   | Expression | Value |        | (Y/N) |

| MC68HC11 (2)           | MHz) Re | quirements |       |        |       |

| $t_{\text{ACCE}}$ (35) | 192     |            |       |        |       |

| $t_{\text{ACCA}}$ (29) | 296     |            |       |        |       |

| t <sub>DHR</sub> (18)  | 10      |            |       |        |       |

| 6290-45 Requir         | rements |            |       |        |       |

| $t_{\rm AVAV}$         | 45      |            |       |        |       |

## Write Cycle

| Require           | ement    | Guarant    | eed   | Margin | Met   |

|-------------------|----------|------------|-------|--------|-------|

| Symbol            | Value    | Expression | Value |        | (Y/N) |

| MCM629            | 0-45 Req | uirements  |       |        |       |

| t <sub>AVWL</sub> | 0        |            |       |        |       |

| $t_{\rm AVWH}$    | 35       |            |       |        |       |

| $t_{\rm WLWH}$    | 35       |            |       |        |       |

| $t_{\rm DVWH}$    | 20       |            |       |        |       |

| $t_{\rm WHDX}$    | 0        |            |       |        |       |

## **Question 3**

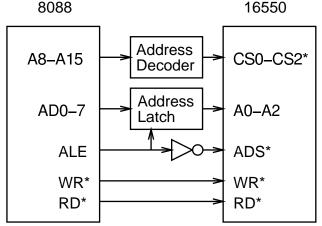

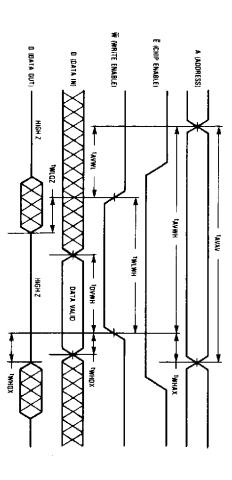

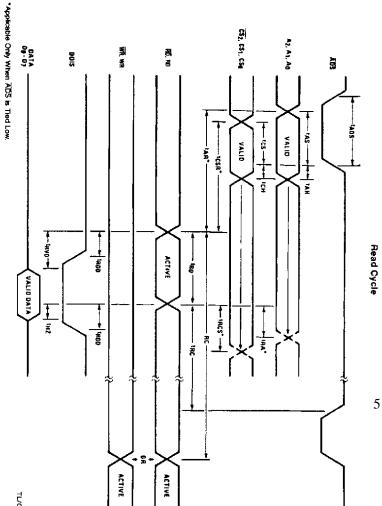

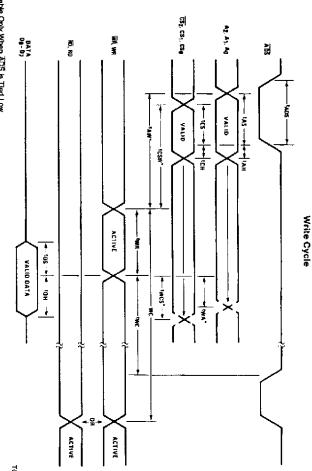

Attached are the timing diagrams and timing specifications for a a National 16550 serial interface chip and the timing specifications for an Oki 8088 CPU in minimum mode. The timing diagram for the 8088 was provided in the lecture on the 8088 processor bus. All times are in nanoseconds. The devices are connected as follows:

As in the previous question, you must determine if the above circuit will operate reliably by computing the margins for the timing requirements of both devices during both read and write cycles.

Prepare tables similar to those in the previous question that show the relevant timing requirements, the equations for each requirement in terms of the other device's guaranteed responses, the margin for each requirement and whether that requirement is met or not.

In this case *you* must decide which of the specifications are requirements and also which ones are relevant for read or write cycles.

You may assume that:

• the CPU is a 5 MHz device and the CPU clock frequency is exactly 5 MHz

- the propagation delay through the address decoder,  $T_{PD}$  is a maximum of 15 ns

- there is no propagation delay through the address latch and you need not verify that its setup and hold time requirements will be met

- wait states are not inserted (the READY lines are always asserted) and the CPU bus is never requested (HOLD is always false).

You will probably find it useful draw new timing diagrams that include only the relevant signals appearing at the two devices and at the address decoder.

| , | Vgs [] 12 | 2 | p.    | 2           | 2      | 2 | ь<br>Г | ×    | 2  | 2   | ž  | - <b>1</b> 3 |          |

|---|-----------|---|-------|-------------|--------|---|--------|------|----|-----|----|--------------|----------|

| I | 12        | = | 10    | 6           | •      | 7 | æ      | .,,, | *  | Э   | 2  | •            | MCMICSIO |

| l | 13        | ÷ | 15 00 | <u>d</u> 91 | d<br>L | ē |        | 8    | 20 | 2   | 23 | ž            | 8        |

|   | -0        | 8 | R     | 8           | ĝ      | 8 | E.     | 0 A  | ÷. | A12 | λı | ส์           |          |

| WRITE       |

|-------------|

| CYCLE 1     |

| ŝ           |

| Controlled, |

| See Notes   |

| 1 and 6)    |

| Parameter                                                     | Symbol             | nbol      |     | 2288-215<br>2290-215 | MCM8238-25 MCM6288-30 MCM8238-35 MCM6288-46<br>MCM8230-25 MCM8230-30 MCM8230-35 MCM8230-45 | 288-30 |                | 280-36 | MCM6288-46<br>MCM6280-46 |     | C <sub>n</sub> t | Unit Notes |

|---------------------------------------------------------------|--------------------|-----------|-----|----------------------|--------------------------------------------------------------------------------------------|--------|----------------|--------|--------------------------|-----|------------------|------------|

|                                                               | Standard Alternate | Alternate | Min | Max                  | Min                                                                                        | Max    | Min            | Max    | Min                      | Max |                  |            |

| Write Cycle Time                                              | 1 AVAV             | twc       | 25  | I                    | 8                                                                                          | +      | ដ              | I      | \$                       | 1   | Z                | N          |

| Address Setup Time                                            | <b>IAVWL</b>       | tas       | 0   |                      | •                                                                                          | I.     | ¢              | 4      | 0                        | ſ   | 2                |            |

| Address Valid to End of Write                                 | <sup>1</sup> AVWH  | taw       | 20  | I                    | 25                                                                                         | 1      | 8              | ı      | 8                        | ł   | \$               |            |

| Write Pulse Width                                             | WLWH               | twp       | 20  | ł                    | 25                                                                                         | Ι      | <del>3</del> 6 |        | 8                        | 1   | \$               |            |

| Data Valid to End of Write                                    | <sup>1</sup> DVWH  | tow       | 10  | )                    | 12                                                                                         | 1      | 15             | 1      | 8                        | 1   | 36               |            |

| Data Hold Time                                                | 1WHDX              | ЮН        | 0   | 1                    | 0                                                                                          | 1      | 0              | 1      | 0                        | ı   | 3                |            |

| Write Low to Output High-Z                                    | 1WLQZ              | 1WZ       | 0   | 10                   | 0                                                                                          | 12     | 0              | 15     | •                        | 5   | ä                | 3,4,5,6    |

| Write High to Output Active                                   | ₩нфх               | tow       | 5   | ı                    | 5                                                                                          | 1      | σ              | ı      | 5                        | -   | 15               | 3,4,5      |

| Write Recovery Time                                           | WHAX               | 1WE       | 0   | 1                    | 0                                                                                          | 1      | 0              | ł      | 0                        | I   | <b>D</b> 8       |            |

| NOTES: 1 A write popular during the gwaden of E low and W low | ~ ~ 투 느            |           |     |                      |                                                                                            |        |                |        |                          |     |                  |            |

NOTES:

A write occurs during the overlap of E low and W low.

A write occurs during is referenced from the last valid address to the first transitioning address.

Transition is measured ±500 mV from steady-state voltage with load in Figure 18.

Perameter is sampled and not 100% tested.

Perameter is sampled and not 100% tested.

A sampled and not 100% tested.

MCM6080, if G goes low coincident with or after W goes low, the output will remain in a high impedance state.

# AC OPERATING CONDITIONS AND CHARACTERISTICS (VCC = 5 V ± 10%, TA=0 to +70°C, Unless Otherwise Noted)

| Input Timing Measurement Reference Level 1.5 V Output Timing Measurement Reference Level | Output Timing Measurement Reference Level |

|------------------------------------------------------------------------------------------|-------------------------------------------|

| Input Pulse Levels                                                                       | Output Load Figure 1A United Otherwise N  |

| Input Riss/Falt Time                                                                     |                                           |

|                                                                                          |                                           |

READ CYCLE (See Note 1)

|                                                | SYI            | Symbol             | MCM6280-25<br>MCM6280-25 |     | MCM | MCM6285-30 MCM6285-35 |     |     | MCM230-45 |   | Unk No | Š.  |

|------------------------------------------------|----------------|--------------------|--------------------------|-----|-----|-----------------------|-----|-----|-----------|---|--------|-----|

|                                                | Standard       | Standard Alternate | Min                      | Max | N   | Max                   | Min | Max | Mij       | M |        |     |

| Read Cycle Time                                | LAVAV          | thc.               | 25                       | 1   | 8   | ı                     | *   | 1   | \$        | 1 | 2      | ١., |

| Address Access Time                            | TAVOV          | 1AA                | 1                        | 25  | Ι   | 30                    | ł   | 36  | ۱         | ħ | 3      |     |

| Enable Access Time                             | TELOV          | <sup>t</sup> ACS   | Ι                        | ĸ   | Т   | 8                     | ۱   | *   | 1         | 8 | 2      |     |

| Output Hold from Address Change                | ۲AXOX          | ЧŎ                 | 67                       | I   | 5   | ı                     | 5   | 1   | 57        | 1 | Z      |     |

| Output Enable Access Time MCM8290              |                | ίΩΕ                | 1                        | 12  | 1   | 16                    | I   | 5   | ı         | 8 | 2      |     |

| Output Enable Low to MCM6230<br>Output Active  | t₀_0x          | ŗ                  | 0                        | 1   | •   | 1                     | •   | 1   | •         | 1 | 3      | 2   |

| Output Enable High to MCM8290<br>Output High-Z | 1GHOZ          | ŧ                  | o                        | 70  | 0   | 12                    | •   | đ   | •         | ಹ | 2      | 2   |

| Enable Low to Output Active                    | teLOX          | ᆀ                  | 5                        | ł   | 5   | I                     | 5   | ı   | ch        | ı | *      |     |

| Enable High to Output High-Z                   | TEHOZ          | tHZ                | 0                        | 10  | 0   | 12                    | •   | ಹ   | 0         | 5 | ¥      |     |

| Power Up Time                                  | <b>TELICCH</b> | ۲pU                | •                        | 1   | •   | 1                     | •   | 1   | °         | ŀ | 3      |     |

| Power Down Time                                | <b>LEHICCI</b> | PD                 | ı                        | R   | I   | 8                     | 1   | 8   | 1         | 8 | 3      |     |

| NOTES: 1. We is high for read cycle.           |                |                    |                          | 1   |     |                       |     |     |           |   |        |     |

در دو م

All nead orcie timing is referenced from the last valid address to the first transitioning address. A datresses valid prior to or coincident with E going low. A tany given votage and temperature, tEHQZ max is less than tELOX min, and tGHQZ max is less than tGLQX min, both for given device and from device to device. Transition is measured ± 260 mV from steady-state votage with load of Figure 18. This parameter is sampled and not 100% teated. Device is continuously selected ( $E = V_{\rm IL}$  (MCM6230 only).

ģ

۴

2

| Symbol           | Parameter                                                        | Conditions               | Min      | Max  | Unita  |

|------------------|------------------------------------------------------------------|--------------------------|----------|------|--------|

| tADS             | Address Strobe Width                                             |                          | 60       |      | ns     |

| t <sub>AH</sub>  | Address Hold Time                                                |                          | 0        |      | ns     |

| t <sub>AR</sub>  | RD, RD Delay from Address                                        | (Note 1)                 | 30       |      | ns     |

| tas              | Address Setup Time                                               |                          | 60       |      | ns     |

| taw              | WR, WR Delay from Address                                        | (Note 1)                 | 30       |      | 13<br> |

| t <sub>CH</sub>  | Chip Select Hold Time                                            |                          | 0        |      |        |

| tcs              | Chip Select Setup Time                                           |                          | 60       |      | ns     |

| ICSR             | RD, RD Delay from Chip Select                                    | (Note 1)                 | 30       |      | ns     |

| tcsw             | WR, WR Delay from Select                                         | (Note 1)                 | 30       |      | ns     |

| t <sub>DH</sub>  | Data Hold Time                                                   |                          | 30       |      |        |

| tos              | Data Setup Time                                                  | ·····                    | 30       |      | ns     |

| t <sub>HZ</sub>  | RD, RD to Floating Data Delay                                    | @100 pF loading (Note 3) |          | 100  | ns     |

| t <sub>MR</sub>  | Master Reset Pulse Width                                         | <u></u>                  | 5000     | -100 | п\$    |

| t <sub>RA</sub>  | Address Hold Time from RD, RD                                    | (Note 1)                 | 20       |      | ns     |

| tRC              | Read Cycle Delay                                                 | , <u></u>                | 125      |      | ns     |

| tacs             | Chip Select Hold Time from RD, RD                                | (Note 1)                 | 20       |      | ns     |

| t <sub>RD</sub>  | RD, RD Strobe Width                                              |                          | 125      |      |        |

| t <sub>RDD</sub> | RD, RD to Driver Enable/Disable                                  | @100 pF loading (Note 3) |          | 60   | ns     |

| t <sub>RVD</sub> | Delay from RD, RD to Data                                        | @100 pF loading          | ┝╼═╌──╴┠ | 60   | ns     |

| 1 <sub>WA</sub>  | Address Hold Time from WR, WR                                    | (Note 1)                 | 20       |      |        |

| two              | Write Cycle Delay                                                |                          | 150      |      |        |

| twcs             | Chip Select Hold Time from WR, WR                                | (Note 1)                 | 20       |      |        |

| twe              | WR, WR Strobe Width                                              |                          | 100      |      | ns     |

| 1 <sub>XH</sub>  | Duration of Clock High Pulse                                     | External Clock (8, Max.) | 55       |      | ns     |

| <sup>t</sup> xl. | Duration of Clock Low Pulse                                      | External Clock (8, Max.) | 55       |      | ns     |

| RC               | Read Cycle = t <sub>AR</sub> + t <sub>RD</sub> + t <sub>RC</sub> |                          | 280      |      | ns     |

| wc               | Write Cycle = $t_{AW} + t_{WR} + t_{WC}$                         | <u> </u>                 | 280      |      | ns     |

### AC Electrical Characteristics T<sub>A</sub> = 0°C to +70°C, V<sub>DD</sub> = +5V ± 10% 3.0

## **Receiver/Transmitter with FIFOs†** PC16550D Universal Asynchronous

\*Applicable Only When ADS is Tied Low.

# **OKI** Semiconductor

# MSM80C88A-10RS/GS/JS

## **Timing Requirements** Minimum Mode System

| 5                 5 5                                                             | - 30 - 20 - 1 - 1 - 30 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 -         | Tchichi<br>Tclizcli<br>Tclizcli<br>Tclizx<br>Trivcl<br>Trivch<br>Trivch<br>Tinvch<br>Tillih | (From 1.0 V to 3.5 V)<br>CLK Fall Time<br>(From 3.5 V to 1.0 V)<br>Data in Setup Time<br>Data in Hold Time<br>RDY Setup Time into<br>MSM 82C84A-2 (See Notes 1, 2)<br>RDY Hold Time into MSM 82C84A-2<br>(See Notes 1, 2)<br>READY Setup Time Into<br>MSM80C88A-10<br>READY Hold Time Into MSM80C88A-10<br>READY Hold Time Into MSM80C88A-10<br>READY Hold Time Into MSM80C88A-10<br>READY Hold Time Into<br>MSM80C88A-10<br>READY HOLD X X X X X X X X X X X X X X X X X X X |

|-----------------------------------------------------------------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                   | 69                                                                   | Тана                                                                                        | CLK High Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1                                                                                 | 118                                                                  | Тасн                                                                                        | CLK Low Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| R                                                                                 | 200                                                                  | Tcucu                                                                                       | CLK Cycle Period                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5 MHz Spec.<br>V <sub>oc</sub> = 4.5 V to 5.5 V<br>Ta = -40 to +85°C<br>Min. Max. | 5 MHz Spec.<br>V <sub>CC</sub> = 4.5 V to<br>Ta = -40 to +<br>Min. N | Symbol                                                                                      | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

## **Timing Responses**

|                                                         |                   | 5 MHz Spec.                                           | ō          |

|---------------------------------------------------------|-------------------|-------------------------------------------------------|------------|

| Parameter                                               | Symbol            | V <sub>CC</sub> = 4.5 V to 6.5 V<br>Ta = -40 to +85°C | ¥85°C      |

|                                                         |                   | Mŋ.                                                   | Max.       |

| Address Valid Delay                                     | tcLAV             | 6                                                     | 110        |

| Address Hold Time                                       | xv131             | 10                                                    | 1          |

| Address Float Delay                                     |                   | tcrvx                                                 | 80         |

| ALE Width                                               | ใหม               | t <sub>CLCH</sub> -20                                 | 1          |

| ALE Active Delay                                        | СССИ              | 1                                                     | 08         |

| ALE Inactive Delay                                      | וכאור             | 1                                                     | <b>5</b> 8 |

| Address Hold Time to ALE inactive                       |                   | totch-10                                              | 1          |

|                                                         | lcrov             | 5                                                     | 110        |

| Data Hold Time                                          | CHDX              | 10                                                    | 1          |

| Data Hold Time after WR                                 | 1wHox             | toloh-30                                              | 1          |

| Control Active Delay 1                                  | loverv            | 10                                                    | 110        |

| Control Active Delay 2                                  | CHCIN             | 10                                                    | 110        |

| Control Inactive Delay                                  | ICVCTX            | 10                                                    | 110        |

| Address Float to RD Active                              | <sup>l</sup> azrl | 0                                                     |            |

| RD Active Delay                                         | t CL HL           | 10                                                    | 165        |

| RD Inactive Delay                                       | tcruh             | 10                                                    | 150        |

| RD Inactive to Next Address Active                      | <b>t</b> rhav     | t <sub>CLCH</sub> -45                                 |            |

| HLDA Valid Delay                                        | ICLHAV            | 10                                                    | 160        |

| RO Width                                                | <b>t</b> RLRH     | 2tcLcL-75                                             |            |

| WR Width                                                | <b>WLWH</b>       | 21acc-60                                              | 1          |

| Address Valid to ALE Low                                | TAVAL             | t <sub>сі сн</sub> -60                                | I          |

| Ouput Rise Time (From 0.8 V to 2.0 V)                   | тогон             | 1                                                     | 15         |

| Output Fall Time (From 2.0 V to 0.8 V)                  | TOHOL             | l                                                     | 15         |

| Notes: 1. Signals at MSM82C84A-2 shown for reference or | IA-2 sho          | wn for ref                                            | erence     |

6

÷ N :

Signals at MSM82C84A-2 shown for reference only. Setup requirement for asynchronous signal only to guarantee recognition at next C Applies only to  $T_2$  state. (8 ns into  $T_3$ )