## TOP A00123456 TOP A00123456 TOP A00123456 TOP A00123456 TOP

ELEX 2117 : Digital Techniques 2 2025 Winter Term

## MIDTERM EXAM 2 2:30 PM – Wednesday, March 5, 2025 SW01-1205

This exam has four (4) questions on two (2) pages. The marks for each question are as indicated. There are a total of nineteen (19) marks. Answer all questions. Write your answers and all rough work in this paper and nowhere else. Show your work. <u>Underline</u> or draw a <u>box</u> around your final answer. Numerical answers must include units. Books and notes are allowed. No electronic devices other than calculators are allowed. **Show your work**.

This exam paper is for:

Sample Exam 1 A00123456

Each exam is equally difficult.

Answer your own exam.

Do not start until you are told.

| Name:      |  |

|------------|--|

| BCIT ID:   |  |

| Signature: |  |

Question 1 3 marks

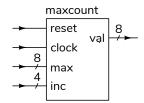

Write a Verilog module named maxcount with logic inputs named reset and clock, an 8-bit logic array input named max, a 4-bit logic array input named inc, and an 8-bit logic array output named val.

The output only changes on the rising edge of **clock**. If **reset** is asserted or **val** is equal to zero then **val** is set to **max**, otherwise **val** is decremented by **inc**. Follow the course coding guidelines but omit comments.

Question 2 6 marks

Write a Verilog testbench module named maxcount\_tb that:

- · declares any necessary variables

- instantiates the module maxcount described in the previous question

- sets max to a value equal to the last two digits of your BCIT ID and inc to 4

- creates a continuous 10 MHz clock, starting with a low (0) value

- · asserts reset for exactly one clock cycle

- terminates (rather than pauses) the simulation when val is equal to θ

You need not include comments or create a .vcd file.

Question 3 4 marks

Given the following module declarations:

```

module rom #(parameter b, w)

( input logic [w-1:0] a,

output logic [b-1:0] d );

input logic [b-1:0] din,

output logic [b-1:0] dout,

output logic [w-1:0] a );

```

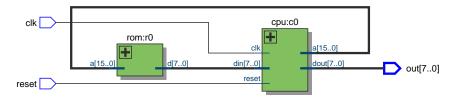

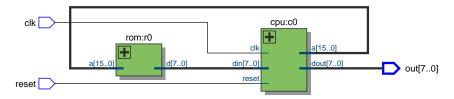

Write a Verilog module named **system** that implements the following diagram:

Declare any additional signals required to implement the diagram, using any valid signal names. Use a value of 8 for the parameter **b** and a value of 16 for the parameter **w** in each instantiation. Use explicit port and parameter names (e.g. .port(signal), .port, or #(.parameter(n))).

A00123456 2

Question 4 6 marks

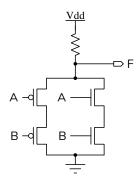

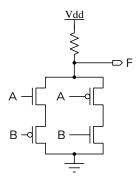

(a) The following table shows the voltages on inputs A and B for the circuit shown below. H corresponds to a voltage above the gate threshold voltage and L corresponds to 0 V.

Fill in the last column of the table with the voltage at point F of the circuit. Use H for a voltage of approximately  $V_{dd}$  and L for a voltage of approximately 0 V.

| А | В | F |

|---|---|---|

| L | L |   |

| L | Н |   |

| Н | L |   |

| Н | Н |   |

- (b) An IC has specifications of  $V_{\rm IL}=0.3\,{\rm V}$  and  $V_{\rm IH}=0.7\,{\rm V}$ . If you needed a noise margin of  $0.2\,{\rm V}$  for both high and low voltages, what are the required maximum  $V_{\rm OL}$  and minimum  $V_{\rm OH}$ ?

- (c) A circuit draws 200 mA when operating with a clock frequency of 50 MHz. You would like to operate this circuit for a year when powered by a CR2016 battery that has a capacity of 100 mAh. What clock frequency should you use? Hints: P = IV. V does not change. There are  $365 \times 24 = 8760$  hours in a year.

A00123456 3

## TOP A01234567 TOP A01234567 TOP A01234567 TOP A01234567 TOP

ELEX 2117 : Digital Techniques 2 2025 Winter Term

## MIDTERM EXAM 2 2:30 PM – Wednesday, March 5, 2025 SW01-1205

This exam has four (4) questions on two (2) pages. The marks for each question are as indicated. There are a total of nineteen (19) marks. Answer all questions. Write your answers and all rough work in this paper and nowhere else. Show your work. <u>Underline</u> or draw a <u>box</u> around your final answer. Numerical answers must include units. Books and notes are allowed. No electronic devices other than calculators are allowed. **Show your work**.

This exam paper is for:

Sample Exam 2 A01234567

Each exam is equally difficult.

Answer your own exam.

Do not start until you are told.

| Name:      |  |

|------------|--|

| BCIT ID:   |  |

| Signature: |  |

Question 1 3 marks

Write a Verilog module named maxcount with logic inputs named reset and clock, an 8-bit logic array input named max, a 4-bit logic array input named inc, and an 8-bit logic array output named val.

The output only changes on the rising edge of **clock**. If **reset** is asserted or **val** is equal to **max** then then **val** is set to zero, otherwise **val** is incremented by **inc**. Follow the course coding guidelines but omit comments.

Question 2 6 marks

Write a Verilog testbench module named maxcount\_tb that:

- · declares any necessary variables

- instantiates the module maxcount described in the previous question

- sets max to a value equal to the last two digits of your BCIT ID and inc to 2

- creates a continuous 50 MHz clock, starting with a low (0) value

- · asserts reset for exactly one clock cycle

- terminates (rather than pauses) the simulation when val is equal to max

You need not include comments or create a .vcd file.

Question 3 4 marks

Given the following module declarations:

```

module rom #(parameter b, w)

( input logic [w-1:0] a,

output logic [b-1:0] d );

input logic [b-1:0] din,

output logic [b-1:0] dout,

output logic [w-1:0] a );

```

Write a Verilog module named **system** that implements the following diagram:

Declare any additional signals required to implement the diagram, using any valid signal names. Use a value of 8 for the parameter **b** and a value of 16 for the parameter **w** in each instantiation. Use explicit port and parameter names (e.g. .port(signal), .port, or #(.parameter(n))).

А01234567

Question 4 6 marks

(a) The following table shows the voltages on inputs A and B for the circuit shown below. H corresponds to a voltage above the gate threshold voltage and L corresponds to 0 V.

Fill in the last column of the table with the voltage at point F of the circuit. Use H for a voltage of approximately  $V_{dd}$  and L for a voltage of approximately 0 V.

| А | В | F |

|---|---|---|

| L | L |   |

| L | Н |   |

| Н | L |   |

| Н | Н |   |

- (b) An IC has specifications of  $V_{\rm IL} = 0.3 \, \rm V$  and  $V_{\rm IH} = 0.7 \, \rm V$ . If you needed a noise margin of  $0.2 \, \rm V$  for both high and low voltages, what are the required maximum  $V_{\rm OL}$  and minimum  $V_{\rm OH}$ ?

- (c) A circuit draws 50 mA when operating with a clock frequency of 50 MHz. You would like to operate this circuit for a year when powered by a CR2016 battery that has a capacity of 100 mAh. What clock frequency should you use? *Hints:* P = IV. V does not change. There are  $365 \times 24 = 8760$  hours in a year.

A01234567 3