## **Static Timing Analysis**

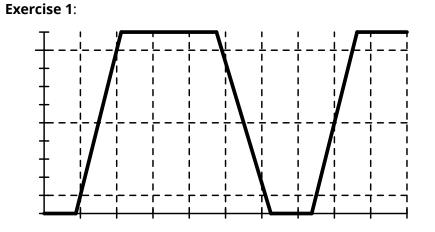

The diagram above shows an oscilloscope screen capture that includes one period of an *active-low* digital waveform. The scale on the horizontal axis is 20 ns per division. What are: the rise time, period, positive pulse width and duty cycle?

## Exercise 2:

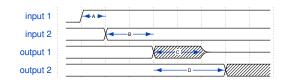

Label the specifications A through D as requirements or guaranteed responses. Which specifications are measured to a signal being in a high-impedance state? Which are measured from a rising edge only? From either?

**Exercise 3**: Is  $t_{PD}$  a requirement or a guaranteed response?

**Exercise 4**: Is  $t_{SU}$  a requirement or a guaranteed response? How about  $t_{H}$ ?

## Exercise 5:

$t_{SU}$  (avail) =  $T_{clock}$  -  $t_{co}$  (max) -  $t_{PD}$  (max)

Which of the specifications in the formula above decrease the available setup time as they increase? Which increase it? **Exercise 6**: For a particular circuit  $f_{clock}$  is 50 MHz,  $t_{co}$  is 2 ns (maximum), the worst-case (maximum)  $t_{PD}$  in a circuit is 15 ns and the minimum setup time requirement is 5 ns. What is the setup time slack? Will this circuit operate reliably? If not, what it the maximum clock frequency at which it will?

**Exercise 7**: What is the maximum clock frequency for a counter using flip-flops with 200 ps setup times, 50 ps clock-to-output delays and adder logic that has a 250 ps propagation delay?