## **Analog Interfaces**

**Exercise 2**: What minimum sampling rate would be required to digitize a 10 kHz square wave if you wanted to be able to recover frequency components up to the 7'th harmonic (at 70 kHz)?

**Exercise 3**: A signal with range of  $\pm 3$  V must be quantized so that the maximum *quantization error* is less than 1 mV. What is the resolution in mV? What minimum number of bits of resolution is required?

$$|o_{Jz}(z^n)| = |o_{Jz}(\frac{6}{0.00z})$$

$$n > 11.55$$

1ce  $n=12$  bits of resolution

Exercise 4: When quantizing a full-scale sine wave, what quantization SNR would be achieved with a resolution of 12 bits? What if the signal's voltage range was only half of the full-scale range?

$$n = 12$$

Sur (dB) = 1.76+6n = (.76+6.12) = 7.3.76  $= 7.3.76$

$$P = V^{2}$$

$$P_{1} = V_{1}^{2}$$

$$P_{2} = V_{2}^{2} = \left(\frac{V_{1}}{2}\right)^{2} = \frac{V_{1}}{4}$$

new

$$SNR = \frac{S/4}{N} \Leftrightarrow \frac{S}{N} - 6 dB$$

$$= 74 - 6 = 68 dB$$

$$= 74 - 6 = 68 dB$$

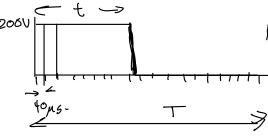

**Exercise 8**: You are using a PWM DAC to convert a 200 VDC supply to a 48 VDC output. The clock frequency is 25 kHz. What is the pulse duration?

$$V_0 = V_{\text{ref}} \cdot \frac{t}{T}$$

$$\frac{t}{T} = \frac{48}{200}$$

$$H8 = 200 \cdot \frac{t}{T}$$

H8 =

$$200 \cdot \frac{t}{T}V$$

QSSONE  $N = 10$

$Z^{N} = 1624$

$T = Tolode \cdot 2^{N} = 40 ms \cdot 1029 2 40 ms$

$$t = T \cdot \frac{48}{200} = 40 \times 10^{-3} \cdot \frac{48}{200} =$$

Exercise 9: You are designing a PWM DAC and need resolution of 1 mV with a full-scale output of 12 V. How many bits of resolution are required? The pulse frequency is 10 kHz. What is the clock frequency?

$$\frac{12 \text{ V}}{1 \text{ mV}} = 12,000$$

$$2^{n} > 12,000$$

$$1092 12000$$

$$> 13.5$$

$$0se n = 14$$

$$\frac{1}{\sqrt{1 + \frac{1}{2}}} = \frac{1}{\sqrt{1 + \frac{1}{2}}}$$

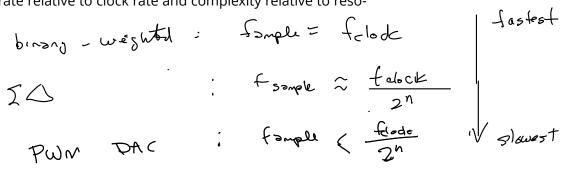

**Exercise 10**: Rank the different DACs described above in terms of sampling rate relative to clock rate and complexity relative to resolution.

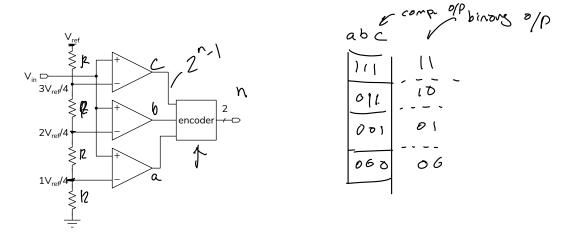

Exercise 11:

Draw a diagram showing the voltage ranges, the comparator outputs and the binary output for the 4-bit flash ADC above.

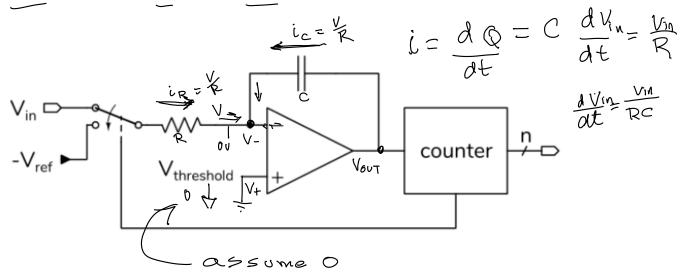

**Exercise 14**: What is the slope of an integrator, in V/s, when charging a 100 nF capacitor with 5 V through a  $100 \, k\Omega$  resistor?

$$\frac{\partial p - Amps 101}{V_{out} = A_v(V_+ - V_-)}$$

$$V_{out} = A_v(V_+ - V_-)$$

Solve =

$$\frac{V}{RC} = \frac{5}{100 \times 10^{-9} \times 100 \times 10^{3}}$$

=  $\frac{5}{10^{4} \times 10^{-9}} = \frac{5}{10^{-2}} = \frac{500 \text{ s}}{10^{-2}}$