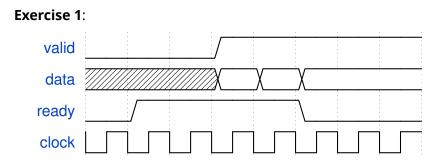

Mark the clock edges where data is transferred.

## Exercise 2:

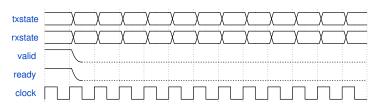

Draw the state transition diagrams for the transmitter and receiver if the transmitter has a data word ready two clock cycles after the previous one is read and the receiver requires three clock cycles to process each received word. Draw the timing diagram assuming valid and ready are asserted to start with.

## Exercise 3:

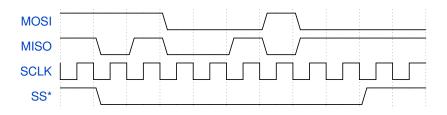

The diagram above shows a transfer over an SPI bus. How many bits of data are transferred? What is the value, in decimal, of the data transferred from the master to the slave? From the slave to the master?

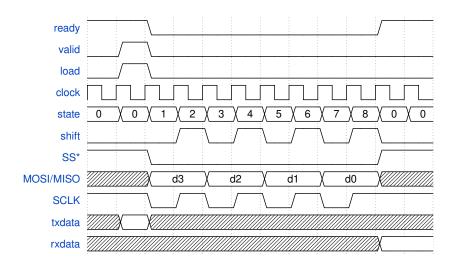

The diagram above shows the signals and state variable for a 4-bit SPI interface. The controller sequence generator states use a binary encoding. Write a state transition table for this state machine. Write Verilog expressions for the controller outputs.