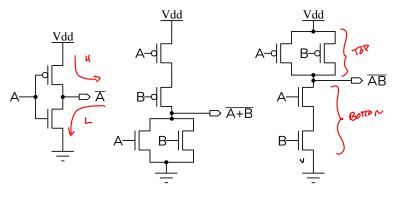

## **Implementation of Digital Logic Circuits**

NAND

| .A | В   | DE  | BOTION O/P |

|----|-----|-----|------------|

| 0  | 0   | 50  | OFT 7      |

| 0  | ) ( | ON  | OFF (HIGH  |

| ١  | 0   | ON  | OFE )      |

| ١  | 1   | OFF |            |

|    | I   |     |            |

In which direction does the output current flow when the output is high? When it is low? Which transistors in the NAND circuit are on (conducting) in each case?

**Exercise 2**: A logic family has  $V_{OH}(min) = 5 \text{ V}$ ,  $V_{OL}(max) = 0.5 \text{ V}$ ,  $V_{IH}(min) = 4 \text{ V}$  and  $V_{IL}(max) = 1.5 \text{ V}$ . What are the noise margins?

- noise margin(low) =  $V_{IL(max)} V_{OL(max)}$

- noise margin(high) =  $V_{OH(min)} V_{IH(min)}$

**Exercise 3**: All else being equal, by how much would we expect to decrease power consumption when reducing logic levels from 5 V to 3.3 V? What would be the effect on power consumption in reducing the clock frequency from 50 MHz to 1 MHz?

$$\frac{P_2}{P_1} = \frac{f_2}{f_1} \cdot \left(\frac{V_2}{V_1}\right)^2$$

=Voh - Vih = 5 - 4 = 1V

′il - Vol = 1.5 - 0.5 = 1∨

power after change:  $P_2 = P_1 \cdot rac{f_2}{f_1} \cdot \left(rac{V_2}{V_1}

ight)^2$

percent reduction in power consumption:  $R=-rac{\left(P_2-P_1

ight)}{P_1}\cdot 100$

percent eduction in power at 3.3 V  $R\left(V_1=5\left[V

ight],V_2=3.3\left[V

ight],f_2=f_1

ight)=~56$

percent eduction in power at 1 MHz:  $R(f_1 = 50 [MHz], f_2 = 1 [MHz], V_2 = V_1) = 98$

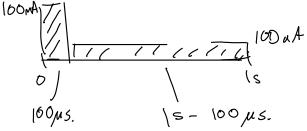

**Exercise 4**: If a circuit draws 100 mA for  $100 \mu \text{s}$  per second and draws  $100 \mu \text{A}$  the rest of the time, how long will a 1000 mAh battery last?

on time, on current:  ${T_{\mathit{on}}} = 100\left[ {us}

ight],{I_{\mathit{on}}} = 100\left[ {mA}

ight]$

off time, off current:  ${T}_{off} = 1\left[s

ight] - {T}_{on}, {I}_{off} = 100\left[uA

ight]$

average current:

$$I_{avg} = rac{I_{on} \cdot T_{on} + \ I_{off} \cdot T_{off}}{T_{on} + T_{off}} = [uA] \ = 110 \, [uA]$$

battery capacity:  $C = 1000 \left[ mA \cdot h \right]$

battery duration:

$$T = rac{C}{I_{avg}} = [years] = 1.04 \, [years]$$

**Exercise 5**: 18650 cells weigh about 50 g, output 3.7 V and have a capacity of 3500 mA-h. How many cells are needed to build an 85 kWh EV battery? How much does it weigh?

batttery capacity in Joules:  $C_{bat}=85\,[kWh]=~3.06 imes10^8\,[J]$

cell capacity in Joules:  $C_{cell} = 3.7 [V] \cdot 3500 [mA \cdot h] = 46620 [J]$

number of cells required to make up battery:  $N_{cell} = rac{C_{bat}}{C_{cell}} = ~6564$

weight of cell:  $W_{cell} = 50 \left[g

ight] = \left[g

ight] = 50 \left[g

ight]$

weight of battery:  $W_{battery} = W_{cell} \cdot N_{cell} = 328.2 [kg]$

$$\frac{18 \text{ mm}}{18650 \text{ cell}} = \frac{7}{\sqrt{23}} \frac{18650 \text{ cell}}{1}$$

$$= \frac{7}{\sqrt{23}} \frac{1}{\sqrt{23}} \frac{1}{\sqrt{2$$

**Exercise 6**: What are the active-state current and the RC time constant for a wired-or interrupt-request line using a  $10k\Omega$  resistor pulling up a circuit with 50 pF capacitance to 3.3 V?

$$I = \frac{V}{R} = \frac{0.33 \text{ mA}}{\frac{33}{4}}$$

$$I = \frac{V}{R} = \frac{0.5 \text{ ms}}{\frac{33}{4}}$$

12

-

2 mm

**Exercise 7**: The Apple M3 CPU has an area of approximately 146 mm<sup>2</sup>. How many die fit on one 300 mm wafer? If each wafer costs \$20,000 to manufacture, what is the cost per die?

die per wafer:

$$N = \frac{\pi \cdot \left(\frac{300 \ [mm]}{2}\right)^2}{146 \ [mm^2]} = 484.15$$

cost per die:  $\frac{20000}{N} = 41.31$

$\sqrt{146} = 12.08$

$\sqrt{146} = 12.08$

**Exercise 8**: How many square mm of PCB area does each package require? Which packages have their pins accessible when the package is placed on the PCB?

TQFP: anea =

$$22 \text{ mm}^2$$

$n_2 2000 \text{ mm}^6$

Bat ana =  $3.5 \text{ mm}^2$   $\approx 12 \text{ mm}^2$