## **Sequential Logic and State Machines**

**Exercise 1**: Write the Verilog for an 8-bit counter named 'n'. Modify it so that the register value is set to 0 each time it reaches 99. Draw the corresponding block diagram. Identify the next-state combinational logic.

$$logic (7:0]n;$$

$$always_f @ (posedge clk)$$

$$h <= n == 99? 0 : n+1;$$

$$n == 99? 0 : n+1;$$

$$n == 99? 0 : n+1;$$

**Exercise 2**: Write a 4-bit counter named 'cnt' with reset, enable, and down inputs. reset should have priority over enable. Draw the block diagram.

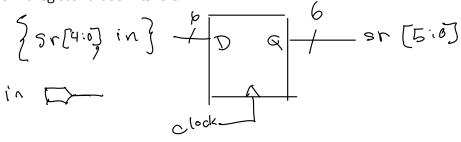

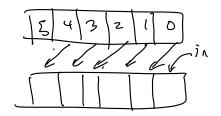

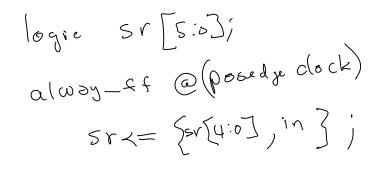

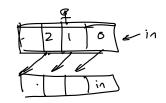

**Exercise 3**: The example above is an N-bit shift register that shifts the bits right. Draw a block diagram and write the Verilog for a 6-bit shift register that shifts left.

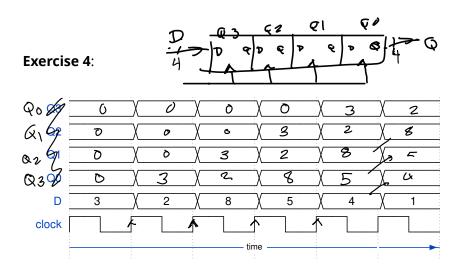

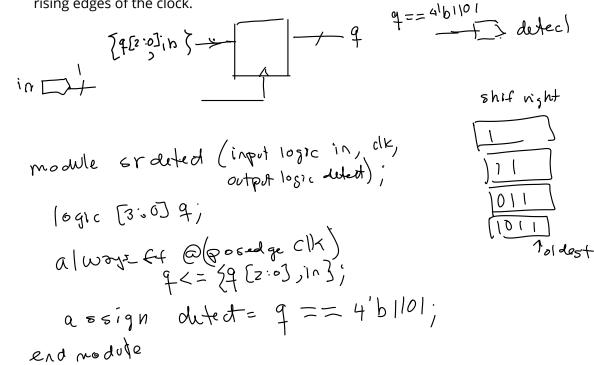

Fill in the diagram above for a 4-bit (N = 4) right-shift shift register. Assume the initial value is zero. Which bit is the oldest (first) value in the waveform? Which bit of the shift register holds the oldest value? **Exercise 5**: Draw a block diagram and write the Verilog for a circuit that sets an output named **detect** high when the sequence of values 1, 1, 0, 1 has appeared on an input named **in** on successive rising edges of the clock.

Shift left

) ]

ιιΟ

110

oldest

**Exercise 6**: What value of *N* would result in a 20 ms delay if the clock frequency is 50 MHz? How many bits are needed for this timer's register?

$$T = \frac{1}{f} = \frac{1}{50\times106} = 20\times10^{-9} (2005)$$

$$2005 = 20\times10^{-3}$$

$$NT = delay \qquad N = \frac{delay}{T} = \frac{2/4(6^{-3})}{2/0\times10^{-9}} = 100^{6}$$

$$N = (\times10^{6} = \frac{1000000}{10-1} = \frac{999}{999} \dots \frac{9}{9}$$

with b bits con represents fm o to  $2^{5}-1$

test: b = 10 6...  $2^{10}-1 = 1023$

b = 20 9...  $2^{2^{2}}-1 \approx 10^{6}$

max =  $2^{5}-1$

b =  $(0 \leq 2^{10}-1) = 1023$

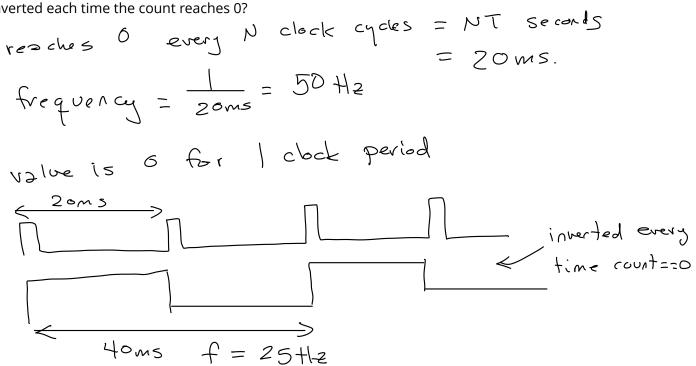

**Exercise 7**: Assume the timer above is reset to N - 1 each time it reaches 0. What is the time between each time the count reaches zero? What is this frequency? For how long does the register have the value 0? What are the period and frequency of a signal that is inverted each time the count reaches 0?

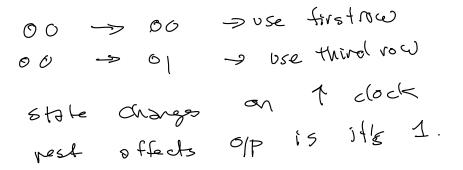

**Exercise 8**: For the state machine described above, if the current state is 01, what will be the next state? When will the state change? What is the output in state 00? In state 01? In state 10?

00 -> 0 01 -> 0 10 -> 1

01 -> 10 (if result not >=serted). State alroyers on rising edge of clack.

**Exercise 9**: What will be the next state if the state is 00 and the **reset** input is 1? If the state is 00 and the **reset** input is 0? When does the state change? When does **reset** affect the output?

**Exercise 10**: Write the above state transition and output tables using state names A, B, C, and D.

| state | reset | next  |

|-------|-------|-------|

|       |       | state |

| XX    | 1     | 00    |

| 11    | 0     | 00    |

| n     | 0     | n+1   |

$A = \infty$  $B = \infty$ C = 10D = 11

e.j.

| state      | reset | next   |

|------------|-------|--------|

| <br>X<br>D | 10    | A<br>A |

| A          | 0     | ts l   |

| B          | 6     |        |

| C          | 0     |        |

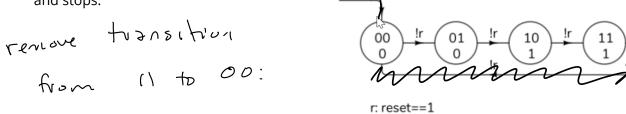

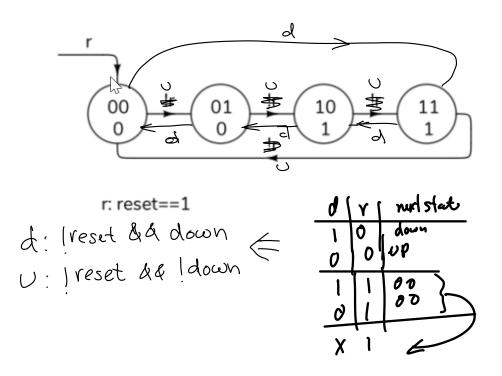

**Exercise 11**: Modify the diagram so the stat and stops.

**Exercise 12**: Add a **down** input that cause the values to count down.

**Exercise 13**: How many bits need to be considered to detect a specific state when a binary encoding is used? How many need to be considered if a one-hot encoding is used?

**Exercise 14**: If we used 8-bits of state information, how many states could be represented? What if we used 8 bits of state but used a "one-hot" encoding?

$$binary: 2^8 = 256$$

one-not: 8