# **Solutions to Quiz 4**

There were two versions of each question. The values and the answers for both versions are given below.

## Question 1

Fill in the testbench module at right with code that uses **initial** and **always** statements, not loops, to do the following:

- (a) set the initial value of n to 0

- (b) terminate the simulation with \$stop() if the value of n is ever equal to (or greater than) 8'd127.

- (c) add 1 (or 2) to **n** every 5 (or 10)µs, and

- (d) print the current value of n every 20 (or 40)μs (using \$display())

```

module quiz_tb ;

logic [7:0] n ;

endmodule

```

#### **Answers**

```

module quiz_tb ;

logic [7:0] n;

initial begin

n = 0;

// (a)

wait (n == 8'd127) $stop; // (b)

always \#5us n = n + 1;

// (c)

always #20us $display(n) ;

endmodule

module quiz_tb_ ;

logic [7:0] n;

initial begin

n = 0;

// (a)

wait (n > 8'd127) $stop; // (b)

always #10us n = n + 2;

// (c)

always #40us $display(n) ;

endmodule

```

which produce the following output:

```

# 3

# 7

# 11

...

# 119

# 123

and

# 6

# 14

# 22

...

```

# 126

### **Question 2**

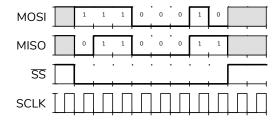

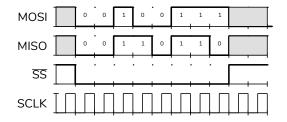

Draw the SS, MISO, and MOSI waveforms that would be used to transfer bytes with values 8'h36 (or 8'h63) (in Verilog notation) from the slave to the master and 8'h27 (or 8'h72) from the master to the slave over an SPI interface. Follow the conventions shown in the lecture notes, including the timing of SS relative to the data, the data relative to SCLK, and the bit order.

## Answers

The SPI interface transfers bits from slave to master over MISO and from master to slave of MOSI. The bits are transferred m.s.b. (most significant bit) and  $\overline{SS}$  is low while the bits are being transferred. In the examples in the lecture notes, the rising edge of the clock appears in the middle of the bit interval.

The diagrams below show the waveforms annotated with values of the bits transferred in each bit interval.

or