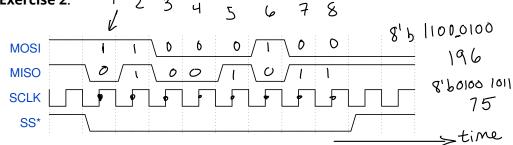

The diagram above shows a transfer over an SPI bus. How many bits of data are transferred? What is the value, in decimal, of the data transferred from the master to the slave? From the slave to the master?

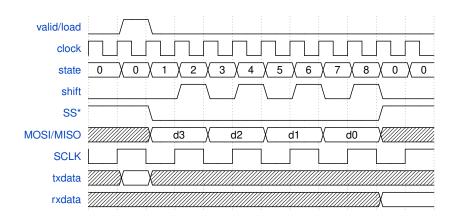

## Exercise 3:

Based on the diagram above, write a state transition table for an SPI interface controller that transfers four bits at a time. Include an idle state. In which states are **SCLK** and **SS** asserted?

| te. In which states are oblic and oblisserted. |          |               |                           |

|------------------------------------------------|----------|---------------|---------------------------|

| Sble                                           | 0 il 6V  | next<br>stale | o = idle                  |

| Ō                                              | $\vec{}$ | 1             |                           |

| 8                                              | 6        | Ø             |                           |

| 8                                              | ۱        | )             |                           |

| $\sim$                                         | ×        | n+1           |                           |

| SCLK asserted in even states (2,4,6,8)         |          |               |                           |

| <br>55                                         | JSSer-   | ted in        | non-zero states (1 to 8). |