#### ELEX 2117 : Digital Techniques 2 2024 Winter Term

# Simulation

This lecture describes how to use Verilog to simulate designs.

After this lecture you should be able to write a testbench that can: set initial values, generate clocks, read test vectors from a file, display values, and terminate on a condition.

#### Simulation

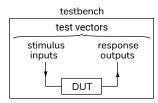

In addition to using HDLs to design hardware, they can also be used to test these designs by simulating their operation. A simulation consists of the module being tested (called the Design Under Test or DUT) that is instantiated in another module called a testbench. The testbench applies inputs to the DUT and checks its outputs:

### **Test Vectors**

The inputs to the DUT and the corresponding expected outputs are called test vectors. These can be generated by the testbench itself or they can be read from a file.

Test vectors should include:

- 1. typical inputs,

- 2. minimum and maximum valid inputs,

- 3. invalid inputs, and

- 4. randomly-chosen values.

**Exercise 1:** Give examples of appropriate test inputs for each of the above categories if you were testing a circuit that computed the square root of a 16-bit signed number.

## **Verilog for Verification**

The following Verilog features are useful for simulation but can't be synthesized (implemented in hardware).

## initial and always blocks

initial blocks execute once at the start of the simulation and are used to initialise signals. always blocks execute continuously. begin and end are used to group statements within these blocks (as with { and } in C).

# if/else/for/while

if/else, for, and while statements, whose syntax is similar to C, can be used in initial or always blocks. However, in HDL simulations control flow is often based on conditions or events as described below.

## Delays

Placing #number before a statement delays<sup>1</sup> execution by *number* simulation time. The suffixes **ns** and **us** can be used for nano- and micro-seconds.

The syntax @(*event*) where *event* can be **posedge** or **negedge** followed by a signal name or just the signal name delays execution until that signal edge or until a change in that signal's value.

## wait

The wait (*expression*) statement pauses until the expression is non-zero.

Exercise 2: What's the difference between wait(x) y='1; and @(x) y='1;?

## System Tasks

Functions beginning with **\$** are called system tasks. Useful ones include:

• **\$display()** similar to C's **printf()**, can be used to print values during a simulation;

<sup>&</sup>lt;sup>1</sup>Delays are not synthesizable because delays cannot be easily implemented in hardware.

|                 | 0    | 1    | ls   | 21   | S  | 31 | ls   | 4    | US          | 5 | ÚS   | 6    | lS   |      |

|-----------------|------|------|------|------|----|----|------|------|-------------|---|------|------|------|------|

| n=3             | 3    |      |      |      |    |    |      |      |             |   |      |      |      |      |

| reset=1         |      |      | 1    |      |    |    |      |      |             |   |      |      |      |      |

| clk=0           |      |      |      |      |    |    |      |      |             |   |      |      |      |      |

| in[7:0]=00      | 00   |      | 01   | _    | 02 |    | 03   |      | <b>)</b> 04 |   | 05   |      | 07   |      |

| out[15:0]=xxxx  | XXXX | 0000 |      | 0001 |    |    |      | 0004 |             |   |      | 0009 |      | 0000 |

| out_[15:0]=0000 | 0000 |      | 0001 |      |    |    | 0004 |      |             |   | 0008 |      | 0000 |      |

Figure 1: Simulation waveforms (from ex66.vcd).

- **\$dumpfile** and **\$dumpvars** record changes in signals to a .vcd file for subsequent viewing with a waveform viewer.

- **\$fopen()** and **\$fscanf()**, similar to the C library functions **fopen()** and **fscanf()**, can open and read from text files.

- **\$finish** and **\$stop** terminate or suspend a simulation.

#### Example

The testbench below demonstrates the language features described above.

The DUT is a module with an 8-bit input that outputs a 16-bit sum of all the odd-valued inputs since a reset input was asserted. An **initial** block opens a file containing test vectors, initializes the clock signal and **\$stop**'s the simulation at the end of the test vector file. Every  $0.5 \,\mu$ s the clock is inverted; this creates a 1 MHz clock.

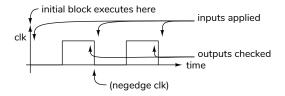

The final **always** block continuously reads and applies the input(s) from each test vector, waits for the falling edge of the clock, and compares the DUT output(s) to the value(s) read from the test vectors.

This examples changes the DUT input a half-cycle before the rising edge of the clock and checks it a halfcycle after. Delays can be added to change the timing.

The simulation code accesses the value of **out** within the DUT using the notation *<instance name>.<signal name>* (**ex66\_0.out** in this case). This violates the principles of modularity and "data hiding" but can be useful for troubleshooting.

The test vectors are read from the file **ex66data.csv** containing the following lines<sup>2</sup>:

1,0,0 - 0,1,1 0,2,1 0,3,4 0,4,4 0,5,8 1,7,0

> Running this testbench using the Modelsim simulation program creates the waveform files shown in Figure 1. The following lines are printed showing the input, actual output and the expected output given in the test vector:

| # | test vector=1, | 0, | 0 |   |

|---|----------------|----|---|---|

| # | DUT state =    | 0  |   |   |

| # | test vector=0, | 1, | 1 |   |

| # | DUT state =    | 1  |   |   |

| # | test vector=0, | 2, | 1 |   |

| # | DUT state =    | 1  |   |   |

| # | test vector=0, | З, | 4 |   |

| # | DUT state =    | 4  |   |   |

| # | test vector=0, | 4, | 4 |   |

| # | DUT state =    | 4  |   |   |

| # | test vector=0, | 5, | 8 |   |

| # | DUT state =    | 9  |   |   |

| # | ***Error: 5,   | 9  | , | 8 |

| # | test vector=1, | 7, | 0 |   |

| # | DUT state =    | 0  |   |   |

| # | test vector=1, | 7, | 0 |   |

**Exercise 3:** How could you:

- (a) terminate the simulation if a test vector failed?

- (b) change the clock frequency to 10 MHz?

- (c) print each test vector as it's read?

- (d) assert the reset input for two clock cycles?

<sup>&</sup>lt;sup>2</sup>This file is in Comma Separated Values (.csv) format.

// output cumulative sum of odd-valued inputs

```

module ex66

( input logic reset, clk,

input logic [7:0] in,

output logic [15:0] out ) ;

always_ff @(posedge clk)

out <= reset ? '0 :

in & 1 ? out+in : out ;

</pre>

```

#### endmodule

```

// example testbench

```

```

module ex66_tb ;

```

```

// DUT inputs and outputs

logic reset, clk ;

logic [7:0] in ;

logic [15:0] out, out_ ;

// file descriptor and number of values by fscanf()

integer fd, n ;

// instantiate DUT

ex66 ex66_0 (.*);

// initialization

initial begin

// record all signals in a .vcd file

$dumpfile("ex66.vcd");

$dumpvars ;

// initialize clock

clk = '0 ;

// open the test vector file

fd = $fopen("ex66data.csv","r") ;

// stop at end of file or error

wait (n < 0) $stop ;</pre>

end

// generate 1 MHz clock (2x500ns period)

always #0.5us clk = ~clk ;

// continuously apply input, wait, & check output

always begin

// read & set DUT inputs; display test vector

n = $fscanf(fd, "%d, %d, %d", reset, in, out_) ;

$display ("test vector=%d,%d,%d",reset,in,out_);

// on falling clock edge

@(negedge clk) begin

// display DUT internal signals; check outputs

$display ( "DUT state = %d", ex66_0.out );

if ( out != out_ ) begin

$display("***Error: %d, %d",in,out,out_);

end

end

end

```

```

endmodule

```