## **Introduction to Digital Design with Verilog HDL**

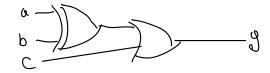

**Exercise 1**: What changes would result in a 3-input OR gate?

**Exercise 2**: What schematic would you expect if the statement was assign y = ( a ^ b ) | c :?

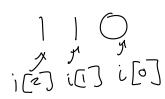

**Exercise 3**: If the signal **i** is declared as **logic** [2:0] **i**;, what is the 'width' of **i**?

If i has the value 6 (decimal), what is the value of i[2]?

1

Of i[0]?

Ο.

**Exercise 4**: What are the widths and values, in decimal, of the fol-

**Exercise 5**: What are the values of the following expressions:

14'6010?

$$|'b0| = |'h0|$$

-4'6010?  $|'b0| = |'h0|$

(or - reduction)

-4'61001?  $|'h0| = |'h0|$

(xor - reduction)

84'61111?  $|'h| = |'h0|$

84'61110?  $|'h| = |'h0|$

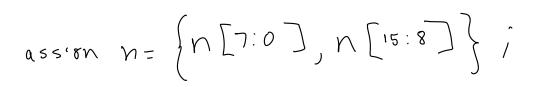

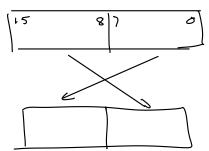

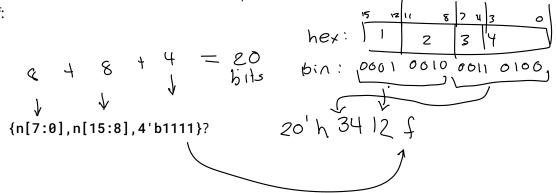

**Exercise 6**: Use slicing and concatenation to compute the byteswapped value of an array n declared as logic [15:0] n.

**Exercise 7**: If **n** has the value **16** ' **h1234**, what is the value and width

**Exercise 8**: Use concatenation to shift **n** left by two bits.

n [15:07

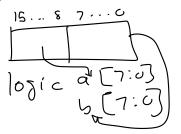

**Exercise 9:** Use concatenation to assign the high-order byte of  $\bf n$  to  $\bf a$  and the low-order byte to  $\bf b$ .

assign

$$\{a,b\} = n;$$

some result as

assign  $a = n[16:8];$

assign  $b = n[7:0];$

**Exercise 11**: An array declared as logic [15:0] n; and has the value 16'h1234. What are the values and widths of the following expressions?

$$\sim n[3:0]$$

$4'b1011 = 4'hb$

$$\frac{n + 1'b1}{|b|} \frac{|b'|}{|b'|} \frac{|b'|} \frac{|b'|}{|b'|} \frac{|b'|}{|b'|} \frac{|b'|}{|b'|} \frac{|b'|}{|b'|} \frac{|$$

$$n = 16'h1234$$

$$\frac{16'h1234}{\frac{16'h234}{16'heqcb}} = \frac{0001 0010 0011 0100}{\frac{1111 1111 1111}{1110 1111}} = \frac{xor inverts}{(negstes) each}$$

$$\frac{16'h1234 8 \times 1'h0}{\frac{1111 1111}{1110 1111}} = \frac{xor inverts}{(negstes) each}$$

$$\frac{1111 1111 1111}{\frac{1111}{1110 1111}} = \frac{xor inverts}{(negstes) each}$$

**Exercise 12**: What are the width and value of the expression: 3 ? 16'd10: 8'h20?

If  $\mathbf{x}$  has the value 0, what is the value of the expression: 1'b1: 1'b0?

If x has the value

$$\frac{-1}{2}$$

$\frac{1}{2}$   $\frac{1}$

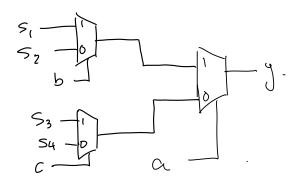

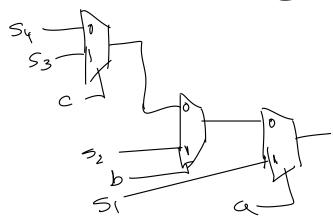

**Exercise 13**: Draw the schematics corresponding to:

$$y = a$$

(  $b$  ?  $\underline{s1}$  :  $\underline{s2}$  ) : (  $c$  ?  $\underline{s3}$  :  $\underline{s4}$  );

$$y = 2.51$$

:

$b. ? 52$ :

$c. ? 53:54$

## Exercise 14:

assign

$$y = a + 1$$

;

Some software warns about truncation. How could you re-write the assign statement to avoid such a warning?

Use assign

$$y = a + b$$

;

**Exercise 15**: Write an always\_ff statement that toggles (inverts) its output on each rising edge of the clock.

alway-ff @ (posedge clk)

$$q \le Nq \quad j$$

$$(or ! f \quad q \text{ is } 1 \text{ bit})$$

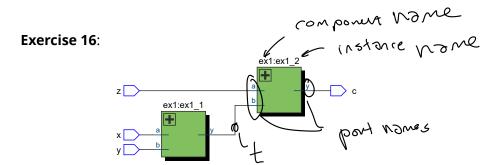

Identify the following in the diagram above: component names, component "instance names," component port names, module port names. Label the signal **t** in the schematic.

**Exercise 17**: Rewrite the **ex60** module using operators. Which version – "structural" or "behavioural" – is easier to understand?

## Exercise 18:

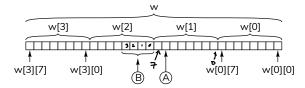

W [1] [6] How would you specify the bit marked A in the diagram above?

The bits marked B?  $\omega [2][3:0]$

w [0] The least-significant byte?

## Exercise 19:

```

X 15 4 bits: 4'60011

y 15 8 bits: 8' b 1010 (010

2 is 2×4 (ouptol) by (3 hounto 6)

// concatenation:

logic [3:0] x = \{ 2'b00, 2'b11 \} ;

// replication (z=8'b1010_1010):

logic [7:0] y = \{ 4\{2'b10\} \} ;

// arrav literal

Value 15 4 (60611, 41610)0

logic [0:1] [3:0] z = '\{ 4'b0011, 4'b1010 \} ;

```

What are the dimensions and initial values of x, y, and z in the examples above?

another example: if

$$logic [3:0][7:0] \times = \frac{1}{2} [1,2,3,4]$$

;

$$1 = \frac{1}{2} [1,2,3,4]$$

$$1 = \frac{1}{2} [$$