## **Analog Interfaces**

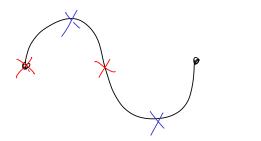

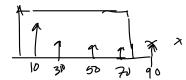

**Exercise 1**: Draw a sine wave and indicate two sets of sampling points at twice the frequency of the sine wave: one that demonstrates aliasing and one that does not. Is it sufficient to sample at twice the highest frequency of the analog signal?

No. fs > 2fmay

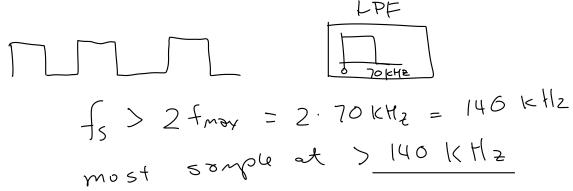

**Exercise 2**: What minimum sampling rate would be required to digitize a 10 kHz square wave if you wanted to include frequency components up to the 7'th harmonic (at 70 kHz)?

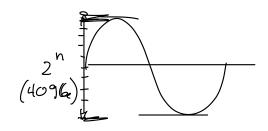

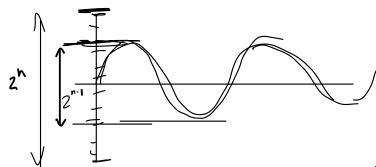

**Exercise 3**: A signal with range of  $\pm 3$  V must be quantized so that the quantization error is less than 1 mV. What minimum number of bits of resolution is required?

$$V = 6V = 3 - (3)$$

$$V = 6V$$

$$= 1 \text{mV}$$

$$2^{n} = \frac{6V}{|mV|}$$

$$n : \log_{Z} \left(\frac{6}{.001}\right) = |65_{Z}(6608)| = |2.5|$$

$$0 \text{ Se} \quad |3| \text{ bit resolution } ADC_{-}$$

**Exercise 4**: A signal-to-noise power ratio of about 48 dB is considered good enough for speech communication. Approximately how many bits per sample are required to obtain this quantization SNR?

$$48 = 6B$$

$B = \frac{48}{6} = 8 \text{ bits are needed}$

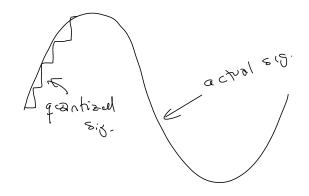

quantization

$$SNR = 1.76 + Gn$$

dB

=  $1.76 + 6.12$

$\approx 74$  dB

$$74 dB = 10 \log \frac{P_{signol}}{P_{roix}} = 10 \log \left(\frac{V_{sign}}{V_{rois}}\right)^{2}$$

$$= 20 \log \left(\frac{V_{signol}}{V_{rois}}\right)$$

AMM = quantization hoise

**Exercise 7**: You are using a PWM DAC to convert a 200 VDC supply to a 48 VDC output. The switching frequency is 25 kHz. What is the duration of each PWM pulse?

$$t = \frac{V_{out}}{V_{veg}}.T$$

$$= \frac{48}{200}.\frac{1}{25\times10^{3}}$$

$$= 9.6 \mu s.$$

**Exercise 8**: You are designing a PWM DAC and need resolution of 1 mV with a full-scale output of 12 V. How many bits of resolution are required? The pulse frequency is 10 kHz. What is the clock fre-

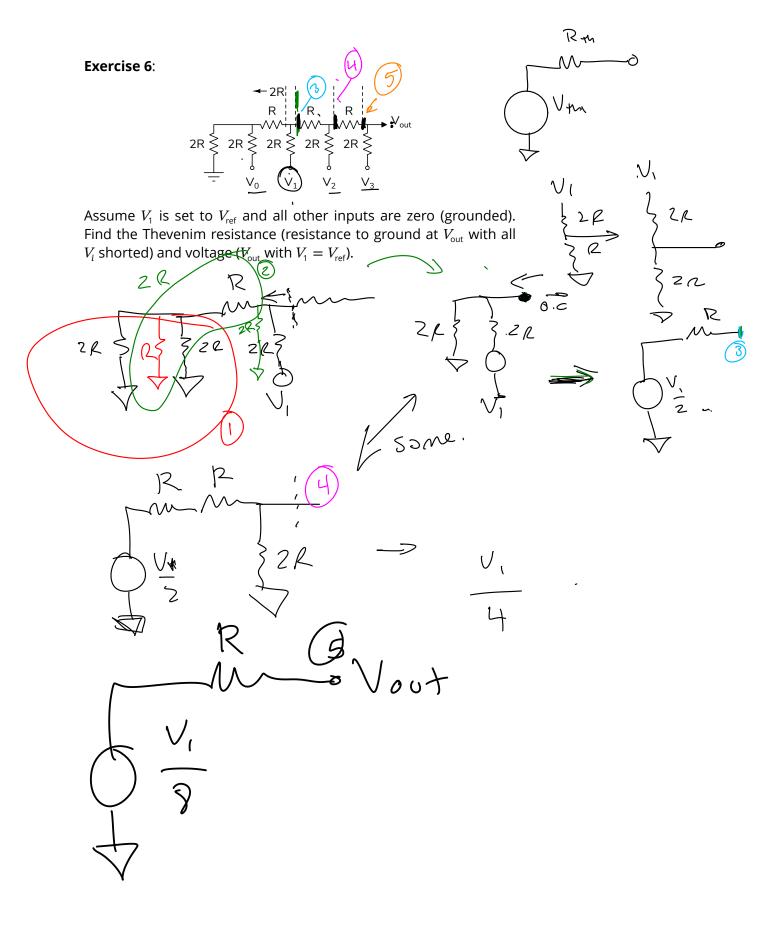

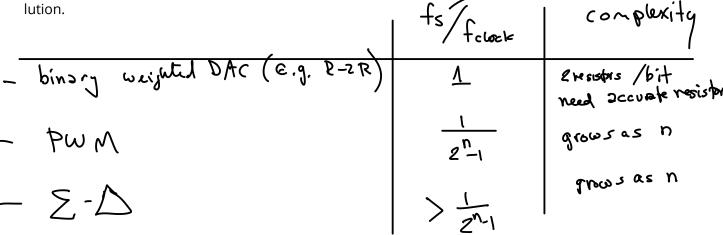

Exercise 9: Rank the different DACs described above in terms of sampling rate relative to clock rate and complexity relative to resolution

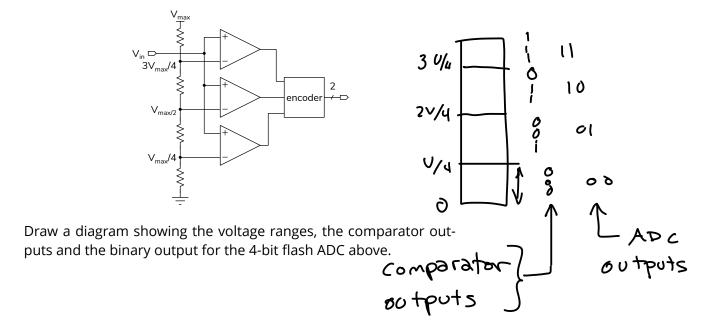

## Exercise 10:

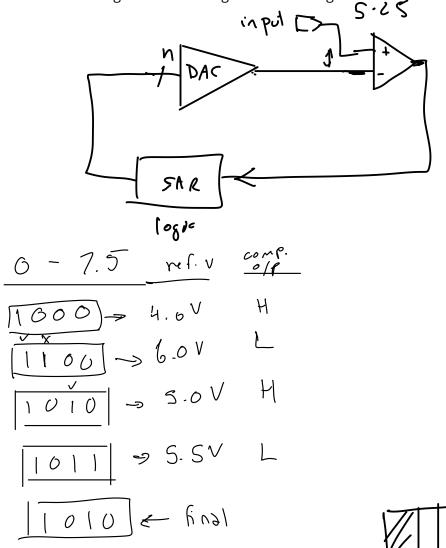

Exercise 11: A SAR ADC using a 4-bit DAC with a full-scale range of 0 to 7.5 V digitizes a 5.25 V signal. What voltages will the DAC output?

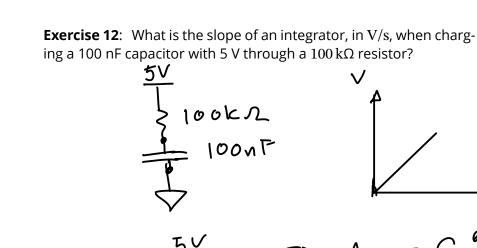

resistor?

$$i = C \frac{dV}{dt}$$

$$i(t=0) = \frac{5V}{100K} = 50 \text{ p.A} = C \frac{dV}{ott}$$

$$\frac{dV}{dt} = \frac{\dot{c}}{c} = \frac{50 \times 10^{-6}}{100 \times 10^{-9}} = 0.5 \times 10^{3} \left( \frac{500 \text{ V/s.}}{100 \times 10^{-9}} \right)$$

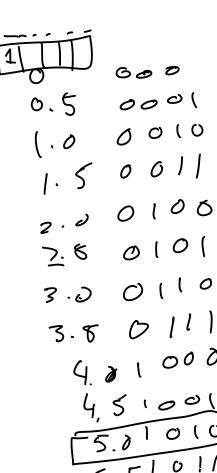

Exercise 13: Rank the different ADCs described above in terms of sampling rate relative to clock rate and complexity relative to resolution.

D(n) +1 con

|                | +5  |

|----------------|-----|

| rusler flash   |     |

| SAR            | ŧ   |

| 2 🛆            | \00 |

| dual-slope     |     |

| chesh no Lowb. |     |

accuracy

means increases proportional to h.