## **State Machines**

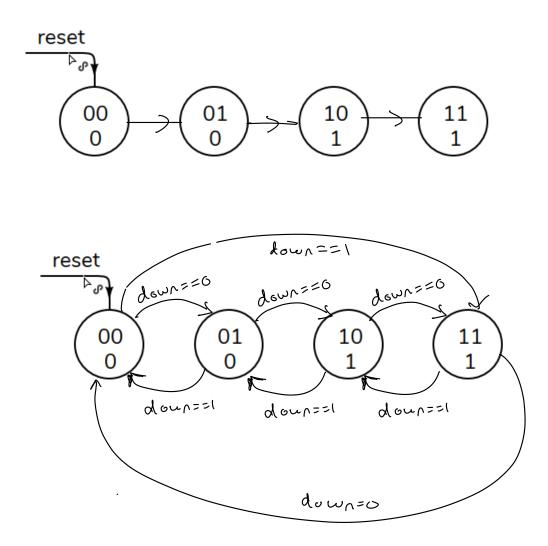

**Exercise 1**: Modify the diagram so the state machine counts to 11 and stops. Add a down input that cause the values to count down.

**Exercise 2**: Show the state transition diagram and table for a 2-bit counter with reset, enable, and down inputs. Reset should have priority. Write the Verilog.

$$\begin{array}{c|c} count & reset enable down & count \\ \hline \chi \chi & 1 & \chi & 0 & 0 \\ \hline n & 0 & 0 & \chi & h \\ \hline 1 & 0 & 1 & 0 & 0 \\ \hline 1 & 0 & 1 & 0 & 0 \\ \hline 0 & 0 & 1 & 1 & 11 \\ \hline n & 0 & 1 & 0 & -1 \\ \hline n & 0 & 1 & 1 & h-1 \end{array}$$

**Exercise 2**: Show the state transition diagram and table for a 2-bit counter with reset, enable, and down inputs. Reset should have priority. Write the Verilog.

| Count                             | reset                 | ensble  | down      | count &                                                                                          |

|-----------------------------------|-----------------------|---------|-----------|--------------------------------------------------------------------------------------------------|

| $\chi \times$<br>h<br>1<br>0<br>n | 1<br>0<br>0<br>0<br>0 | X O 1 1 | × × Ø - O | 0<br>0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 |

| $\sim$                            | 0                     |         | l         | v ( -                                                                                            |

**Exercise 3**: What value of *N* would result in a 20 ms delay if the clock frequency is 50 MHz? How many bits are needed for this timer's register?

elock frequency =

$$f = \frac{50 \times 10^6}{12}$$

clock period =  $T = \frac{20 \times 10^{-3}}{120}$

delay =  $t = NT = \frac{20 \times 10^{-3}}{120}$

clock cycles =  $N = \frac{t}{T} = \frac{20 \times 10^{-3}}{20 \times 10^{-3}} = 10^6$

**Exercise 4**: Assume the timer above is reset to N - 1 each time it reaches 0. For how long is the register value 0? What are the period and frequency of a signal that is inverted each time the count reaches 0?

T

**Exercise 5**: Write the state transition table for the state machine for the **lights** output.

| for the <b>lights</b> output. |        |       |          | hext           |

|-------------------------------|--------|-------|----------|----------------|

|                               | lights | reset | court    | next<br>(ignts |

| count==0 count==0             | ×      | l     | $\times$ | rg             |

|                               | rg     | O     | Q        | vy             |

|                               | YЧ     | 0     | 0        | gr             |

| count==0                      | gr     | 0     | ð        | yr             |

|                               | yr     | 6     | 0        | r g            |

|                               | n<br>N | P     | 70       | $\sim$         |

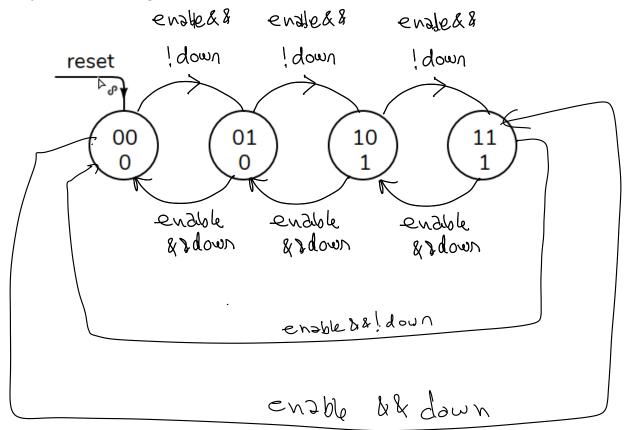

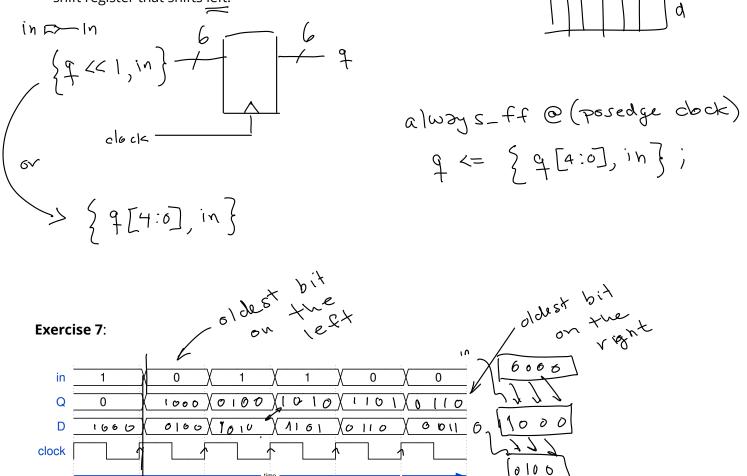

**Exercise 6**: The example above is an N-bit shift register that shifts the bits right. Draw a block diagram and write the Verilog for a 6-bit shift register that shifts left.

i٥

Fill in the diagram above for a 4-bit (N = 4) right-shift shift register. Assume the initial value is zero. Which bit is the oldest (first) value in the waveform? Which bit of the shift register holds the oldest value?

$$\{in, Q[3:1]\}$$

D c

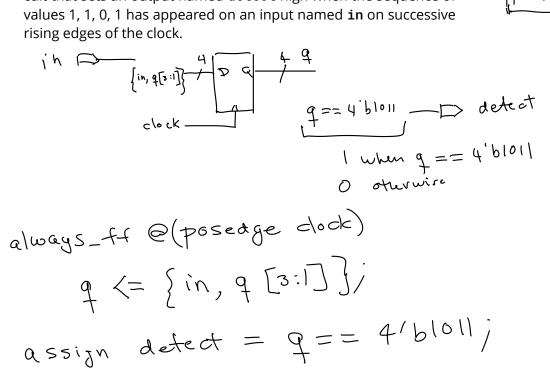

**Exercise 8**: Draw a block diagram and write the Verilog for a circuit that sets an output named **detect** high when the sequence of values 1, 1, 0, 1 has appeared on an input named in on successive rising edges of the clock.

-> 1011

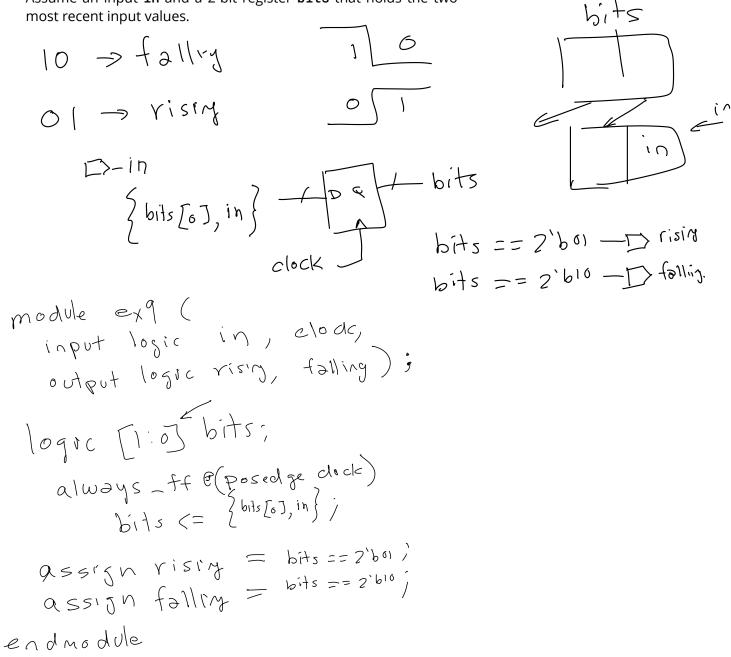

**Exercise 9**: For which states would **falling** be asserted? **rising**? Draw the schematic and write the Verilog for this state machine. Assume an input **in** and a 2-bit register **bits** that holds the two most recent input values.

**Exercise 10**: Write **always\_ff** statements that implement these state machines.

| count | in out    | next  |  |

|-------|-----------|-------|--|

|       | in == out | count |  |

| x     | 1         | N-1   |  |

| 0     | х         | N-1   |  |

| n     | 0         | n-1   |  |

0

in ⊃—

count != 0 ►

clock ⊳