## **More Verilog**

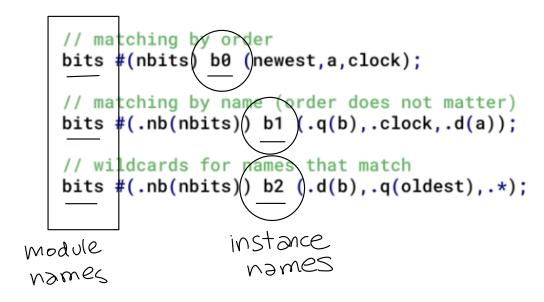

**Exercise 1**: Identify the module instantiation statements in the code above. For each one, what is the instantiated module's name? The instance name?

**Exercise 2**: How would you specify the bit marked ??? in the diagram above?

W[][6]

**Exercise 3**: Write a Verilog lookup table to look up whether a value between 0 and 7 is a prime number or not. The result should be 1 if the value is a prime or else 0. *Hint: The primes are 2, 3, 5 and 7.*

| 0 | 0 | $ ogic $ isprime $(0:7] = {0,0,1,0,1,0,1}$ |

|---|---|--------------------------------------------|

|   | 0 |                                            |

| 2 | 1 | examples:                                  |

| 3 |   | isprime [3] = 1                            |

| 4 | 0 | isprime [0] = 0                            |

| 5 | 1 |                                            |

| 6 | 0 |                                            |

| 7 |   |                                            |

**Exercise 4**: Is a signal named **overload** active-high or active-low? Is there an overload if this signal is high? What if the signal was named overload?

**Exercise 5**: Come up with active-high and an active-low names for a signal that is at 3 V when a door is open and 0 V when the door is closed.

signal: 3V = open OV = closed

active high: open

active low: dosed

**Exercise 6**: If  $\overline{D}$  is a data bus and  $\overline{D0}$  is low, is the value on the data -bus-an even or odd number?

BN

Do = active low = the tolow

. odd number