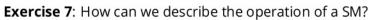

## State Machines

(see section 7-14 in text for related

**Exercise 1**: Why do I need to know this?

material)

for Lab 5 & Lab Exam #1

**Exercise 2**: In theory, what is a SM? What isn't a SM?

-ong thing with memory is a SM (in theory) - if no mmory (tt, registers) then it's not a SM.

Exercise 3: How large a SM is it practical to design? (how many states)

~ | page ) if larger, then decompose < 20? States. } decompose to smaller SMS.

**Exercise 4**: What are some things we could design as SMs?

- elevator - traffic light - >larms

**Exercise 5**: What are some things we would not design as a SM? Why?

too may states too complicated. (but parts of the CPU would be)

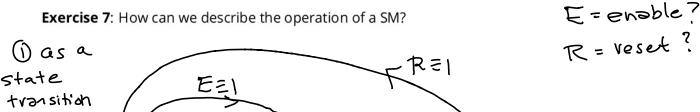

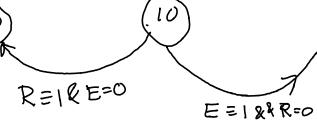

**Exercise 6**: What defines the state of a SM?

di agram

the contents of registers/FFs.

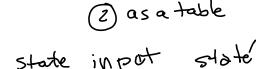

11

| State | MBON    | 57010 |

|-------|---------|-------|

|       | も々      |       |

| 00    | (۲<br>۲ | 1 0   |

| 10    | 0 1 0   | 00    |

| 1 \   | X       | 00    |

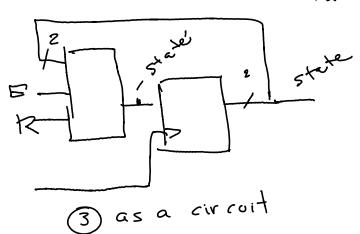

Exercise 8: Can a design have multiple state machines?

yes, very common.

**Exercise 9**: How can one SM control another?

through their states or their state transitions (events).

Exercise 10: What are the steps in designing a SM?

Exercise 11: Show me some examples!

see lecture 6.