## **Counters, Timers, State Machines**

**Exercise 1**: Why do I need to know this?

(see section 7-12

of the tool

for related

moterial)

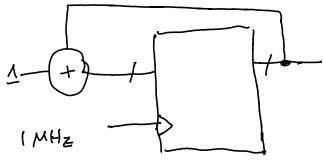

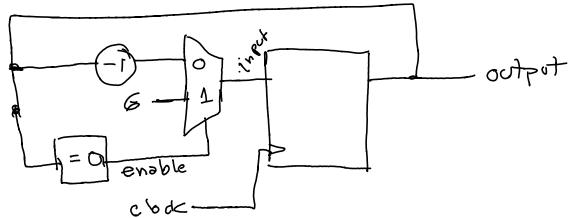

**Exercise 2**: Draw a register with a clock running at 1 MHz. The input comes from an adder that adds 1 to the output. Assume the initial register value is zero.

**Exercise 3**: What values appear at the register output?

**Exercise 4**: When does the output change?

on vising edge of the clock

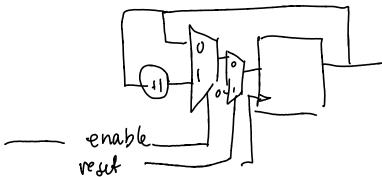

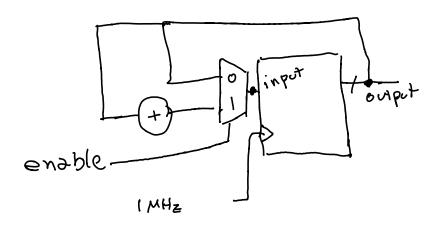

Exercise 5: Now add a multiplexer with an enable that selects the output of the adder or the current value of the register.

**Exercise 6**: What values appear at the output when the enable is asserted? When it is not?

| 1, | os serter | tonds |

|----|-----------|-------|

| 14 |           | 6     |

|    | C         | O     |

|    | \         | σ     |

|    | 2         | σ     |

|    | 3         |       |

|    | •         |       |

|    | ,         |       |

**Exercise 7**: When is the register loaded?

**Exercise 8**: When is the register loaded with a new value?

**Exercise 9**: If the enable lasts for one clock cycle, by how much will the register change?

**Exercise 10**: If the enable is generated as the output of another register, when does it change?

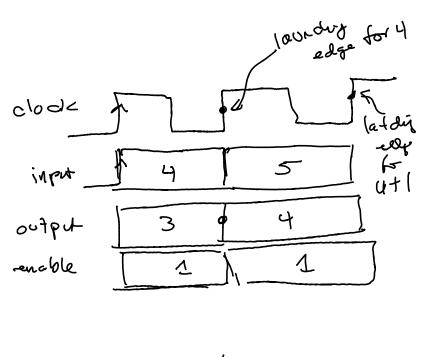

**Exercise 11**: Draw the clock, the enable and the register output as a function of time (ignore propagation delays).

**Exercise 12**: Label a launching edge. Label the corresponding latching edge. How much time separates them?

1 period, MS.

**Exercise 13**: How much time is allowed for the signal to travel through the adder and multiplexer?

Exercise 14: What values are produced if we replace the adder with a subtractor, the mux selects between the new value and the value N=1, and the enable is asserted only when the register value is zero?

| output       | 0 6 | 5 | 4 | 3 | 2 |   | 0 | 6  | 5 |

|--------------|-----|---|---|---|---|---|---|----|---|

| enable (= 0) | 1 0 | 0 | 0 | 0 | 6 | 0 | 1 | 0  | 6 |

| input        | 6 5 | 4 | 3 | 2 | 1 | 0 | 6 | TE | 4 |

|              | 1   | 2 | 3 | A | 5 | 6 | 7 | 1  |   |

**Exercise 15**: What is the duration of the zero-detected signal? ( e nable)

I clock period

**Exercise 16**: How often does the counter get reset to N = 17. What is the period? What is the frequency?

every N = 7 clock cycles.

| MS X 7 clock cycles

7 ms.  $\approx 114 \text{ kHz}$

**Exercise 17**: Why do we call this a timer?

measures clock pensons => measures time.

**Exercise 18**: Draw the clock, timer values and zero-detect (ignore propagation delays).

(see above).

**Exercise 19**: Why do we count down and detect zero instead of counting up and detecting some other value?

**Exercise 20**: How can we detect a zero value without OR'ing all the bits?

0010

**Exercise 21**: Can we use one timer to control another? What signal do we use?