## **Examples of State Machines**

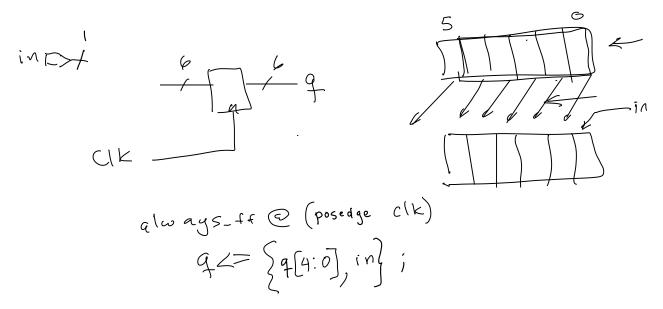

**Exercise 1**: The example above is an N-bit shift register that shifts the bits right. Draw a block diagram and write the Verilog for a 6-bit shift register that shifts left.

## Exercise 2:

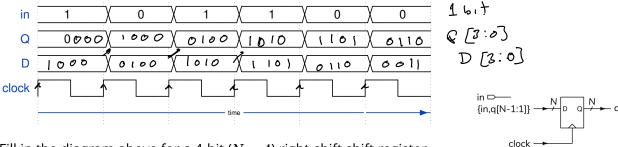

Fill in the diagram above for a 4-bit (N=4) right-shift shift register. Assume the initial value is zero. Which bit is the oldest (first) value in the waveform? Which bit of the shift register holds the oldest value?

**Exercise 3**: Draw a block diagram and write the Verilog for a circuit that sets an output named **detect** high when the sequence of values 1, 1, 0, 1 has appeared on an input named **in** on successive rising edges of the clock.

in

$$E$$

{In,  $q(3:1)$ }  $\frac{4}{4}$   $\frac{4}{9}$   $\frac{$

and module

**Exercise 4**: How could you modify the code so that **digits** is only updated when an **enable** input is asserted?

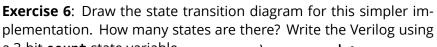

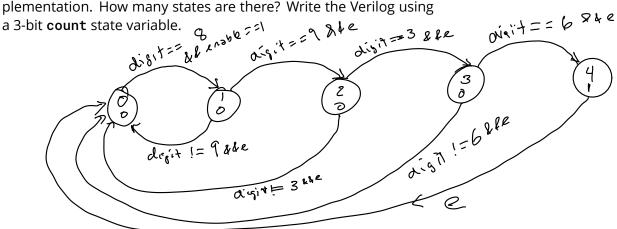

**Exercise 5**: How many states can this state machine have?

e: enable==1 d: digit

assum the combination is

**Exercise 7**: For which states would a **fell** output be asserted? A rose output? Draw the schematic and write the Verilog for this state machine. Assume an input in and a 2-bit register bits that holds the two most recent input values.

fell would be a seerted in state 10.

rose would be a seerted in state 01.

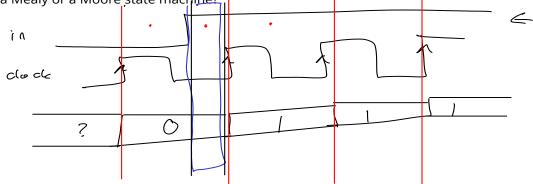

Exercise 8: Can you design an edge detector that uses only one bit? Is this a Mealy or a Moore state machine?

cessing rose = 19 & in ) < Meshy (output is function of input)

**Exercise 9**: Write always\_ff statements that implement these state machines.

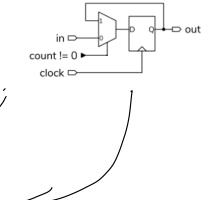

| count | in == out | next  |  |

|-------|-----------|-------|--|

|       | III out   | count |  |

| Х     | 1         | N-1   |  |

| 0     | ×         | N-1   |  |

| n     | 0         | n-1   |  |

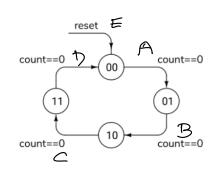

**Exercise 10**: Write the state transition table for this state machine.

| State | Inputts | next State |

|-------|---------|------------|

|       | -       |            |

| state      | reset | count==0 | next<br>State. |               |

|------------|-------|----------|----------------|---------------|

| X          | 1     | X        | 00             | F             |

| (°, (°)    | 0     | 1        | 01             | A             |

| 0 (        | 0     | l        | 10             | B             |

| <b>O</b> ( |       | (        | 111            | 6             |

| 16         |       | l        | 60             | $\mathcal{D}$ |

|            | 10    |          |                |               |