# **Coding Guidelines**

Revision 2: Changed indentation example and wording to emphasize that only always\_ff is the only always allowed.

#### **Mandatory Guidelines**

It's not enough that your design work. Marks will be deducted if you do not follow the guidelines in this section.

#### **File-level Comments**

Include, near the beginning of each Verilog file, comments showing: the file name, a line describing the purpose of the file, the author's name, and the date<sup>1</sup>.

**Why?** These help to quickly identify the source and purpose of your code.

#### **Example:**

```

// lab1.sv

// Display digits of ID on 7-segment display.

// Jane Doe, 2020-9-15

```

## Synchronous Design

Use a single clock. The same clock signal must appear in every always\_ff @(posedge <*clock*>) expression. You can verify this by checking that this is the only signal that appears as a Clock in Processing > Compilation Report > Fitter > Resource Section > Control Signals.

Why? Programmable hardware and design tools assume synchronous (one clock) design. "Computed" clocks, such as in the ripple counter below, are inefficient and difficult to verify.

#### **Example:**

```

// NOT allowed:

always_ff @(posedge clk40) clk20 <= ~clk20 ;

always_ff @(posedge clk20) clk10 <= ~clk10 ;</pre>

```

## **Example:** A report showing multiple clocks:

| 📅 Resource Utilization by Entity |   | Name  | Location    | Fan-Out | Usage |  |

|----------------------------------|---|-------|-------------|---------|-------|--|

| 📰 Delay Chain Summary            | 1 | clk20 | LC_X2_Y4_N4 | 2       | Clock |  |

| EEE Control Signals              | 2 | clk40 | PIN_C2      | 1       | Clock |  |

| Logic and Routing Section        |   |       | _           |         |       |  |

## logic Type

Use the **logic** type for synthesis.

Why? System Verilog's logic can replace both wire and reg. Use it in new code.

## Example:

```

// NOT allowed:

wire clk ;

reg [15:0] cnt ;

// OK:

logic clk ;

logic [15:0] cnt ;

```

# **Consistent Indentation**

A line with **end** should be indented the same as the line with the corresponding **begin**. Each level of indentation should increase by the same amount (no less than 3 and no more than 8). Avoid use of tab characters.

Why? This makes it much easier to find errors.

#### Example:

```

// NOT allowed:

assign cnt_next =

cnt == 0 ? 25 :

cnt - 1 ;

always_ff @(posedge clk)

cnt <= cnt_next ;

// OK:

assign cnt_next =

cnt == 0 ? 25 :

cnt - 1 ;

always_ff @(posedge clk)

cnt <= cnt_next ;</pre>

```

<sup>&</sup>lt;sup>1</sup>Don't confuse this with the information on your report's cover page.

Use always\_ff, not always, always\_comb or always\_latch.

An always\_ff block may only contain one assign-

Don't follow examples that use sequential state-

ments such as if or case within the always\_ff.

Why? This ensures each always\_ff corresponds to

Why? To avoid unintended latches.

**Example:**

ment.

one register.

// NOT allowed:

if ( cnt[15] )

**Example:**

end

// OK:

module ...

```

// NOT allowed:

always @(posedge clk)

cnt <= cnt_next ;

// OK:

always_ff @(posedge clk)

cnt <= cnt_next ;</pre>

```

Single Assignment in always\_ff

always\_ff @(posedge clk) begin

cnt <= cnt + 1'b1 ;

always\_ff @(posedge clk) cnt <=

**Recommended Guidelines**

ever, their use won't be marked.

cnt[15] ? cnt + 1'b1 : cnt ;

```

// set usea to 1 if a>b and a<c or a>=c and a <=b

assign usea = a > b && a < c || a >= c && a <= b;

// D0 describe non-obvious signals and code

module ...

(

input logic reset_n, clk,

input logic [15:0] a, b, c, // filter inputs

...

// is a the median value?

assign usea = a > b && a < c || a >= c && a <= b;</pre>

```

**Use consistent signal naming** to avoid confusion. The following are widely-recognized conventions:

- append \_n to active-low signals

- append \_t to type names

- append \_in to names of input ports that have a corresponding internal signal such as a synchronised or debounced version

- append \_next to the name of a register output to derive the name of the register input

**Use enumerated types for states** to make your code easier to read and to help the synthesizer optimize the design.

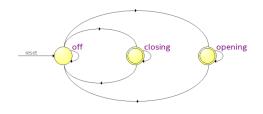

The garage door controller below is an example of a state machine. The synthesizer will choose an appropriate representation for the state variables.

module controller

```

(

input logic clk, pb_in, // clock, pushbutton

input logic top, bottom, // position sensors

output logic up, down

// motor control

) ;

// declare and use an enum state type

typedef enum int unsigned

{ off, opening, closing } state_t ;

state_t state = off, state_next ;

logic pb

debounce db0 ( pb_in, clk, pb ) ;

always @(posedge clk) state <=

state == off && pb ?

( top ? closing : opening )

state == opening && top ? off :

state == closing && bottom ? off :

state ;

assign up = state == opening

assign down = state == closing ;

```

endmodule

```

input logic reset_n, clk, // active-low reset, clk

input logic [15:0] a, b, c,

```

The following guidelines will make your code easier

to understand and help you avoid mistakes. How-

Add comments next to port and signal declarations

should explain why you're doing something rather

than repeating what is obvious from the code. It

should be possible to figure out how your design

and for non-obvious parts of your design.

works just by reading the comments.

// AVOID redundant or missing comments:

These

# **AI Tools**

Generative AI software such as ChatGPT can indent your code, find syntax errors, add comments, and help explain how your design works – or why it doesn't.

However, do not rely on these program to write your code because (1) you will need to write your own code on the quizzes, exams and some labs; and (2) these programs are unlikely to generate code that complies with the course coding guidelines without significant prompting.

As always, credit any work that is not your own. You must cite the source if you submit code generated by AI software.