## **Interfaces**

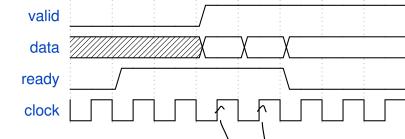

Mark the clock edges where data is transferred.

data transferred here

(only when valid & Mady

both asserted).

## Exercise 2:

asserted).

$$= 8d 196$$

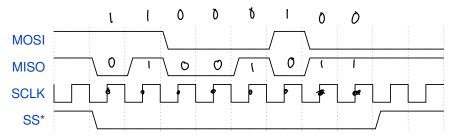

$MISO: (to moster)$

$8'b 01001011$

$= 8'd 75$

8/6/160 0100

MOSI: (to slove)

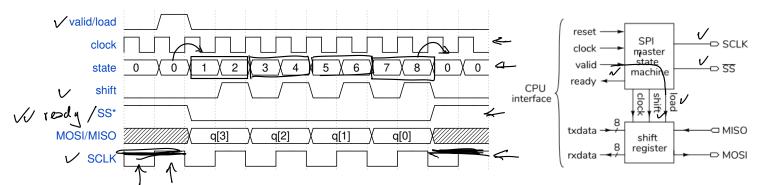

## Exercise 3:

SCLK

Based on the diagram above, write a state transition table for an SPI interface controller that transfers four bits at a time. Include an idle state. In which states are **SCLK** and <del>SS</del> asserted?

| logic state [5:0];                                                         |

|----------------------------------------------------------------------------|

| assign = CLK = ! state[0];<br>assign = state==0;<br>assign   load = valid; |

| assign   00 d = 10/6d;                                                     |

| Soitt - State == 1                                                         |

| assign $Shift = State = 2$ $11state = = 411$                               |

| 25519N resdy = SS_M;                                                       |

| always-ff @(poselyeck)                                                     |

| ctale Vesell                                                               |

| 109 OK AGUA.                                                               |

| state = = 8 ?0:                                                            |

| state +1;                                                                  |