## **Analog Interfaces**

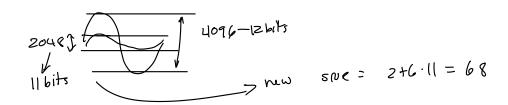

**Exercise 1**: Draw a sine wave and indicate two sets of sampling points at twice the frequency of the sine wave: one that demonstrates aliasing and one that does not. Is it sufficient to sample at twice the highest frequency of the analog signal?

no, must sample at > 2x fnax.

**Exercise 2**: What minimum sampling rate would be required to digitize a 10 kHz square wave if you wanted to include frequency components up to the 7'th harmonic (at 70 kHz)?

**Exercise 3**: A signal with range of  $\pm 3$  V must be quantized so that the quantization error is less than 1 mV. What minimum number of bits of resolution is required?

$$V = 6V$$

$$-3 V = 1092 = 0.001$$

$$V = 6V$$

$$V = 6V$$

$$V = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 1092 = 109$$

**Exercise 4**: A signal-to-noise power ratio of about 48 dB is considered good enough for speech communication. Approximately how many bits per sample are required to obtain this quantization SNR?

**Exercise 5**: When quantizing a full-scale sine wave, what quantization SNR would be achieved with a resolution of 12 bits? What if the signal's voltage range was only half of the full-scale range?

## Exercise 6:

Assume  $V_1$  is set to  $V_{\rm ref}$  and all other inputs are zero (grounded). Find the Thevenim resistance (resistance to ground at  $V_{\rm out}$  with all  $V_i$  shorted) and voltage ( $V_{\rm out}$  with  $V_1 = V_{\rm ref}$ ).

**Exercise 8**: You are designing a PWM DAC and need resolution of 1 mV with a full-scale output of 12 V. How many bits of resolution are required? The pulse frequency is 10 kHz. What is the clock frequency?

quency?

$$\Delta = \frac{\sqrt{2}}{2^n} \qquad N = ?$$

$$\Delta = 0.001$$

$$\Delta = \sqrt{2} \qquad \sqrt{2^n} \qquad \sqrt$$

**Exercise 9**: Rank the different DACs described above in terms of sampling rate relative to clock rate and complexity relative to resolution.

|                 |                                      | Camplexity | or cost          |

|-----------------|--------------------------------------|------------|------------------|

| type            | 5peed                                | ا ما در    | digital          |

| binary weighted | fastest<br>(ts = folock)             | high       | (οω              |

| PWM             | $f_s = \frac{f_{clock}}{z^n}$ slower | (0 W       | medium<br>hisher |

| ∑-△             | ( > some as pwm)                     | lower.     | higher           |

|                 |                                      |            |                  |

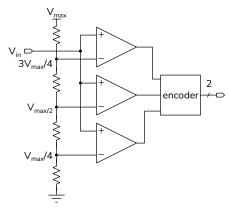

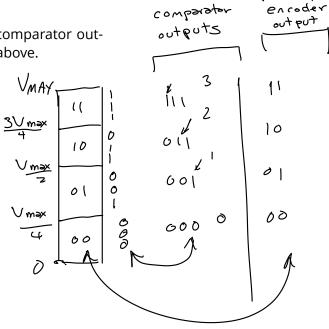

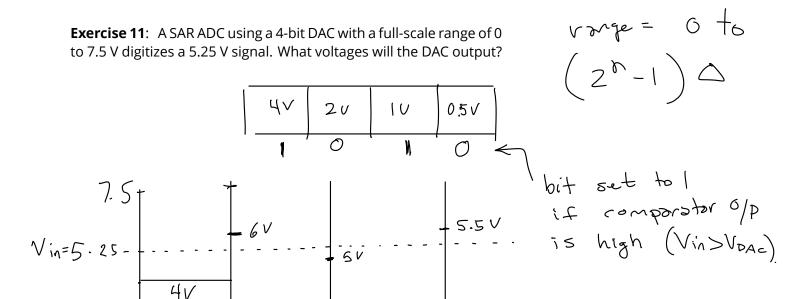

## Exercise 10:

Draw a diagram showing the voltage ranges, the comparator outputs and the binary output for the 4-bit flash ADC above.

**Exercise 12**: What is the slope of an integrator, in V/s, when charging a 100 nF capacitor with 5 V through a  $100~k\Omega$  resistor?

2

ing a 100 nF capacitor with 5 V through a

$$100 \, k\Omega$$

resistor?

$$i = \frac{V}{R} = \frac{50 \, \text{MA}}{100 \, \text{K}} = \frac{50 \, \text{MA}}{0.1 \, \text{M}} = \frac{500 \, \text{M}}{0.1 \, \text{M}} = \frac{5$$

**Exercise 13**: Rank the different ADCs described above in terms of sampling rate relative to clock rate and complexity relative to reso-

complexity

| lustia a   | ı ' '         | <b>\</b>                              |          |

|------------|---------------|---------------------------------------|----------|

| lution.    | fclode/fs     | 8nglog                                | dijital  |

| flash      | 1 (fast)      | high<br>(2h comporators)              | medium   |

| SAR        | ~ (mudium)    | predium<br>(Scouste R-2R)<br>Intwork) | m e dibm |

|            |               | 16W                                   | medium   |

| 2-0        | 2 h (slow)    |                                       | \6W      |

| dual-slope | 2 ~ (slowest) | \6W                                   |          |

|            |               |                                       |          |