## **More Verilog**

**Exercise 1**: Is a signal named **overload** active-high or active-low? Is there an overload if this signal is high? What if the signal was named

**Exercise 2**: Come up with active-high and an active-low names for a signal that is at 3 V when a door is open and 0 V when the door is closed.

**Exercise 3**: If  $\overline{D}$  is a word and  $\overline{D0}$  is low, is the word an even or odd number?

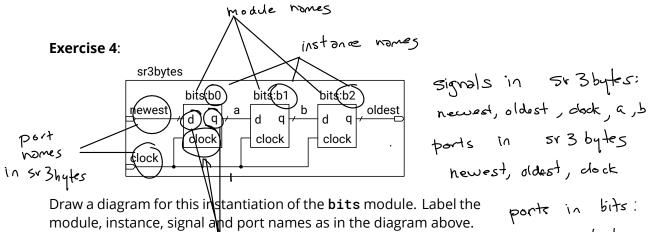

for bits in

$$\overline{D}$$

$L = 1$

$H = 0$

$D_0 = D[0] = Lisin bits g D.$

(our hor means active low not complement).

port names in bits

ports in bits:

## Exercise 5:

```

module sr3bytes

input logic [7:0] newest,

output logic [7:0] oldest, input logic clock

localparam nbits = 8;

module instantiations

logic [nbits-1:0] a, b;

rogge

(bits #(nbits)(b0 )newest/a; clock);

ler does not matter)

.q(b),.clock,.d(a));

(bits) #(.nb(nbits))(b1

(#(.nb(nbits))

(.d(b),.q(oldest),.<u>*)</u>;

endmodule

```

Identify the module instantiation statements in the code above. For each one, what is the instantiated module's name? The instance name?

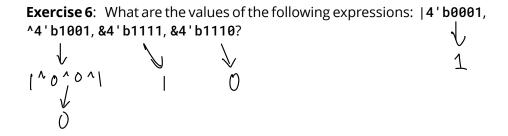

## Exercise 7:

```

// concatenation:

logic [3:0] x = { 2'b00, 2'b11 }; x is 4'b0011

// array literal:

logic [3:0] x[2] = '\{ 4'b0011, 4'b1010 \}; x[0] is 4'b0011, x[1] is 4'b1010 // replication within literal:

logic [3:0] x[2] = '\{2\{ 2'b00, 2'b11 \}\} ;

What are the initial values of \mathbf{x} in the examples above?

should be '{2{ {2'b00,2'b11} }}

initial value of x[0] and x[1] is 4'b0011

```