# Introduction to Digital Design with Verilog HDL

This is a brief introduction to digital circuit design using the System Verilog Hardware Description Language (Verilog HDL). After this lecture you should be able to: define a module with single- and multi-bit <code>logic</code> inputs and outputs; write Verilog numeric literals in binary, decimal and hexadecimal bases; declare arrays and arrays of arrays; evaluate the value and length of expressions containing <code>logic</code> signals, arrays, numeric literals and the operators described below; use <code>assign</code>, <code>always\_ff</code>, and component instantiation statements to create combinational logic, registers, and to instantiate one module in another.

Version 2: Re-ordered and revised sections on Arrays of Arrays and Statements.

#### Introduction

Hardware Description Languages (HDLs) are used to design digital circuits. In this course we will use System Verilog, the modern version of the Verilog HDL, rather than the other popular HDL, VHDL.

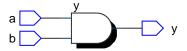

Let's start with a simple example – a circuit called an ex1 that has one output (y) that is the logical AND of two input signals (a and b). The file ex1.sv contains the following Verilog description:

Some observations on Verilog syntax:

- Everything following // on a line is a comment and is ignored.

- Module and signal names can contain letters, digits, underscores (\_), and dollar signs (\$). The first character of an identifier must be a letter or an underscore. They cannot be the same as certain reserved words (e.g. module).

- Verilog is case-sensitive: a and A would be different signals.

- Statements can be split across any number of lines. A semicolon ends each statement.

Capitalisation and indentation styles vary. In this course you will need to follow the coding style guide available on the course website.

The module definition begins by defining the input and output signals for the device being designed.

The body of the module contains one or more statements, each of which operates at the same time – *concurrently*. This is the key difference between HDLs and programming languages – HDLs allows us to define concurrent behaviour.

The single statement in this example is a signal assignment that assigns the value of an expression to the output signal **y**. Expressions involving **logic** signals can use the logical operators described below including & (AND), | (OR), and ^ (XOR). Parentheses can be used to order the operations.

From this Verilog description a program called a logic synthesizer (e.g. Intel's Quartus) can generate a circuit that has the required functionality. In this case it's not too surprising that the result is the following circuit:

If you're familiar with the C programming language you'll note that Verilog uses similar syntax.

Exercise 1: What changes would result in a 3-input OR gate?

Exercise 2: What schematic would you expect if the statement was assign y = ( a ^ b ) | c ;?

### **Syntax**

#### **Reserved Words**

System Verilog has about 250 reserved words (including many common ones such as time, wait, disable, reg, table, input, ...) that may not be used as module or signal names. Doing so will give a syntax error when you try to compile ("synthesize") the description. An editor with syntax highlighting will help you identify and avoid using reserved words.

# logic values

Verilog's logic signals can have four values: 0 (false or low), 1 (true or high), z (high impedance) and x (undefined).

#### **Numeric Literals**

Numeric literals, often called "constants," are written as a sequence of up to three parts: the number of bits; the letter 'b for binary, 'h for hex, or 'd for decimal; and the value in the specified base. The default width is 32 and the default base is decimal. Underscores (\_) may be used within the value to improve readability.

Exercise 3: What are the lengths and values, in decimal, of the following: 4'b1001? 5'd3? 6'h0\_a? 3?

The notations '0 and '1 are convenient abbreviations for a literal that is all-zeros or all-ones.

### **Arrays**

An array is a collection of **logic** signals whose elements can be selected by a value called the index. Arrays often represent numerical values in binary form.

For example, the declaration logic [3:0] a; specifies an array named a with a 'width' of four bits.

In this example the bit indices are declared as going from 3 down to 0. If the bit values are written out and represent a binary number then a[3], the leftmost bit, is the most significant bit. a[0] is the rightmost (least significant) bit.

Exercise 4: If the signal i is declared as logic [2:0] i;, what is the 'width' of i? If i has the value 6 (decimal), what is the value of i[2]? Of i[0]?

#### **Expressions**

Logic circuits in HDLs are defined using expressions as shown above. These include operators that operate on "operands" – numeric literals ("constants"), logic signals and arrays of these. Operators with higher "precedence" are applied before those of lower precedence. If two operators are of equal precedence they are applied from left to right. Operators can change the number of bits in an expression (the "length") as they're applied. Values are padded with zeros on the left when necessary.

### **Operators**

The following describe some useful Verilog operators in order of decreasing precedence.

**Slices** A range of bits in an array (a "slice") can be extracted using a range of indices in brackets ([first:last]) after the array name. The bit order cannot be reversed. The length is the number of bits in the slice.

**Negation** Logical negation (!) is zero (0) when applied to a non-zero operand and one (1) otherwise. The length is 1 bit.

Bitwise negation (~) inverts the value of each bit. The length is the width of the operand.

**Arithmetic** Multiplication (\*), division (/), addition (+) and subtraction (-) can be applied to arrays. The first two have higher precedence. The length is the largest of the two operands' lengths.

**Shift** Right- (>>) and left-shift (<<) operators shift the bits in the array operand on the left by the value on the right. The length is the length of the left operand.

**Comparison** When arithmetic comparison operators (<, >, <=, >=, !=) are applied to arrays the result is 1 if the comparison is true and 0 otherwise. The length is 1 bit.

**Bitwise Logical** Bitwise logical operators (&, |, ^) are applied to the corresponding bits in two operands. The length is the largest of the two operands' lengths.

**Logical** The logical AND operator (&&) has value 1 if both operands are non-zero. The logical OR operator (||) has value 1 if either operand is non-zero. The length is 1 bit.

Exercise 5: An array declared as logic [15:0] n; and has the value 16'h1234. What are the values and lengths of the following expressions?  $n[15:13]!n \sim n[3:0]n > 4$   $n + 1'b1n[7:0] - n[3:0]n > = 16'h1234n ^ '1 n$  && !n n \* (!n + 1'b1)

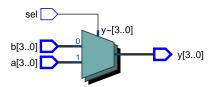

**Conditional Operator** Verilog's conditional operator is a concise syntax for describing a two-way multiplexer. The operator consists of three

parts: the condition, the true value and false value. The result of the operator is the true value if the condition is non-zero, or the false value otherwise. The length is the largest of the true and false value lengths. For example:

assign y = sel ? a : b

$$\Leftrightarrow$$

$b \to 0$

sets y to a when sel is non-zero and sets y to b when sel is zero.

Exercise 6: What are the length and value of the expression: 3 ? 16'd10: 8'h20? If x has the value 0, what is the value of the expression: x ? 1'b1: 1'b0? If x has the value -1?

The following example implements a multiplexer that selects from one of two 4-bit inputs:

which results in:

Conditional operators can be used to concisely describe trees of multiplexers. In the absence of parentheses a sequence of conditional operators is evaluated from left to right.

**Exercise 7:** Draw the schematics corresponding to:

```

y = a ? ( b ? s1 : s2 ) : ( c ? s3 : s4 );

y = a ? s1 : b ? s2 : c ? s3 : s4;

```

**Concatenation** The concatenation operator ({,}) combines expressions into a longer value. The length is the sum of the lengths.

Exercise 8: Use slicing and concatenation to compute the byte-swapped value of an array n declared as logic [15:0] n.

Exercise 9: If n has the value 16'h1234, what is the value and length of:  $\{n[7:0], n[15:8], 4'b1111\}$ ?

**Exercise 10:** Use concatenation to shift **n** left by two bits.

Concatenations of variables can also be used on the left hand side of an assignment.

**Exercise 11:** Use concatenation to assign the high-order byte of **n** to **a** and the low-order byte to **b**.

#### **Statements**

The assign, always\_ff, and component instantiation statements create logic. Statement order does not matter since the hardware created by each statement operates simultaneously (*concurrently*).

# assign

The **assign** statement continuously assigns the value of the expression on the right-hand side (RHS) to the signal on the left-hand side (LHS). The most significant bits are dropped if the RHS is wider than the LHS. For example, this module:

results in this logic:

**Exercise 12:** Some software warns about truncation. How could you re-write the **assign** statement to avoid such a warning?

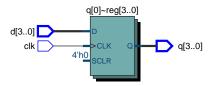

#### always\_ff

The always\_ff statement creates flip-flops and registers. For example, the following Verilog:

#### endmodule

synthesizes a 4-bit D flip-flop that transfers the **d** input to the **q** output on the rising (positive) edge of **clk**:

Note the use of "non-blocking assignment" (<=) in always\_ff statements. As with the blocking assignment (=), the leftmost bits are dropped if the RHS is wider than the LHS.

**Exercise 13:** Write an always\_ff statement that toggles (inverts) its output on each rising edge of the clock.

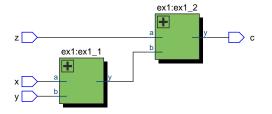

# **Component Instantiation**

Module instantiation inserts a copy of ("instantiates") one module into another and connects signals to the instantiated module's input and output ports. For example, the module:

endmodule

creates a 3-input AND gate by instantiating two instances of the ex1 module defined earlier:

**Exercise 14:** Identify the following in the diagram above: component names, component "instance names," component port names, module port names. Label the signal t in the schematic.

**Exercise 15:** Rewrite the **ex60** module using operators. Which version – "structural" or "behavioural" – is easier to understand?

# **Arrays of Arrays**

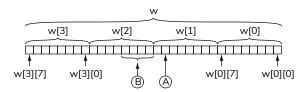

We can also declare arrays of arrays. For example, logic[3:0][7:0] w; declares w as an array of four arrays of eight bits. A single index selects one of the bytes, two indices selects a byte as well as a bit from that byte:

**Exercise 16:** How would you specify the bit marked A in the diagram above? The bits marked B? The least-significant byte?

# **Lookup Tables**

Arrays of arrays can serve as look-up tables. In this example:

```

// 0 1 2 3 4 5 6 7

logic [0:7][1:0] sumofbits = '{0,1,1,2,1,2,2,3} ;

logic [2:0] n ;

logic [1:0] b ;

...

assign b = sumofbits[n] ;

```

**sumofbits** is a lookup table initialized<sup>1</sup> with values that are the sum of the bits in the binary representation of each number between 0 and 7. For example, the binary representation of the number 5 is 101 and the sum of these bits is 2. So we've set **sumofbits[5]** to 2.

Note that the first dimension of the lookup table is declared with *increasing* index values.

To find the sum of the bits in a number we use that number as the index into the array. The value in the array at that index is the desired result. Thus the expression <code>sumofbits[n]</code> gives the number of '1' bits in <code>n</code>.

**Exercise 17:** Define a Verilog lookup table named isprime that can be used to determine if a value between 0 and 7 is a prime number or not. The result should be 1 if the value is a prime or else 2. *Hint: The primes are 2, 3, 5 and 7.*

**Exercise 18:** Write an expression giving the same result. Draw the corresponding block diagram.

<sup>&</sup>lt;sup>1</sup>The contents set by the logic synthesizer.