## **Introduction to Digital Design with Verilog HDL**

**Exercise 1**: What changes would result in a 3-input OR gate?

CHambaate

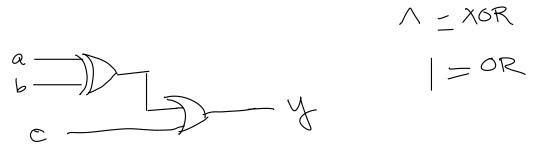

**Exercise 2**: What schematic would you expect if the statement was assign  $y = (a \hat{b}) | c$ ;?

Exercise 3: What are the lengths and values, in decimal, of the following: 4'b1001, 5'd3,  $6'h0_a$ , 3?1ength 9

5'd3  $\Rightarrow$  5

6'h0\_a  $\Rightarrow$  6

10

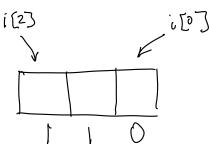

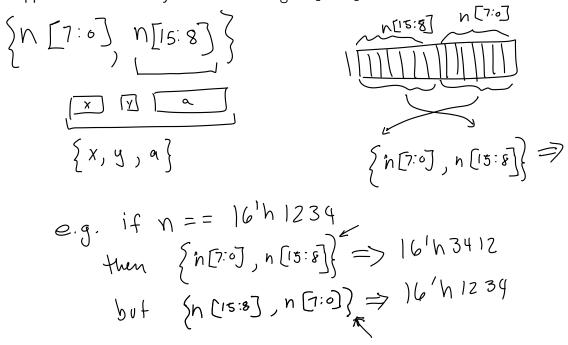

**Exercise 4**: If the signal i is declared as logic [2:0] i;, what is the 'width' of i? If i has the value 6 (decimal), what is the value of i[2]? Of i[0]?

**Exercise 5**: An array declared as logic [15:0] n; and has the value 16 'h1234. 0001 0010 0011 3:0 00 What are the values and lengths of the following expressions? n[15:13] 3,800 0 1, P 0 !n ~n[3:0] 4 b | 6 l \ 16'b 0000 000 0010 0011 0100 or 16 h 0123 n>>4  $n + 1'b1 = \frac{1}{6} \cdot h \cdot 1235$  $81(8'h34-4'h4) \Rightarrow 8'h30$ n[7:0] - n[3:0] 161 n >= 16'h1234000/ 0010 0011 0100 m 16'h fff 16'h1234 88 1'b0 => 1'b0

$1'b1 * 16'h1234 \Rightarrow 16'h1234$

1'60 + 1'61 => 1'61

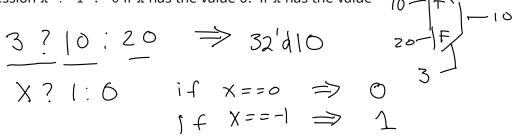

**Exercise 6**: What is the value of the expression 3? 10 : 20? Of the expression x? 1 : 0 if x has the value 0? If x has the value -1?

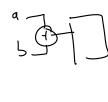

**Exercise 7**: Draw the schematics corresponding to:

assign

$$y = a$$

?  $s1 : b ? s2 : c ? s3 : s4;$

**Exercise 8**: Use slicing and concatenation to compute the byteswapped value of an array n declared as logic [15:0] n.

**Exercise 9**: If n has the value 16'h1234, what is the value and length of  $\{n[7:0], n[15:8], 4$ 'b1111 $\}$ ?

$${8'h34, 8'h12, 4'hf} \Rightarrow 20'h3412f$$

**Exercise 10**: Use concatenation to shift n left by two bits.

**Exercise 11**: Use concatenation to assign the high-order byte of  ${\tt n}$  to a and the low-order byte to  ${\tt b}$ .

logic [7:0] a,b;

assign

$$\{a,b\} = n$$

;

$n = \{a,b\}$  also possible

assign

$$y = a + 2 ;$$

Some software warns about truncation. How could you re-write the assign statement to avoid such a warning?

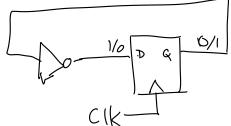

**Exercise 13**: Write an always\_ff statement that toggles (inverts) its output on each rising edge of the clock.

alway-ff @(posed ge clk) 9 <= ~9

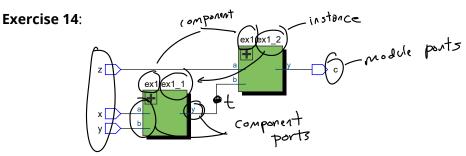

Identify the following in the diagram above: component names, component "instance names," component port names, module port names. Label the signal t in the schematic.

**Exercise 15**: Rewrite the ex60 module using operators. Which version – "structural" or "behavioural" – is easier to understand?

module ex60 (input logic x, y, z, output logic c);

logic t;

ex1 ex1\_1(x,y,t);

ex1 ex1\_2(z,t,c);

endmodule

"Stro C toval"

Dehaviouval"

A ssier for homons

to understand

to understand

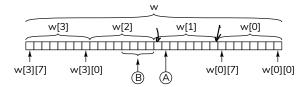

## Exercise 16:

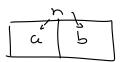

How would you specify the bit marked A in the diagram above?

The bits marked B?  $\omega$  [2] [3:0]

**Exercise 17**: Define a Verilog lookup table named isprime that can be used to determine if a value between 0 and 7 is a prime number or not. The result should be 1 if the value is a prime or else 2. *Hint:*

| o | z 3 4 5 6 7 | o | c To:  $\frac{1}{2}$  [1:0] is prime =  $\frac{1}{2}$  [2, 2, 1, 1, 2, 1, 2, 1);