## **Memory System Design**

**Exercise 1**: Is  $t_{AW}$  a requirement or a guaranteed specification for this memory? How about the  $t_{AA}$ ?

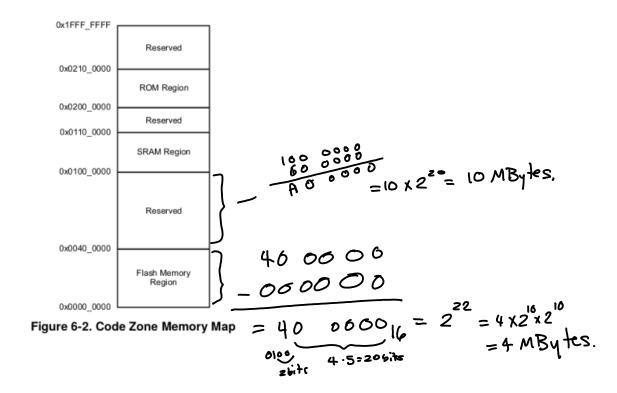

**Exercise 3**: How large are the two lowest memory regions in the memory map above?

**Exercise 4**: If a CPU has a 32-bit address bus, how many bytes can it address? What range of addresses would correspond to the first 64 k Bytes? If this range of memory was to be implemented with 32-bit words, how many address bits would be required to select a byte within each word? How many bits would be required to select a 32-bit word within the 64 k range? How many bits are not directly connected to the memory ICs? What would they be used for?

32 bits => 232 bytes can be addressed

64kBytes = 0 to (64 ×1024 -1)

= 0 to 65535

32 bits is

$$\frac{32}{8} = 4$$

bytes

need  $\log_2 4 = 2$  bits to select one byte

from each 32-bit word

64kBytes =  $\frac{64kB}{4}$  bytes/word

$\log_2 |\log k = 14$  bits needed to select

a word

The least-significant 2 bits are not

connected to the ICs:

They are used to select a

byte from each 32-bit word.

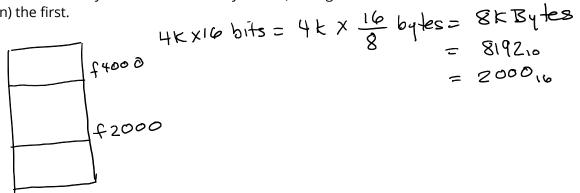

**Exercise 5**: A 4k×16 memory is to be used in a system with a 20bit address bus. This memory is to respond to addresses starting at 20'hf2000. Draw the memory map. Assuming the address signal is defined as logic [19:0] a; and the chip-select as logic cs0; write the Verilog that would implement the chip-select signals csO. Write the expression for a second chip-select, cs1 that would enable a second 8 kBytes bank immediately above (at a higher address than) the first.

assign  $CS\phi = a > = 20$  hf2000 && a < 26 hf4000, assign cs1 = a>=20'hf4000 && a<z'hf6000; or, more simply, note that!

\$2000 is 1111 0010 − 1206− f3fff is 11110011 £4000 is 11110100 11 f5ff is

written os: so this could also be

assign  $cs \phi = a[19:13] = 7'b1111_001j$ assign cs1 = q[19:15] = 7/b 1111\_010;