### MODELING AND OPTIMIZATION OF SPECULATIVE THREADS

by

Tor M. Aamodt

A thesis submitted in conformity with the requirements for the degree of Doctor of Philosophy, Department of Electrical and Computer Engineering, University of Toronto

Copyright © 2006 Tor M. Aamodt

#### Abstract

#### MODELING AND OPTIMIZATION OF SPECULATIVE THREADS

Tor M. Aamodt Doctor of Philosophy Department of Electrical and Computer Engineering University of Toronto 2006

This dissertation proposes a framework for modeling the control flow behavior of a program and the application of this framework to the optimization of speculative threads used for instruction and data prefetch. A novel form of helper threading, *prescient instruction prefetch*, is introduced in which helper threads are initiated when the main thread encounters a spawn point and prefetch instructions starting at a distant target point. The target identifies a code region tending to incur I-cache misses that the main thread is likely to execute soon, even though intervening control flow may be unpredictable. The framework is also applied to the compile time optimization of *simple p-threads*, which improve performance by reducing data cache misses.

The optimization of speculative threads is enabled by modeling program behavior as a Markov chain based on profile statistics. Execution paths are considered stochastic outcomes, and program behavior is summarized via path expression mappings. Mappings for computing reaching, and posteriori probability; path length mean, and variance; and expected path footprint are presented. These are used with Tarjan's fast path algorithm to efficiently estimate the benefit of spawn-target pair selections.

Two implementation techniques for prescient instruction prefetch—direct pre-execution, and finite state machine recall—are proposed and evaluated. Further, a hardware mechanism for reducing resource contention in direct pre-execution called the YAT-bit is proposed and evaluated. Finally, a hardware mechanism, called the safe-store, for enabling the inclusion of stores in helper threads is evaluated and extended. Average speedups of 10.0% to 22% (depending upon memory latency) on a set of SPEC CPU 2000 benchmarks that suffer significant I-cache misses are shown on a research Itanium® SMT processor with next line and streaming I-prefetch mechanisms that incurs latencies representative of next generation processors. Prescient instruction prefetch is found to be competitive against even the most aggressive research hardware instruction prefetch technique: fetch directed instruction prefetch.

The application of the modeling framework to data prefetch helper threads yields results

comparable with simulation based helper thread optimization techniques while remaining amenable to implementation within an optimizing compiler.

### Acknowledgements

I would like to thank my thesis supervisor Professor Paul Chow for his guidance over the past several years and for encouraging me to pursue my own directions in my research. I am very thankful to the members of my Ph.D. thesis committee, Professor Todd C. Mowry, Professor Andreas Moshovos, Professor Greg Steffan, and Professor Ian F. Blake for their invaluable feedback on this dissertation.

I would also like to thank Dr. Hong Wang and Dr. John P. Shen for the opportunity to work with them and other members of Intel Research during the initial phase of this research at Intel Corporation's Microarchitecture Research Lab in Santa Clara California. Other individuals from Intel Santa Clara that contributed to a collegial atmosphere during my internship include Perry H. Wang, Shih-Wei Steve Liao, Murali Annavaram, Ed Grochowski, Trung A. Diep, Ryan Rakvic, Mauricio Breternitz Jr., and Gerolf Hoffehner. Similarly, Srikanth Srinivasan, Jared Stark, Konrad Lai, and Shih-Lien Lu from Intel MRL-uAL in Oregon; Edward (Ned) Brekelbaum from Intel MRL-uAL in Austin; Pedro Marcuello and Antonio Gonzalez from Intel Barcelona; and Per Hammarlund from Intel DPG in Oregon made working at Intel an enjoyable and educational experience.

My peers in the Department of Electrical and Computer Engineering at the University of Toronto have made the time spent in graduate school a pleasure. In particular, I would like to thank Amy Wang, Andy Ye, David Tam, Guy Lemieux, Imad A. Ferzli, Jason Anderson, Kostas Pagiamtzis, Lesley Shannon, Marcus van Ierssel, Mark Stoodley, Mathew Zaleski, Mazen Saghir, Navid Azizi, Patrick Doyle, Paul Kundarewich, Peter Jamieson, Reza Azimi, Sirish Raj Pande, Valavan Manohararajah, Vincent Charles Gaudet, and Warren Gross. Since I've been at UofT so long, I might was well apologize in advance to those whose names I've surely missed! Thanks also to Eugenia Distefano and Peter Pereira for their always lightning fast IT support.

I've also enjoyed discussions with various people at computer architecture conferences including Amir Roth, Craig B. Zilles, Jamison D. Collins, Guri Sohi, and Dean M. Tullsen.

My family deserves a very special thanks. Foremost, my wife Dayna has been a constant source of encouragement and inspiration. My parents and in-laws have been very supportive of my desire to obtain my doctorate and I am thankful. I am thankful for my mother's consistent encouragement. My father's study of electrical engineering while I was young, combined with the TRS 80 Color Computer he got me soon after he graduated, surely played a part in the subsequent path of my academic studies. My mother-in-law and father-in-law have helped my wife and myself out in immeasurable number of ways over the past several years and I am very grateful. My wife's grandmother (Bubby) and my grandmother (Nana) will be happy to know I can finally relax on my weekends as would my wife's dearly departed grandfather (Zaidy). My grandfather (Grandpa) implanted the goal of pursuing a Ph.D. from a very early age and even suggested computer engineering back in the days of the Intel 486 (when I was thinking more of becoming an architect that designs buildings rather than computers—I eventually discovered the wisdom of his suggestion while pursuing my undergraduate degree in the Engineering Science program at UofT and thinking hard about what I wanted to study in graduate school).

Financial support for this research was provided by the Natural Sciences and Engineering Research Council (NSERC) of Canada, and by an internship with Intel Corporation.

## Contents

| 1        | Introduction                     |                |                                                        | 1  |  |

|----------|----------------------------------|----------------|--------------------------------------------------------|----|--|

|          | 1.1                              | Motiva         | ation                                                  | 2  |  |

|          | 1.2                              | 1.2 Background |                                                        |    |  |

|          |                                  | 1.2.1          | Fundamental Microarchitecture and Program Behavior     | 5  |  |

|          |                                  | 1.2.2          | Multithreading Microarchitectures and Program Behavior | 9  |  |

|          |                                  | 1.2.3          | Helper Threads                                         | 12 |  |

|          |                                  | 1.2.4          | Program Behavior Exploited by Helper Threads           | 14 |  |

|          | 1.3                              | Disser         | tation Summary                                         | 15 |  |

|          |                                  | 1.3.1          | Research Goals                                         | 15 |  |

|          |                                  | 1.3.2          | Methodology                                            | 16 |  |

|          |                                  | 1.3.3          | Contributions                                          | 16 |  |

|          |                                  | 1.3.4          | Organization                                           | 17 |  |

| <b>2</b> | Modeling Framework 1             |                |                                                        |    |  |

|          | 2.1                              | Gener          | c Properties of Speculative Threads                    | 20 |  |

|          | 2.2                              | Analy          | tical Framework                                        | 24 |  |

|          |                                  | 2.2.1          | A Statistical Model of Program Execution               | 24 |  |

|          |                                  | 2.2.2          | Computing Statistics via Path Expressions              | 25 |  |

|          | 2.3                              | Frame          | work Accuracy                                          | 35 |  |

|          | 2.4                              | Summ           | ary and Contributions                                  | 37 |  |

| 3        | Prescient Instruction Prefetch 3 |                |                                                        |    |  |

|          | 3.1                              | Introd         | $\operatorname{uction}$                                | 39 |  |

|          | 3.2                              | Optim          | ization Algorithm                                      | 43 |  |

|          |                                  | 3.2.1          | Analysis: Single Helper Thread Instance                | 44 |  |

|          |                                  | 3.2.2          | Optimization via Greedy Spawn-Target Pair Selection    | 46 |  |

|   | 3.3        | Simulat                                                                                                 | tion Results                                                                                  | 49                                                                                                                                             |

|---|------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|   |            | 3.3.1                                                                                                   | Methodology                                                                                   | 49                                                                                                                                             |

|   |            | 3.3.2                                                                                                   | Results                                                                                       | 51                                                                                                                                             |

|   | 3.4        | Summa                                                                                                   | xy                                                                                            | 54                                                                                                                                             |

| 4 | Har        | dware S                                                                                                 | Support for Prescient Instruction Prefetch                                                    | 55                                                                                                                                             |

|   | 4.1        | Direct 1                                                                                                | pre-execution                                                                                 | 56                                                                                                                                             |

|   |            | 4.1.1                                                                                                   | Requirements for direct pre-execution                                                         | 56                                                                                                                                             |

|   |            | 4.1.2                                                                                                   | Hardware support                                                                              | 59                                                                                                                                             |

|   | 4.2        | Exploit                                                                                                 | ing predictability                                                                            | 63                                                                                                                                             |

|   |            | 4.2.1                                                                                                   | Finite state machine recall                                                                   | 64                                                                                                                                             |

|   |            | 4.2.2                                                                                                   | FSM and t-slice construction                                                                  | 66                                                                                                                                             |

|   | 4.3        | Perform                                                                                                 | nance evaluation                                                                              | 67                                                                                                                                             |

|   |            | 4.3.1                                                                                                   | Processor model                                                                               | 67                                                                                                                                             |

|   |            | 4.3.2                                                                                                   | Prescient instruction prefetch models                                                         | 67                                                                                                                                             |

|   |            | 4.3.3                                                                                                   | Simulation methodology and workloads                                                          | 69                                                                                                                                             |

|   |            | 4.3.4                                                                                                   | Performance evaluation                                                                        | 71                                                                                                                                             |

|   | 4.4        | Summa                                                                                                   | ry                                                                                            | 74                                                                                                                                             |

| 5 | Opt        | imizati                                                                                                 | on of Data Prefetch Helper Threads                                                            | 77                                                                                                                                             |

|   | 5.1        | Optimization Using Trace Data                                                                           |                                                                                               |                                                                                                                                                |

|   |            |                                                                                                         | zation Using Trace Data                                                                       | 78                                                                                                                                             |

|   |            | 5.1.1                                                                                                   | -                                                                                             | 78<br>79                                                                                                                                       |

|   |            |                                                                                                         | Motivation                                                                                    |                                                                                                                                                |

|   | 5.2        | 5.1.2                                                                                                   | Motivation                                                                                    | 79<br>79                                                                                                                                       |

|   | 5.2        | 5.1.2<br>Optimiz                                                                                        | Motivation                                                                                    | 79<br>79<br>84                                                                                                                                 |

|   | 5.2        | 5.1.2<br>Optimiz<br>5.2.1                                                                               | Motivation                                                                                    | 79<br>79<br>84                                                                                                                                 |

|   | 5.2        | 5.1.2<br>Optimiz<br>5.2.1<br>5.2.2                                                                      | Motivation                                                                                    | 79<br>79<br>84<br>84                                                                                                                           |

|   | 5.2<br>5.3 | 5.1.2<br>Optimiz<br>5.2.1<br>5.2.2<br>5.2.3                                                             | Motivation                                                                                    | 79<br>79<br>84<br>84<br>87                                                                                                                     |

|   |            | 5.1.2<br>Optimiz<br>5.2.1<br>5.2.2<br>5.2.3<br>Improve                                                  | Motivation                                                                                    | 79<br>79<br>84<br>84<br>87<br>88                                                                                                               |

|   | 5.3        | 5.1.2<br>Optimiz<br>5.2.1<br>5.2.2<br>5.2.3<br>Improve<br>Experim                                       | Motivation                                                                                    | <ol> <li>79</li> <li>79</li> <li>84</li> <li>84</li> <li>87</li> <li>88</li> <li>92</li> </ol>                                                 |

|   | 5.3        | 5.1.2<br>Optimiz<br>5.2.1<br>5.2.2<br>5.2.3<br>Improve<br>Experim<br>5.4.1                              | Motivation                                                                                    | <ol> <li>79</li> <li>79</li> <li>84</li> <li>84</li> <li>87</li> <li>88</li> <li>92</li> <li>94</li> </ol>                                     |

|   | 5.3        | 5.1.2<br>Optimiz<br>5.2.1<br>5.2.2<br>5.2.3<br>Improve<br>Experim<br>5.4.1<br>5.4.2                     | Motivation                                                                                    | <ol> <li>79</li> <li>79</li> <li>84</li> <li>84</li> <li>87</li> <li>88</li> <li>92</li> <li>94</li> <li>95</li> <li>97</li> </ol>             |

|   | 5.3        | 5.1.2<br>Optimiz<br>5.2.1<br>5.2.2<br>5.2.3<br>Improv<br>5.4.1<br>5.4.2<br>5.4.3                        | Motivation                                                                                    | <ol> <li>79</li> <li>79</li> <li>84</li> <li>84</li> <li>87</li> <li>88</li> <li>92</li> <li>94</li> <li>95</li> <li>97</li> <li>99</li> </ol> |

|   | 5.3<br>5.4 | 5.1.2<br>Optimiz<br>5.2.1<br>5.2.2<br>5.2.3<br>Improve<br>Experin<br>5.4.1<br>5.4.2<br>5.4.3<br>Sources | Motivation       Aggregate Advantage         zation using Static Slicing and Path Expressions | <ol> <li>79</li> <li>79</li> <li>84</li> <li>87</li> <li>88</li> <li>92</li> <li>94</li> <li>95</li> <li>97</li> <li>99</li> <li>01</li> </ol> |

|                                          |                | 5.5.3   | Branch Outcome Correlation                       | . 104 |

|------------------------------------------|----------------|---------|--------------------------------------------------|-------|

|                                          |                | 5.5.4   | Spatial Locality / Loss of Temporal Locality     | . 105 |

|                                          |                | 5.5.5   | Resource Constraints                             | . 105 |

|                                          | 5.6            | Summ    | nary                                             | . 106 |

| 6                                        | $\mathbf{Rel}$ | ated V  | Vork                                             | 113   |

| 6.1 Modeling Techniques and Applications |                |         | ling Techniques and Applications                 | . 113 |

|                                          |                | 6.1.1   | Modeling for Program Optimization                | . 113 |

|                                          |                | 6.1.2   | Modeling to Predict Microprocessor Performance   | . 114 |

|                                          |                | 6.1.3   | Sampling                                         | . 115 |

|                                          | 6.2            | Prefet  | ching                                            | . 116 |

|                                          | 6.3            | Specu   | lative Multithreading                            | . 116 |

|                                          | 6.4            | Helpe   | r Threads                                        | . 117 |

| 7                                        | Cor            | nclusio | ns and Future Work                               | 121   |

|                                          | 7.1            | Summ    | ary and Conclusions                              | . 121 |

|                                          | 7.2            | Contr   | ibutions                                         | . 123 |

|                                          | 7.3            | Future  | e Work                                           | . 124 |

|                                          |                | 7.3.1   | Speculative Multithreading and Dependence Chains | . 124 |

|                                          |                | 7.3.2   | Compiler Optimizations                           | . 124 |

|                                          |                | 7.3.3   | Optimization of Chaining Helper Threads          | . 125 |

|                                          |                | 7.3.4   | Equivalent Linked Data Structure Traversals      | . 125 |

| $\mathbf{A}$                             | Pat            | h Leng  | gth Variance Operators                           | 127   |

|                                          | A.1            | Union   | Operator                                         | . 127 |

|                                          | A.2            | Closu   | re Operator                                      | . 128 |

| B                                        | ibliog         | graphy  |                                                  | 131   |

# List of Figures

| 1.1 | Superscalar processor                                                                        | 6  |

|-----|----------------------------------------------------------------------------------------------|----|

| 1.2 | Superscalar processor with simultaneous multithreading support $\ldots \ldots \ldots \ldots$ | 9  |

| 1.3 | Data prefetch helper threads                                                                 | 13 |

| 2.1 | Modeling and Optimization Framework                                                          | 19 |

| 2.2 | Speculative Threads                                                                          | 20 |

| 2.3 | Example: Optimizing an Instruction Prefetch Helper Thread                                    | 22 |

| 2.4 | Abstraction of Program Execution Paths                                                       | 26 |

| 2.5 | Analysis of the closure operator.                                                            | 31 |

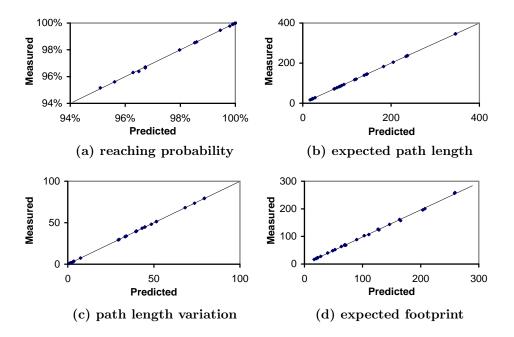

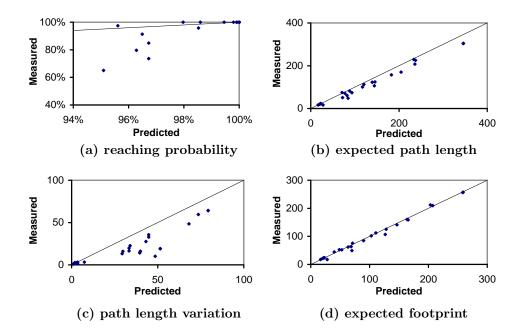

| 2.6 | Monte Carlo Simulation vs. Framework                                                         | 36 |

| 2.7 | Execution Trace Statistics vs. Framework                                                     | 37 |

| 2.8 | Example of inaccuracy due to first-order Markov model approximation                          | 38 |

| 3.1 | Prescient Instruction Prefetch.                                                              | 40 |

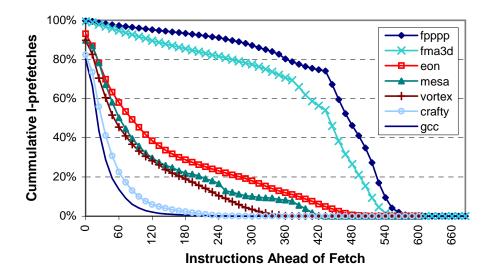

| 3.2 | Prefetch distribution for a branch predictor guided I-prefetch mechanism                     | 42 |

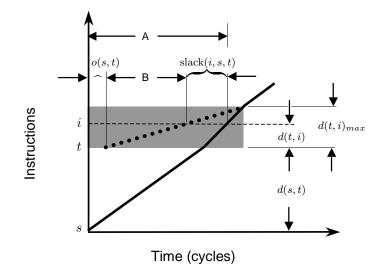

| 3.3 | Illustration of Equations 3.1 and 3.2                                                        | 43 |

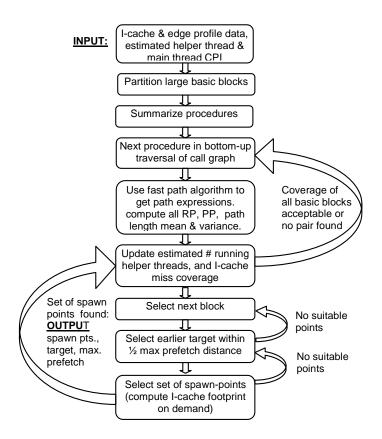

| 3.4 | Spawn-Target Selection Algorithm                                                             | 46 |

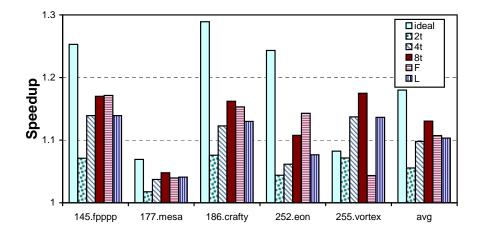

| 3.5 | Limit study performance.                                                                     | 52 |

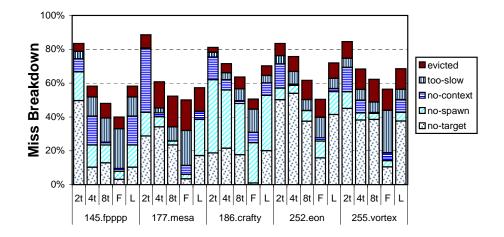

| 3.6 | Breakdown of remaining I-cache misses relative to baseline                                   | 53 |

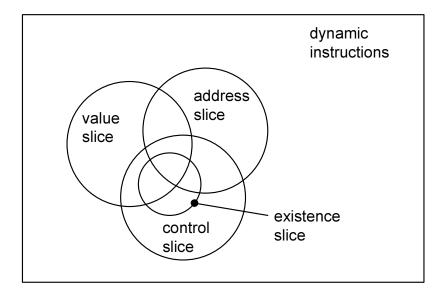

| 4.1 | Venn diagram showing relationships of various dynamic slice classifications                  | 57 |

| 4.2 | Postfix pre-execution and filtering                                                          | 58 |

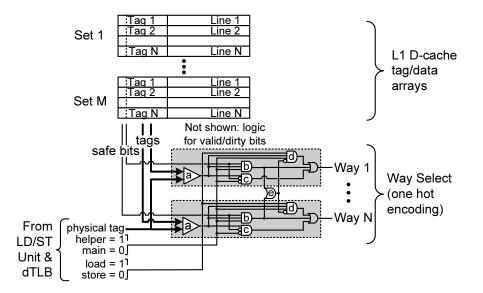

| 4.3 | Safe-store way-selection logic                                                               | 60 |

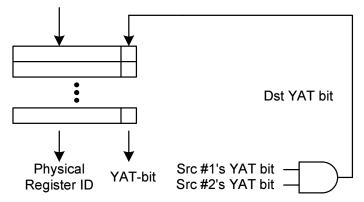

| 4.4 | YAT-bit rename logic                                                                         | 61 |

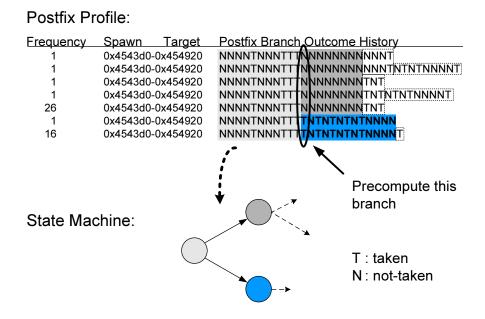

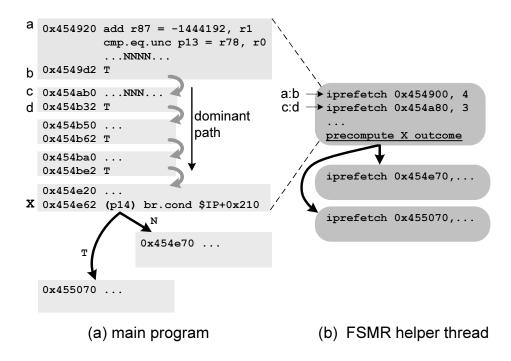

| 4.5 | Postfix profile & FSM construction                                                           | 64 |

| 4.6 | Finite state machine recall example                                                          | 65 |

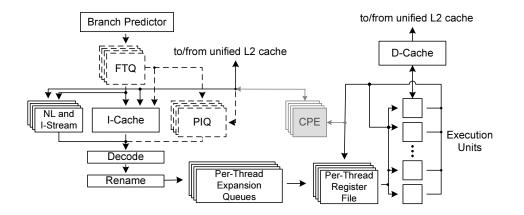

| 4.7 | Processor model (FTQ and PIQ for FDIP only, CPE for FSMR only)                               | 66 |

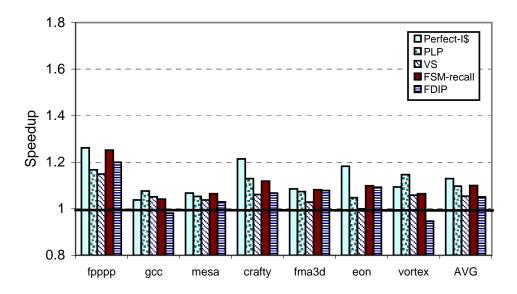

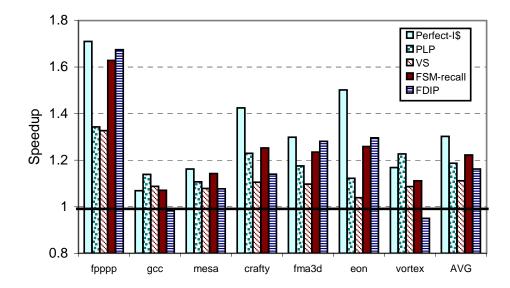

| 4.8  | Performance on $2x$ configuration $\ldots \ldots \ldots$ |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.9  | Performance on $4x$ configuration $\ldots \ldots \ldots$ |

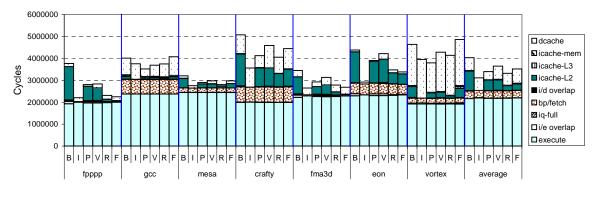

| 4.10 | Classification of execution cycles (4x memory configuration). $\ldots \ldots \ldots \ldots 72$                                                                           |

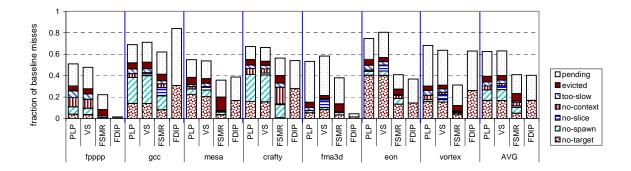

| 4.11 | Classification of remaining I-cache misses (4x memory configuration) $\ldots \ldots \ldots 72$                                                                           |

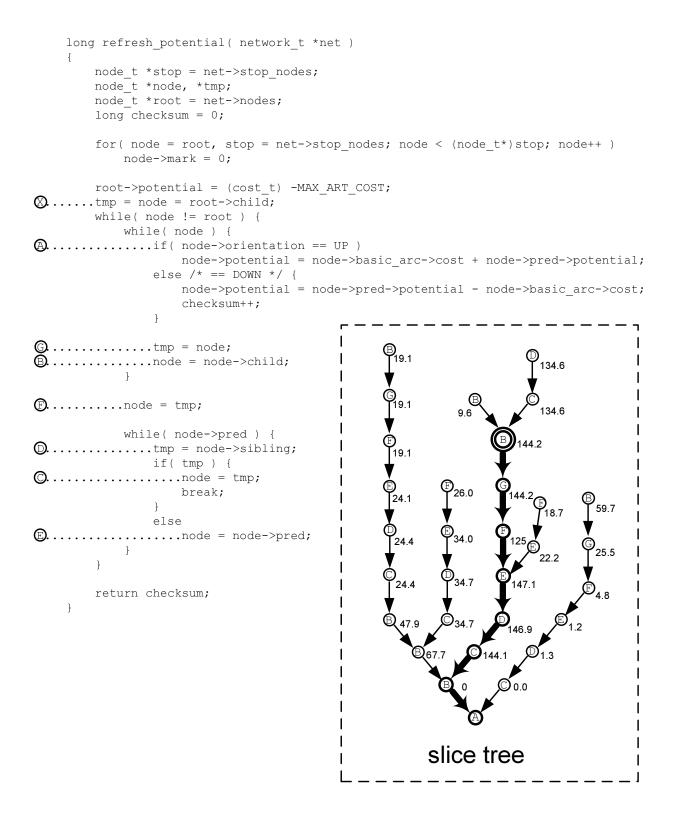

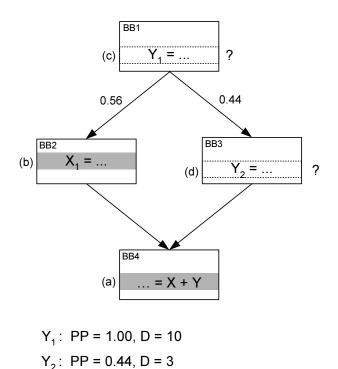

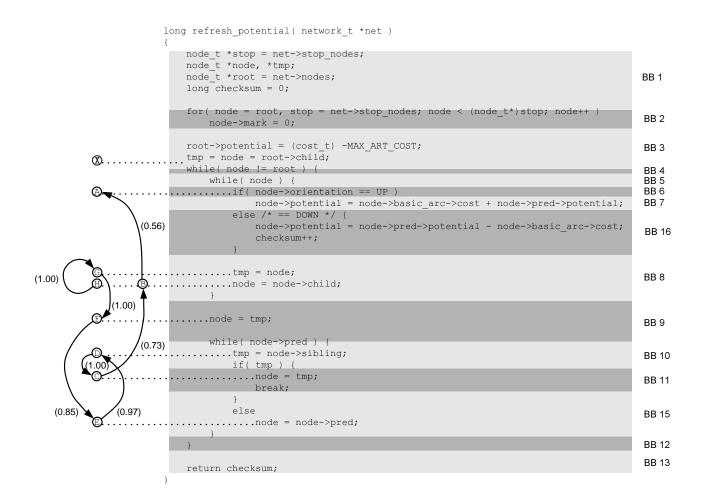

| 5.1  | Slice tree example for a delinquent load in 181.mcf                                                                                                                      |

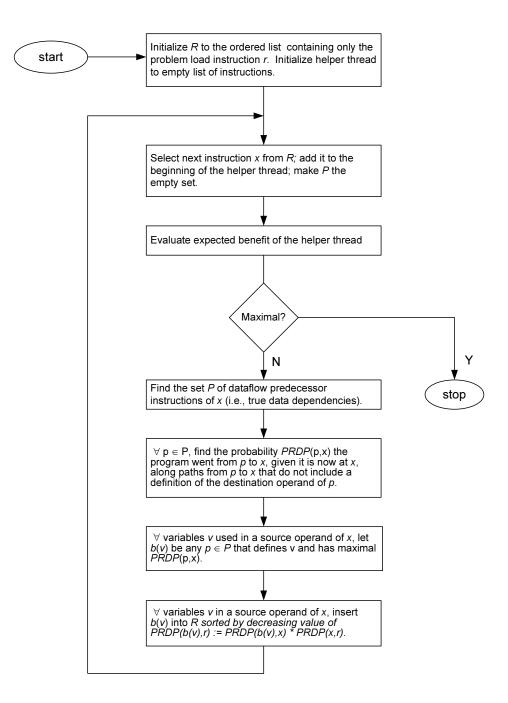

| 5.2  | Path expression p-thread optimization algorithm (PRDP definition on page $87)$ $$ $83$                                                                                   |

| 5.3  | Implied Control Flow                                                                                                                                                     |

| 5.4  | Example illustrating need for predecessor pruning during p-thread slicing $87$                                                                                           |

| 5.5  | Code excerpt from Figure 5.1 with basic blocks in the $gcc-2.6.3$ optimized, Sim-                                                                                        |

|      | pleScalar program binary                                                                                                                                                 |

| 5.6  | Control flow graph for code in Figures 5.1 and 5.5 showing branch transition prob-                                                                                       |

|      | abilities. $\ldots \ldots 90$                                          |

| 5.7  | Second-order control flow graph for code in Figures 5.1 and 5.5 93                                                                                                       |

| 5.8  | Initial version of the data prefetch slice enabling compiler infrastructure implement-                                                                                   |

|      | ing the techniques described in this chapter                                                                                                                             |

| 5.9  | Modified helper thread infrastructure used to evaluate the techniques described in                                                                                       |

|      | this chapter                                                                                                                                                             |

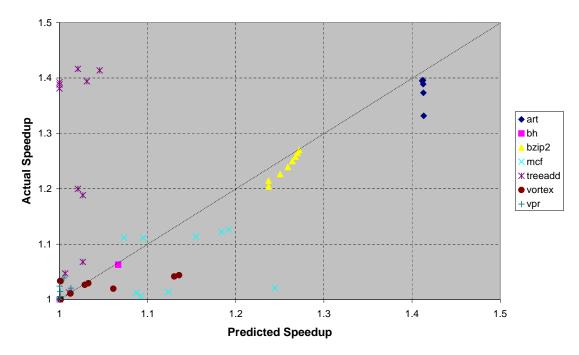

| 5.10 | Framework Accuracy for Predicting Benefit of Data Prefetch Helper Threads $\ . \ . \ . \ 100$                                                                            |

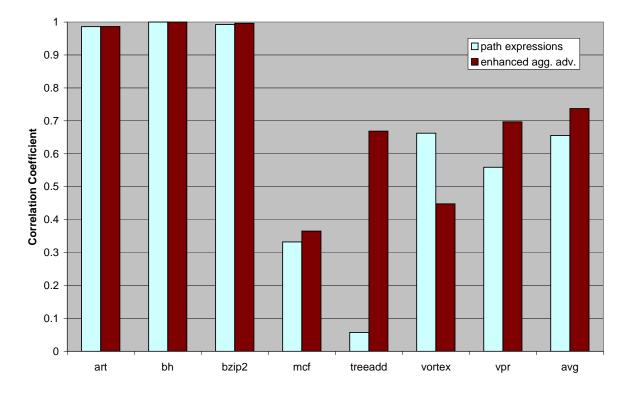

| 5.11 | Comparison of path expression based framework to aggregate advantage framework $101$                                                                                     |

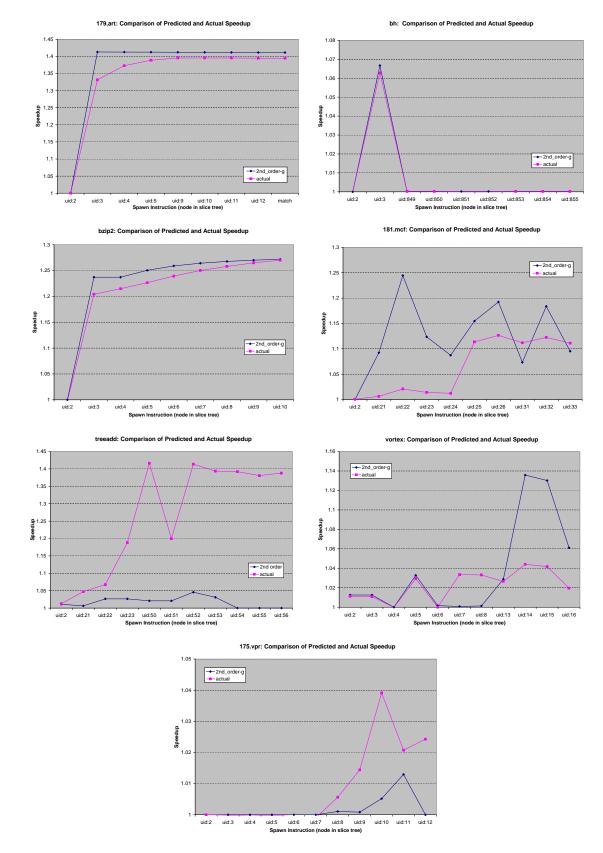

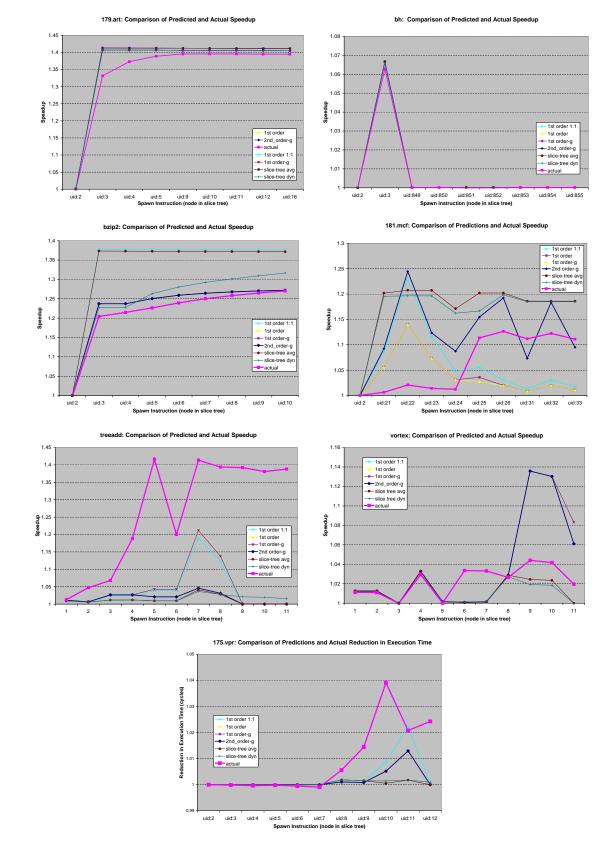

| 5.12 | Predicted and Actual Speedups with 32 Byte Data Cache Lines                                                                                                              |

| 5.13 | Prefetch Slack Sensitivity                                                                                                                                               |

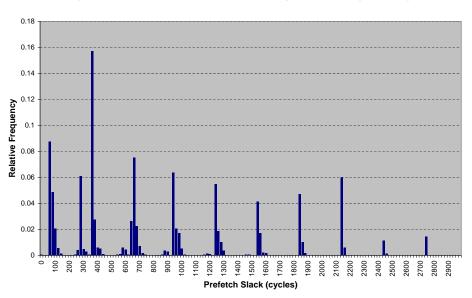

| 5.14 | Helper Thread Prefetch Slack Distribution for 175.vpr                                                                                                                    |

| 5.15 | Predicted and Actual Speedups with 32 Byte Data Cache Lines 109                                                                                                          |

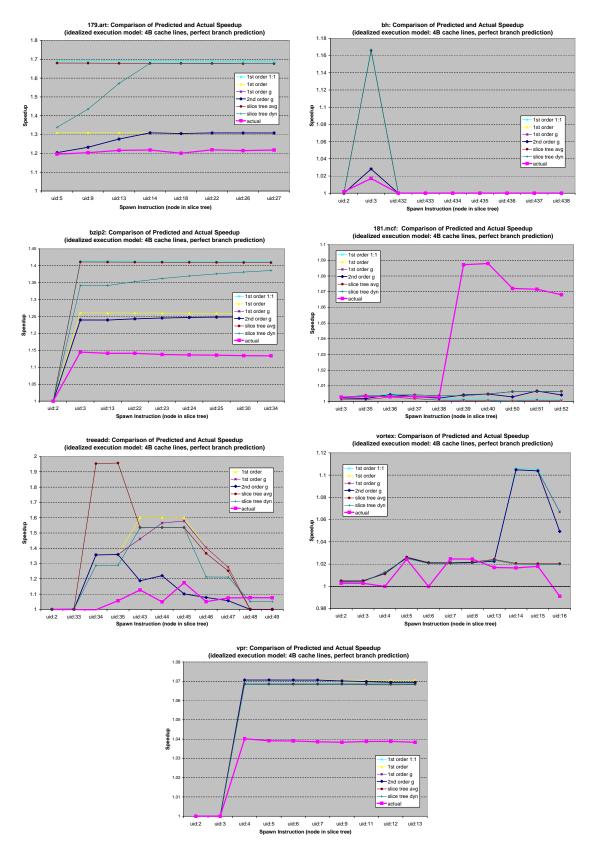

| 5.16 | Predicted and Actual Speedups with 4 Byte Data Cache Lines and Perfect Branch                                                                                            |

|      | Prediction                                                                                                                                                               |

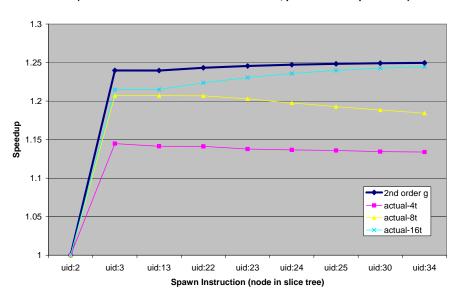

| 5.17 | Increasing Thread Resources for 256.bzip2 Reduces Prediction Error                                                                                                       |

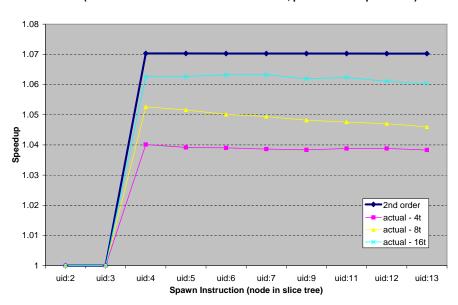

| 5.18 | Increasing Thread Resources for 175.vpr Reduces Prediction Error                                                                                                         |

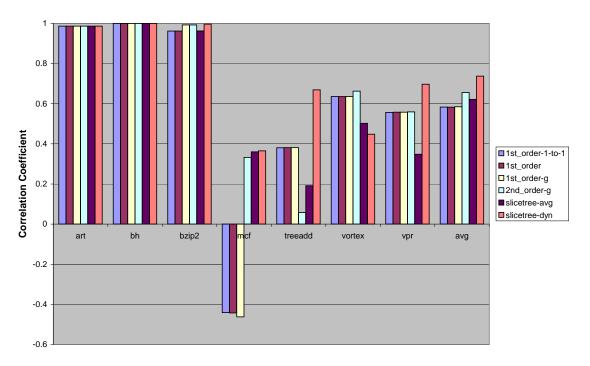

| 5.19 | Correlation of Predicted and Actual Speedups                                                                                                                             |

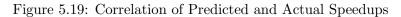

| 5.20 | Correlation of Predicted and Actual Speedups (4B data cache lines, perfect branch                                                                                        |

|      | prediction)                                                                                                                                                              |

# List of Tables

| 2.1 | Path Expression Mappings                                                               | 28 |

|-----|----------------------------------------------------------------------------------------|----|

| 3.1 | Spawn-Target Characteristics                                                           | 50 |

| 3.2 | Processor Resources                                                                    | 51 |

| 4.1 | Processor Configurations                                                               | 75 |

| 4.2 | Helper Thread Statistics                                                               | 76 |

| 5.1 | Comparison of static slicing with statistical control flow analysis using our path     |    |

|     | expression optimization metric in column (e) versus Roth and Sohi's aggregate          |    |

|     | advantage metric in column (h) and actual speedup in column (i). $\ldots$              | 91 |

| 5.2 | Comparison of static slicing with second-order statistical control flow analysis using |    |

|     | path expressions versus aggregate advantage                                            | 94 |

| 5.3 | Processor Configurations                                                               | 95 |

| 5.4 | Target Load Selection ("Sensitivity" listed in this table is defined in Section 5.5.1) | 99 |

## Chapter 1

## Introduction

This dissertation proposes and evaluates a novel framework for modeling the dynamic control flow behavior of computer programs, and applies this framework to modeling and optimizing the performance impact of speculative threads. Speculative threads are a promising approach to improving microprocessor performance on applications exhibiting complex control flow and/or memory access patterns. They improve performance by increasing the amount of useful computational work completed per clock cycle. The earliest research on speculative threads proposed dividing the computation of a single-threaded application into tasks that could be executed concurrently–a technique known variously as *Multiscalar* [SBV95], *thread-level speculation*, [SM98, SCZM00], or *speculative multithreading* [MGT98].

Recently, several forms of speculative *helper threads* have been proposed for reducing the impact of challenging microarchitectural performance bottlenecks in modern microprocessors that have resisted hardware only solutions. While speculative multithreading improves performance by overlapping the execution of instructions from distinct tasks, helper threads overlap memory accesses and/or precompute branch outcomes to reduce disruptions to the flow of instructions through the microprocessor. Instead of focusing on improved *instruction level parallelism* – the latter being the focus of earlier studies on thread-level speculation, helper threads that prefetch instructions or data can be viewed as a technique for enhancing *memory-level parallelism* [Gle98]. Memory level parallelism is enhanced when the latency of cache misses is overlapped with computation or other cache misses [CFA04].

This chapter describes the motivation and background for this dissertation, the methodology employed, the contributions this dissertation makes, and finally summarizes the dissertation's organization.

#### 1.1 Motivation

Microprocessors form the heart of today's computing systems. They range in size from relatively small embedded processors for signal processing applications such as anti-lock brakes, to the largest and most power-hungry microprocessors used in parallel computing systems for business and scientific computing. Improvements in microprocessor performance per unit cost lead directly to improvements in application responsiveness—i.e., the time it takes to finish a single task—and throughput—i.e., the number of independent tasks that can be completed per unit time. Just as significantly, these performance improvements also enable improvements in the quality of software applications by making the use of more sophisticated software features feasible. For example, increasing microprocessor performance has enabled the use of more sophisticated algorithms in applications such as word processors, which can use additional performance to add features such as speech recognition and background grammar/spell checking. While individual improvements in performance are incremental, the accumulated improvements have a dramatic effect on the use of computing by continually enabling applications that would not have been practical earlier. The recent emergence of cell phones with integrated *personal digital assistant* (PDA) and digital cameras is an example of a new application that has relied upon improvements in computing performance to meet the small form factor required for consumers to find such a device useful. Another recent example is the "iPod" music player from Apple Computer [Inc05].

Underlying the historical trend of increasing performance per unit cost are advances in semiconductor technology that have yielded exponential improvements in both transistor switching frequencies, and the number of transistors that can be integrated on a single chip (which now typically doubles every 18-20 months—a trend sometimes referred to as "Moore's Law" [Moo65]). Developing a microprocessor that makes the best use of the logic gates and wires of a given process technology to deliver maximum microprocessor performance is one of the primary goals of the field of computer architecture. While there are other goals of importance in designing a computing system—such as maintaining application compatibility with prior microprocessors, increasing memory capacity, reducing power consumption, improving fault tolerance, and supporting secure computing to protect digital content—performance (or performance per unit cost) has traditionally been, and continues to be one of the main factors considered when buying a computing system.

Performance can be quantified as the reciprocal of an application's total execution time. Execution time in turn can be expressed using the "iron law" of computer performance, which expresses total execution time as a product of the average number of clock cycles it takes to execute an instruction, the time it takes to complete one clock cycle, and the total number of instructions executed:

Execution Time =

$$(Cycles Per Instruction) \cdot (Cycle Time) \cdot (Total Instructions Executed)$$

This formula applies to any instruction set and implementation technology. In recent years it has become customery express the relationship as:

Execution Time =

$$\frac{\text{(Total Instructions Executed)}}{\text{(Instructions Per Cycle)} \cdot (\text{Clock Frequency})}$$

Where *instructions per cycle* (IPC) is used rather than CPI because modern microprocessors are designed to execute multiple instructions per cycle.

Reducing total instructions executed to improve performance is usually accomplished by careful instruction set design and through the use of an optimizing compiler. Increasing clock frequency is achieved by reducing semiconductor technology feature sizes. In any one process technology generation, detailed processor design considerations may significantly influence clock frequency (an excellent example of this is provided in Papworth et al.'s summary of the performance tuning effort for the Pentium Pro microprocessor from Intel Corporation [Pap96]). Even though the impact of such design decisions on cycle time is dwarfed by the exponential growth in clock frequency over many years and successive technology generations, these design decisions are very important to the competitiveness of any given product generation. Processor microarchitecture design impacts clock frequency by placing constraints on the number of gates connected back-to-back between pipeline latches. Typically it is possible to improve IPC by introducing a more complex hardware algorithm. However, such improvements in IPC may be offset by an increase the critical delay path from the output of one set of latches into the next by increasing the number of levels of back-to-back logic on the critical delay path. Historically, this has lead to a form of competition between microprocessor designs embracing a "speed demon" approach (focus on higher clock frequency), versus a "brainiac" approach (focus on higher IPC) [Gwe93].

This dissertation describes techniques for increasing the average number of instructions executed per clock cycle without impacting cycle time.

Two trends in contemporary microprocessor design motivate the techniques presented in this dissertation. The first is the growing availability of single-chip multithreaded hardware. This growth is spurred by an abundance of hardware resources with increasing transistor densities, along with the relative ease (in terms of design complexity and verification costs) of obtaining improved throughput by supporting additional concurrent threads on a single chip. The second, and more fundamental, is a trend towards increasingly significant performance losses due to cache misses and branch mispredictions. Traditionally, performance bottlenecks such as cache misses and branch mispredictions have been addressed by hardware and/or compiler optimization techniques. However, while these approaches have been very effective thus far, they do not completely eliminate some performance degrading events. The techniques explored in this dissertation build on recent efforts that help attack those performance degrading events that traditional techniques are unable to adequately cope with as semiconductor technology continues to scale.

#### 1.2 Background

This section provides a short introduction to the topic of microprocessor design at the microarchitecture level. At the top level of a microprocessor design is the *instruction set architecture* (ISA) interface between hardware and software. The programmer creates software using either a high-level language, which is transformed to machine code using a compiler, or by directly coding instructions at the assembly level. These instructions are executed by the processor and transform the program's inputs to its outputs in some useful way. To ensure software compatibility between successive generations of microprocessors, the ISA is held fixed (with the occasional addition of new instructions). To enhance performance, the hardware organization that implements the instruction set architecture may be varied. This hardware organization is called the microarchitecture of the processor.

The next section provides fundamental background on single-threaded, microarchitectures and can be skipped by the knowledgeable reader. Section 1.2.2 gives an overview of multi-threaded architectures and describes the terminology used in this dissertation.

#### 1.2.1 Fundamental Microarchitecture and Program Behavior

To enhance the impact of the microarchitecture on performance it is important to consider the behavior of "typical" programs. To obtain greater average application performance for a particular semiconductor technology generation, cycle time can be optimized while employing microarchitecture optimizations to extract instruction-level parallelism. *Instruction level parallelism* (ILP) refers to the amount of parallelism among the dynamic sequence of instructions in a single thread of control. While from the programmer's perspective a thread may *appear* to execute sequentially, one instruction at a time, in an order determined by the control flow constructs of the programming language, the hardware microarchitecture may in fact schedule multiple instructions to execute at the same time provided they are independent of each other.

Hardware optimizations used to dynamically extract ILP from software exploit regularities in the behavior of typical programs. What is "typical" tends to evolve over time and hence significant effort is devoted to gathering and refining collections of benchmark programs thought to be representative of programs that will run on future microprocessors. One such example is the SPEC benchmark suite, which has been updated roughly every four years [Sta]. Benchmark suites such as SPEC enable objective comparison of competing computer systems, and encourage microprocessor designers to optimize the performance for real programs. For many microarchitecture techniques used in modern microprocessors, programs can be written that defeat the optimization and actually slow down when the technique is employed. The key is that the behavior exhibited by such programs is *unlikely* in typical programs. In typical programs found in SPEC and other bencharks it has been observed that parallelism among instructions from different basic blocks, correlated branch outcomes, and locality in the sequence of memory addresses generated by the program are common. It has been shown that these particular features can be exploited by hardware structures that adaptively learn the relevant structure of a program and use this information to significantly improve performance. Below we briefly explore the general ways in which these and other features of program behavior are used in existing microprocessor designs. The techniques described later in this dissertation focus on exploiting regularity in the control flow paths executed by a program at a level of granularity not exploited by hardware-only microarchitecture techniques.

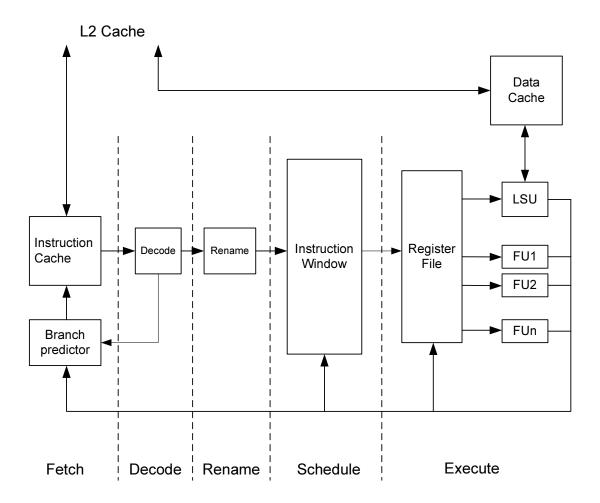

Figure 1.1 shows a block diagram of the microarchitecture of a typical current generation out-of-order superscalar microprocessor. Instruction execution is *pipelined* so that an instruction

Figure 1.1: Superscalar processor

may begin processing before the immediately preceding instructions in the instruction stream have finished processing. Each clock cycle, the fetch stage of the processor brings a new group of instructions into the pipeline from memory. The fetch stage includes a *branch predictor* and *branch target buffer* (BTB) that together attempt to guess the direction ("taken", or "not-taken") and target address of branches as they first enter the pipeline.

Once a set of instructions have been fetched, they are decoded to determine their impact on computation. Then the operands specified in the instruction are renamed and some information about the instruction is placed in an instruction reorder buffer.

*Register renaming* is a mechanism by which each definition of a programmer-visible architectural register (i.e., those registers specified in the ISA) that is encountered in the dynamic instruction stream is given a unique physical storage location. Renaming serves two important purposes: First, it exposes parallelism obscured when the limited number of registers available in a given instruction set architecture forces software to reuse registers. Without register renaming, the process of issuing instructions into execution units must wait whenever an instruction defines a register that may be used by an earlier instruction that has not completed execution. Second, register renaming provides a unique tag that may be used both to signal that the result of a computation is ready to be used by those instructions that depend upon it, and to route that result to the hardware units responsible for executing dependent instructions.

The *reorder buffer* is a FIFO queue used to support precise exceptions and to recover from branch mispredictions.

After register renaming, instructions are placed into an instruction scheduling window where they wait for their source operands to become ready so that they may be selected for execution (in some microarchitectures, the scheduling window also serves as the reorder-buffer). After instructions have completed execution they wait in the instruction window until all prior instructions have completed execution. Finally, instructions are retired from the processor in the same order they entered into the pipeline. This in-order retirement ensures both that the results and side-effects of speculatively executed instructions following a mispredicted branch are discarded without changing the architected program state, and also that the processor can stop when an exception is detected and later restart from the same location after the operating system has processed the exception as though no interruption had occurred. In-order retirement of instructions eliminates the need to stop and save the precise details of the entire pipeline state so that it can be restored later.

Pipelining improves performance by reducing cycle time while exploiting predictability in the control flow of a program and independence between the various stages of instruction processing to divide up the work of executing a single instruction over many cycles and partially overlap an instruction's execution with that of other instructions. For example, provided all instructions are encoded using the same number of bits, the fetching of an instruction can proceed in parallel with the decoding of the previous instruction. As long as the branch predictor is correct, the work done in parallel by the fetch and decode stages is useful. However, if the branch predictor makes a mistake, the fetched instructions are discarded and the opportunity to exploit this parallelism is lost.

The particular pipeline organization in Figure 1.1 is specialized to typical application behavior in several other respects. For example, the use of an instruction window and dynamic instruction scheduling improves performance by exploiting the parallelism typically found between nearby instructions in the dynamic instruction sequence of a program. This parallelism is an inherent property of the program itself, and the processor's ability to extract it is also related to the predictability of program control flow. Typically, in non-numeric applications, it is necessary to examine instructions from multiple basic blocks at the same time to find independent instructions to schedule for simultaneous execution. A *basic block* is a sequence of instructions that is executed as long as the first instruction in the sequence is executed (in other words, a basic block starts with an instruction that is the target of a branch or with the "fall-through" instruction immediately following a "not-taken" branch; it ends with the next branch instruction or the next occurance of an instruction that is immediately before the target instruction of some branch). Without executing a branch that terminates a basic block, it is not known with complete certainty what the subsequent basic block will be. Again, this control dependence is tackled by employing a branch predictor. Branch prediction relies on the fact that for typical programs, the outcome (direction and target address) of branch instructions tends to be correlated with the earlier behavior of the same branch and/or the behavior of other branches.

The processor interfaces to memory through caches that keep frequently accessed instructions and data in a small storage location with fast access times. The first-level cache is backed up by a second level, and sometimes third level of successively slower but larger caches that also maintain copies of instructions and data that are accessed less frequently than those resident in the first-level cache. Load and store instructions are placed in a structure called the load/store queue (also known as a memory order buffer) that schedules access to the memory hierarchy and ensures memory requests satisfy data dependencies through memory and the memory consistency model. Typically, first-level caches are *indexed* using the virtual address and *tagged* using the physical address provided by a translation lookaside buffer (TLB). Upon a first-level data cache miss, a request is sent to the next higher level of the memory hierarchy and, if the request is the result of a load instruction, any instruction that depends upon the value produced by the load must wait for this access to complete. The front-end of the processor accesses instructions in the instruction cache after consulting the branch predictor and BTB to index the cache, and the instruction TLB to perform the tag comparison to detect a hit or miss condition. Upon an instruction cache miss, the fetch unit stalls and instructions are no longer fed into the beginning of the pipeline while instructions already in the pipeline continue processing.

Caches exploit locality in the stream of memory addresses generated by typical programs. This locality exists because programs typically perform many operations on data before they are finished with it, and many algorithms involve looping through a sequence of instructions

View of Execution Stage:

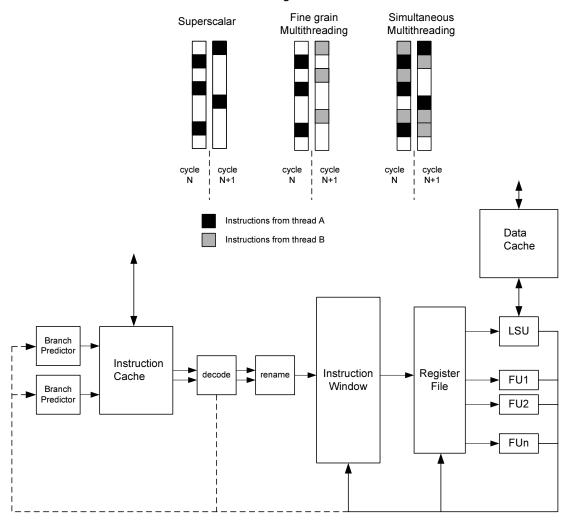

Figure 1.2: Superscalar processor with simultaneous multithreading support

repeatedly. However data and instruction cache misses still persist despite this locality. To improve the effectiveness of the memory hierarchy, modern processors employ a technique called prefetching. *Prefetching* is a process in which instructions or data are brought into the cache before the processor actually needs them.

#### 1.2.2 Multithreading Microarchitectures and Program Behavior

The basic superscalar design in Figure 1.1 can be extended to allow multiple threads of control, or instruction streams, to share most of the pipeline's hardware resources. This is called

simultaneous multithreading (SMT) and is illustrated in Figure 1.2. SMT has been implemented on Intel's Pentium 4 microprocessor under the brand name of 'Hyper Threading', and IBM has announced SMT support in the Power 5, which IBM has disclosed is also a single chip multiprocessor (CMP)—i.e., has multiple microprocessor cores on a single silicon die. The Alpha EV8 microprocessor (development of which was cancelled in 2001) was also designed with an SMT hardware organization [SFKS02]. In an SMT processor the hardware thread contexts on a single processor core typically share the first level of the cache hierarchy. If the threads running on these SMT thread contexts are unrelated, then instructions and data compete for space within the cache hierarchy, potentially leading to higher cache miss rates for both threads. The effect on job throughput is offset by the positive benefit of multiplexing work from both threads on the execution core. In particular, as the issue width of microprocessors are increasing at the same time that memory latencies are scaling up, it is getting more and more difficult to find ready instructions to schedule in a given cycle from a single thread despite the fact that instruction window sizes are also increasing. By allowing ready instructions from independent threads of computation to share execution resources these additional issue slots can be used. In the top portion of Figure 1.2 (labelled "View of Execution Stage"), the issuing of instructions to execution units each cycle is contrasted with normal superscalar, and fine grain multithreading (such as implemented on the Tera Computer System  $[ACC^+90]$ ). For example in Figure 1.2 the superscalar processor issues three instructions from thread 'A' on clock cycle 'N' and two instructions from thread 'A' on clock cycle 'N+1'. Fine grain multithreading increases throughput by allowing instructions from a different thread to be scheduled each clock cycle. In the example in Figure 1.2 on clock cycle 'N+1' the processor supporting fine grain multithreading issues three instructions from thread 'B' instead of the two instructions from thread 'A' thus increasing instruction throughput per cycle by one half over the superscalar design (for an improvement of 20%). Simultaneous multithreading allows a potentially far greater sharing of execution resources within a given cycle. In the example in Figure 1.2, the processor supporting SMT issues three instructions from thread 'A' and three instructions from thread 'B' on the first cycle and roughly doubles instruction throughput compared to the superscalar processor.

SMT allows hardware resources, such as instruction scheduling window entries and issue ports to be allocated dynamically to the thread that can make the best use of them, rather than statically partitioning resources among thread contexts. Of the two structures mentioned (instruction scheduling window entries and issue ports) the latter has been shown to be the more important hardware resource to dynamically partition for sharing among application threads [RR03]. On the other hand, the sharing of caches and branch predictor table entries can lead to destructive interference between concurrently running threads. One of the key hardware attributes enabling helper threads such as those studied in this dissertation to improve performance is the cache interaction between concurrently running threads on an SMT processor. The benefit of sharing space in the cache is that the helper thread can be designed to bring instructions and/or data into the caches just before the main thread requires them.

It has been observed [ZS00] that a small fraction of all static loads and branches are responsible for the majority of data cache misses and branch misprediction events that foil existing hardware techniques such as stride prefetching [PK94] and branch history based branch prediction mechanisms [Smi81, LS84, MH86, YP91]. The load address or branch outcome stream of these instructions does not show sufficient locality that predictions can be made based merely upon past behavior. Load instructions that exhibit this behavior have been described as *delinquent loads* [CWT<sup>+</sup>01].

Recently, proposals have been put forth to use multithreading resources to reduce the impact of such performance bottlenecks [DS98,  $CSK^+99$ ]. One of the earliest proposals included simulating larger branch history based predictors in software than can be built in hardware economically, augmented with sophisticated mechanisms for integrating the prediction results into the conventional superscalar pipeline [CSK<sup>+</sup>99]. Later studies suggested the alternative approach of isolating the subset of instructions that will produce the hard to predict outcome, called the computation *slice* [Wei81], and executing this slice of instructions early enough that the results can be used to eliminate or reduce the impact of the associated performance degrading events. Studies of the slices leading to branch mispredictions and cache misses have shown that these are both limited in size [ZS00], and contain significant locality in the sequence of operations contained within the slice from one instance to the next [AMC01]. Subsequent studies have demonstrated the effectiveness of these techniques under realistic implementation constraints [MPB01, CWT<sup>+</sup>01, CTWS01, ZS01, Luk01, APD01]. Recent work has begun to consider optimization of data prefetch helper threads [RS02, LWW<sup>+</sup>02] and the implementation of helper threads on real hardware systems [KLW<sup>+</sup>04, WCW<sup>+</sup>04].

#### 1.2.3 Helper Threads

A programmer seeking to reduce application runtime by exploiting multiprocessing hardware can manually partition an application into threads when developing the source code. In some cases this partitioning actually eases the software design process itself, for example by decoupling development of unrelated tasks, but often the goal is to improve performance of a single application. In the latter case, a careful consideration of dependencies within the program is required. When manual partitioning is successful it can lead to dramatic improvements in performance. As the process of parallelizing software and the required dependence analysis is well understood for certain application domains—primarily numerically intensive applications—support for automatic parallelization has been incorporated into some modern compilers.

However, there are many important applications for which it is difficult to achieve significant performance improvements by statically partitioning the computation into threads using existing techniques. To tackle the challenges posed by such applications, there has been extensive research on dynamic hardware-based program parallelization that has shown significant potential [SBV95, SM98, KT98, MGT98, AD98, MG02]. With the possible exception of SUN Microsystem's MAJC processor [TCC<sup>+</sup>00, Hal99], commercial microprocessors do not yet employ such techniques.

In contrast to the parallelization techniques described above, a *helper thread* performs computation that is run simultaneously with the application's *main* thread. The goal of the helper threads explored so far is to eliminate microarchitectural performance bottlenecks such as cache misses and branch mispredictions in the main thread.

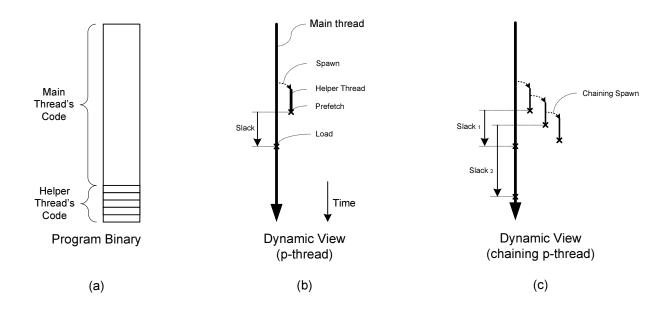

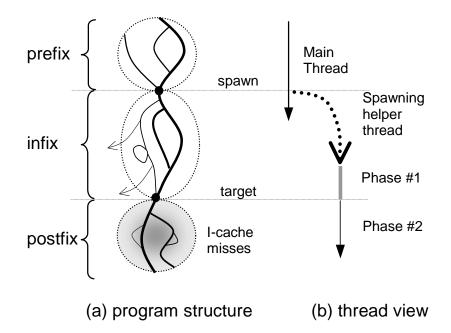

Figure 1.3 illustrates two types of helper threads that have been investigated previously  $[CWT^+01, ZS01, LWW^+02]$ . Figure 1.3(a) shows a static view of the program and highlights the location of helper thread instructions relative to the main thread's instructions in the binary image. When the program executes, helper threads are invoked if the main thread reaches a spawn instruction and there are thread contexts available—see Figure 1.3(b). When a helper thread is spawned the registers in the spare thread context are initialized to the corresponding values in the main thread. The spawn instruction then initializes the program counter of the spare thread context and activates it causing the helper thread to run. In this dissertation the hardware model includes a native spawn instruction that executes in a single cycle. While dedicated hardware support for such spawn instructions has not been announced in any commercial processor thus far, recent studies have shown that microcode implementations of closely related spawn instruction

Part (a) illustrates a modified program in which helper thread code has been attached to the program binary. In part (b) the thick arrow represents the dynamic instruction stream of the main thread and the shorter thick line represents the dynamic instruction stream of a simple helper thread that generates a single data prefetch. Part (c) illustrates a 'chaining' helper thread that spawns another helper thread in addition to generating a data prefetch.

functionality incurring multiple clock cycles of latency [KLW<sup>+</sup>04, WCW<sup>+</sup>04], combined with appropriate helper threads, can yield significant benefit on real applications even on systems composed of single core processors running a multithreaded workload [WCW<sup>+</sup>04]. Referring again to Figure 1.3, the helper thread exits when it executes a special thread exit instruction.

As illustrated in Figure 1.3(c), a *chaining* helper thread contains a spawn instruction that triggers the creation of a new helper thread. Typically, the spawn instruction is assumed to trigger a new invocation of the same thread code containing the spawn. This form of chaining helper thread has been shown to be effective for tackling data cache misses inside of loops. Chaining improves performance by increasing both the number of helper thread instructions executed in parallel (ILP) and the number of outstanding prefetches accessing the memory system (MLP). On in-order machines, it may also help to prevent a cache miss triggered in one helper thread invocation from stalling the execution of a future helper thread invocation.

While each helper thread instance runs for a short duration of time, there will be many helper

thread instances during the runtime of an application and hence helper threads may consume valuable execution resources that potentially could have been used for other purposes. Furthermore, the effectiveness of each helper thread is based on how well its computation anticipates future performance degrading events in the main thread.

#### 1.2.4 Program Behavior Exploited by Helper Threads

There are several factors that govern the performance impact of helper threads. These include the microarchitecture behavior of the helper thread's code upon the helper thread's own execution (i.e., "ignoring" the existence of the main thread), the resources available to run helper threads, and the relationship of the helper thread's behavior relative to the behavior of the main thread.

An important property of the helper thread's execution is the number of instructions that must be executed to generate each prefetch. An important resource is the number of spare thread contexts available to run helper threads. However, it is the relationship of the helper thread's behavior relative to the behavior of the main thread that determines whether a prefetch or branch prediction is timely and necessary. This relationship can be quantified in several ways which will be described in Chapter 2.

The main contribution of this dissertation is a novel framework for modeling the impact of speculative threads used to improve microprocessor performance. While prior work has examined the impact of data dependencies on speculative threads [RS02, LWW<sup>+</sup>02, ZCSM02, ZCSM04], the novel aspect of this new framework is its focus on statistically quantifying the impact of control flow on the impact of speculative threads. While knowledge of data dependencies is critical to identifying parallel sub-computation, state-of-the-art microprocessors follow a single path of control flow that inherently limits the rate at which instructions can pass through a finite window, dataflow-driven, out-of-order execution core. Hence, at a higher level of granularity than the number of instructions that can fit within a modern processor's scheduling window, control flow determines how long it takes for program execution to get from one place to another, as well as how likely that event is to take place. This scale also defines the typical scale, in terms of numbers of dynamic instructions, of speculative threads. Thus, to model the impact of speculative threads it is beneficial to study ways of modeling control flow variation.

As already noted, the correlation between individual branch outcomes—a form of control flow behavior—is already exploited by modern branch predictors. The aspects of control flow this dissertation focuses on extend beyond individual branch outcomes to the control flow structure of the program. In particular, this work considers the statistics of program paths weighted by their frequency of occurrence and uses this information to model the impact of speculative threads. Prior work by Marcuello and Gonzalez noted the potential to use one such aspect—the notion of reaching probability—for improving the performance of speculative multithreading [MG02]. This dissertation takes this notion as a starting point, and advances beyond it by developing a unified theoretical framework incorporating many other important statistical quantities, shows how these quantities can be evaluated efficiently using path expressions, and then applies this novel framework to the optimization of helper threads.

To evaluate the overall framework, it is applied to optimizing the selection of two types of helper threads. The framework proposed in this paper helps estimate helper thread performance impact in a manner compatible with the generation of helper thread code within a standard profile driven optimizing compiler.

While the framework naturally fits in the context of profile-driven compiler optimization, the notion of quantifying the impact of speculative threads to optimize their selection is not inherently limited to this setting. For instance, it may be feasible to implement this type of analysis and optimization methodology in hardware or in a dynamic compilation framework within a runtime system. The advantage of such a system is that it could be used to adapt helper threads to changes in program behavior.

#### 1.3 Dissertation Summary

This section gives an overview of this dissertation, outlining its goals, methodology, contributions and organization.

#### 1.3.1 Research Goals

The primary objective of this research was the development and detailed evaluation of novel techniques for improving the performance impact of speculative threads. The impact of speculative threads can be enhanced by optimizing the selection and composition of the speculative threads themselves. To do so it is desirable to have an accurate framework for quickly estimating without the use of detailed simulation—the impact of tradeoffs in the construction of speculative threads. Such tradeoffs exist, for example, because there are a limited number of thread contexts that must be shared by application main threads and speculative threads, and speculative threads consume execution resources that could also be applied to directly execute instructions from one of the main threads.

A secondary objective was the development and detailed evaluation of novel implementation techniques and hardware support mechanisms both to facilitate the optimization process and to enhance the impact of the resulting speculative threads. For practical reasons the scope of inquiry is limited to speculative helper threads for instruction and data prefetch.

#### 1.3.2 Methodology

The simulation results presented in Chapters 2 to 4 were collected using a simulator based upon SMTSIM [Tul96] extended to run the Intel Itanium® instruction set. Data in these chapters was collected while the author was on an internship with the Microarchitecture Research Lab of Intel Corporation in Santa Clara. This SMTSIM-based simulator is a highly detailed execution driven timing simulator that models an in-order Itanium processor with similar hardware organization to the Itanium 2 from Intel Corporation. Simultaneous multithreading is modeled by assuming instructions from multiple thread contexts can issue in-order to a set of shared function units. Instruction fetching is restricted to bring in instructions from at most two threads in any cycle, independent of how many thread contexts are supported. Memory latencies and pipeline depths are increased in the simulator model to be representative of a future generation processor operating at a higher clock frequency. Additional details of this simulation infrastructure are described later on in the dissertation along with descriptions of the techniques developed in this dissertation.

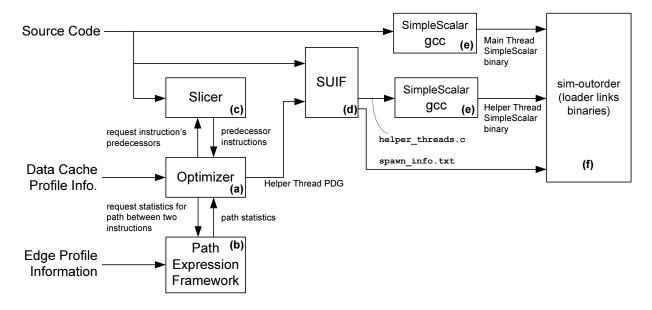

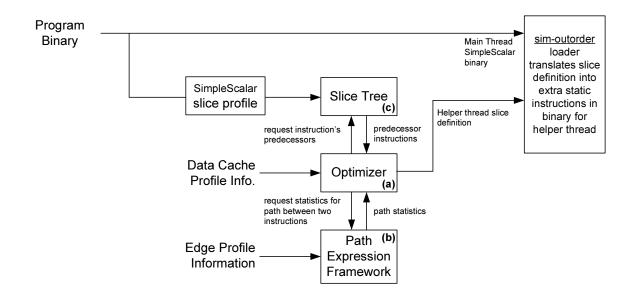

The simulation results presented in Chapter 5 are based upon a modified version of SimpleScalar [BA97] that supports SMT and some of the new hardware mechanisms discussed later in this dissertation. As well, a compiler pass was developed that couples an implementation of the modeling framework in Chapter 2 with the CodeSurfer program slicing tool (licensed for academic use) via the latter's Win32 DLL API and via textfiles with the SUIF compiler infrastructure [HAA<sup>+</sup>96]. The output produced by this combination is ANSI C that is then compiled using the SimpleScalar compiler for the PISA instruction set. Additional details are described in Chapter 5.

#### 1.3.3 Contributions

This dissertation makes the following contributions:

- It proposes and evaluates a novel control flow modeling framework that accurately predicts the following statistical quantities between two static instructions within an application thread: (a) the reaching probability, (b) the posteriori probability, (c) the mean path length, (d) the path length variance, and (e) the path instruction footprint.

- 2. It evaluates this framework on the task of optimizing the use of helper threads for prescient instruction prefetch. A simple "greedy" algorithm is employed along with a heuristic function that quantifies the expected impact of a particular helper thread selection on performance.

- 3. It proposes and evaluates two implementation techniques for realistically enabling instruction prefetch helper threads: *Direct Pre-execution* and *Finite State Machine Recall*.

- 4. It proposes and evaluates a hardware mechanism, the *YAT-bit*, for filtering the instructions executed during Direct Pre-execution.

- 5. It extends and evaluates a proposal for supporting store instructions in speculative threads called the *safe-store*.

- 6. It proposes and evaluates a way of using counted instruction prefetch operations to reduce the resource consumption of helper threads.

- 7. Finally, it proposes extensions to the framework to enable it to optimize the use of helper threads for data prefetch.

#### 1.3.4 Organization

The rest of this thesis is organized as follows: Chapter 2 introduces a rigorous framework for modeling speculative threads. Chapter 3 describes how to apply this framework to optimize prescient instruction prefetch helper threads. Chapter 4 describes hardware support mechanisms and implementation techniques for implementing prescient instruction prefetch helper threads. Chapter 5 describes the application of the modeling framework to the optimization of data prefetch helper threads. Chapter 6 describes related work, and Chapter 7 concludes. Appendix A documents two of the longer derivations that underlie the contributions made in Chapter 2.

### Chapter 2

## **Modeling Framework**

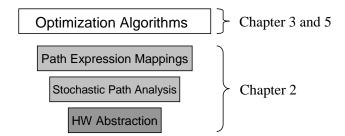

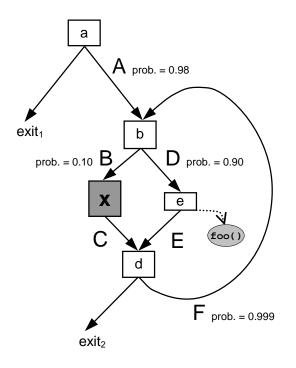

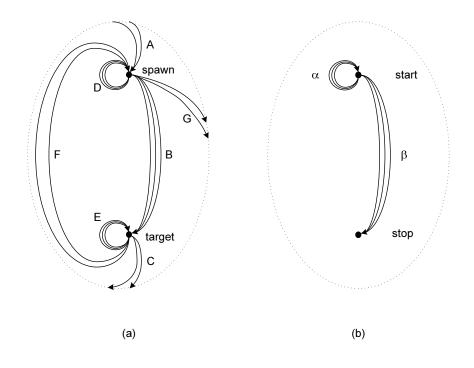

In this chapter we describe the modeling framework developed for this dissertation. Building on this foundation, an optimization algorithm for generating instruction prefetch helper threads is presented in Chapter 3, and similarly, an optimization algorithm for generating data prefetch helper threads is presented in Chapter 5. This framework is designed to model short term variations in control flow that exist within a program phase, over periods longer than represented by the number of instructions in-flight within a microprocessor. A high-level view of the framework is shown in Figure 2.1. This framework is applicable within a profile-guided optimizing compiler that augments an application with helper thread code and enables the application to launch these helper threads on a microprocessor with appropriate hardware support.

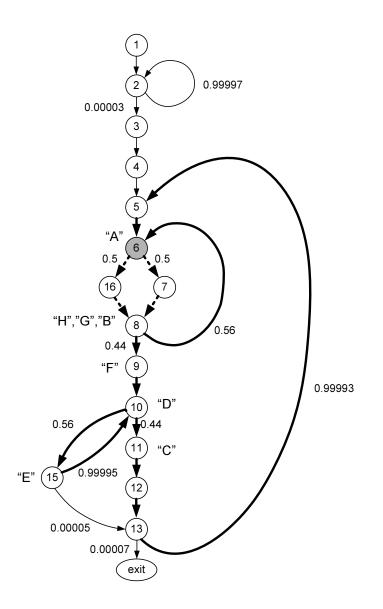

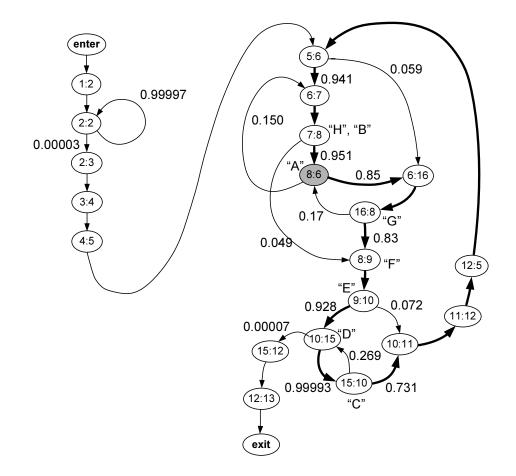

Figure 2.1: Modeling and Optimization Framework

The rest of this chapter is organized as follows: In Section 2.1 we define a generic speculative thread, and then consider a specific example from which we abstract key properties impacting the performance of speculative threads. This abstraction captures important properties of several types of helper thread as well as some important aspects of speculative multithreading. Then

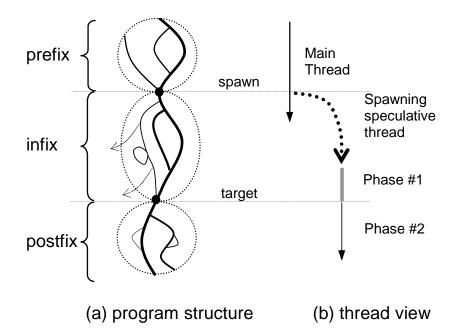

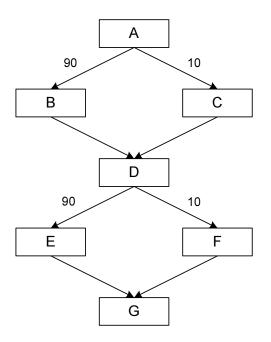

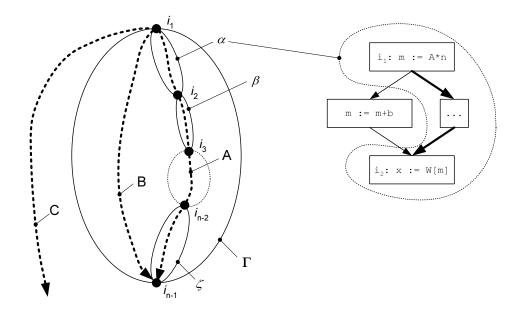

Part (a) shows a control-flow graph with spawn and target points highlighted. It is known *a priori* that having the speculative thread mimic the behavior of the main thread in the region labeled postfix is beneficial to performance. Part (b) illustrates two phases of speculative thread execution: Phase #1 live-in precomputation; Phase #2 postfix precomputation and generation some form of "results" for main thread. Note that distance along the vertical axis in Part (b) corresponds to the number of dynamic instructions executed by the main thread (i.e., it does not directly measure time).

#### Figure 2.2: Speculative Threads.

we consider several metrics for quantifying these properties. In Section 2.2 we show how to compute these metrics by considering the set of all control flow paths between two instructions within a program. In Section 2.3 we provide some experimental evidence showing how accurately the framework models the properties. Finally, Section 2.4 summarizes the contributions of this chapter.

#### 2.1 Generic Properties of Speculative Threads

The objective of a speculative thread modeled by the framework set forth in this dissertation is to "mimic" the behavior of the main thread in some, as yet unspecified way (the examples that will be considered later relate to instruction and data prefetch). For concreteness, we consider a generic speculative thread to consist of five components: a prefix region in the main thread, a spawn point in the main thread, an infix precomputation slice, a target point, and a postfix region. These are illustrated in Figure 2.2, and described below.

- 1. The *spawn point* indicates the location within the main thread at which the speculative thread is launched. The spawn point may be encoded in the program binary as a special "spawn instruction", or it may simply be a program address recognized by the hardware using some other mechanism. Regardless of how it is implemented, the action taken upon reaching the spawn point is to attempt to start a new speculative thread.

- 2. The *target point* indicates the starting location within the main thread that the speculative thread mimics.

- 3. The *postfix region* are the instructions following the target that the speculative thread mimics.

- 4. The *infix precomputation slice* are the instructions between the spawn and the target that must be executed by the speculative thread to accurately mimic the behavior of the inputs to the postfix region. It may be possible to partially predict the result of the infix precomputation slice using hardware mechanisms such as value prediction [LS96].